PCB设计,既是科学也是艺术。其中有非常多关于布线线宽、布线叠层、原理图等等相关的技术规范,但当你涉及到PCB设计中具有艺术特质元器件布局问题时,问题就变得有趣起来了。

事实上,关于元器件摆放限制很少,也没有“绝对正确”的规范要求,这也使得初学者电子工程师在摆布电路板上元器件时,就像个十足的“中二”,向往着个人抱负和创造性,如何摆放完全依赖于你和设计思路。

但这并不意味着你可以为所欲为,计算机中的设计最终还是需要降落凡尘,形成具体可用之物,因此下面十条PCB元器件摆放小建议可以指导电子初学者完成平稳走过电子设计初始阶段。

为什么元器件摆放那么重要?

有一句老话(不知谁说的)PCB设计90%在器件布局,10%在布线,这的确是一句大实话。开始费尽心思精细摆放器件可以起到事半功倍的效果,也可以提高PCB的电气特性。如果你只是将元器件随意任性在电路板上胡乱摆放,那会发生什么?

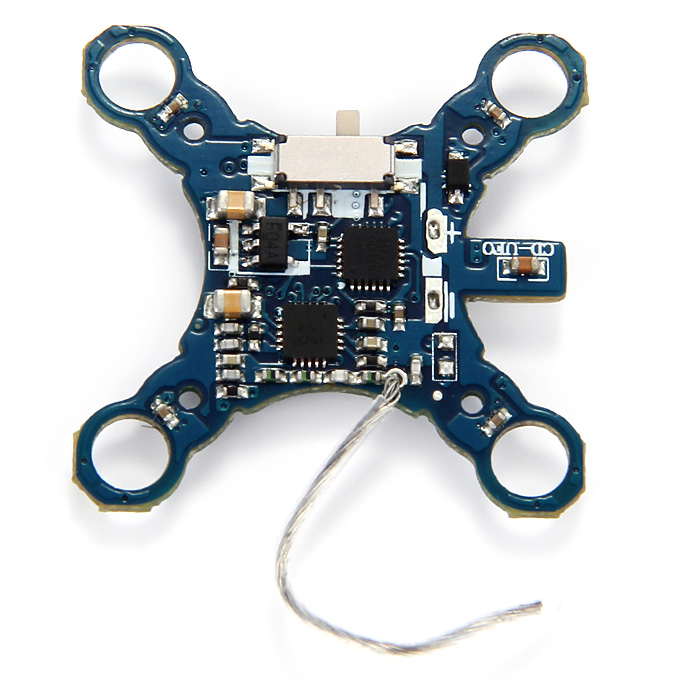

-

时间被打水漂:很大可能性你在布线的过程中就发现有些地方根本没有足够空间走线,甚至整个布线需要推倒重来。

-

电路板不工作:你本以为将器件放置好,并将所有的引线布完就万事大吉了。将设计文件发送给电路板制造商,等几天接到崭新的电路板。正准备兴高采烈焊接电路的时候就被现实猛烈打脸,发现有些器件根本无法焊接(要么封装不对,要么相互有冲突)。

-

美学碎了一地:我们必须承认,即使我们只是谦卑的工程师,在对美学的追求上还是认同对称、细致。那种一开始被缺少爱和不走心的人进行元器件摆放的电路板,在后期焊接和调试过程会给让人感到更加的堵心,涌入眼帘的只有葛优瘫。

如果你碰上一个杠精,会跟你辩论,元器件的摆放哪里什么条条框框,同一个电路图,100个电子工程师会有1000种布线方案。这也就是为什么说设计电路板更多被看成是艺术创作过程。

如果你遇事总想弄清对和错,下面倒是有一个小技巧帮你判断是否你的电路板元器件摆放是否合适。在器件摆放完之后,使用电路板设计软件中的自动布线(比如 Autodesk EAGLE中提供的)进行布线,如果最终电路不通率低于85%,这就说明你需要多花些时间优化元器件的摆放了。

下面就让我们少“逼逼”,多说些关于器件摆放的干货吧。

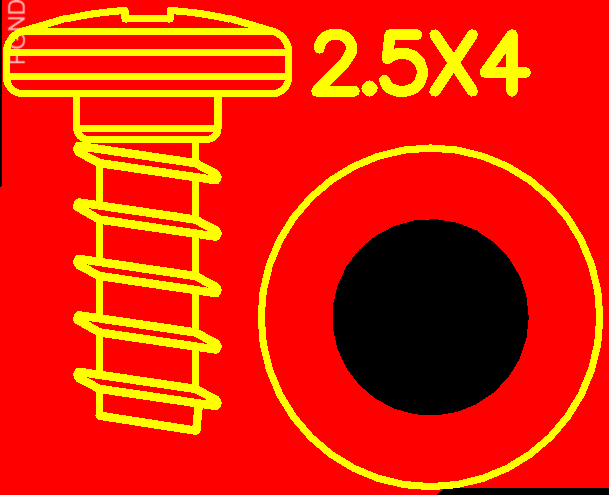

技巧1:弄清电路板物理限制

摆放元器件之前,首先需要确切知道电路板的安装孔、边缘接插件的位置以及电路板的机械尺寸限制。为啥呀?

因为这些因素影响你的电路板的尺寸和外形。曾见过某位设计的电路板无法装进电路板固定区域,只好重新设计。

为了避免犯傻,可以有意对那些机械限制(安装孔、电路外轮廓)设置一个清空区,这样你就可以放心在允许范围内进行创作了。

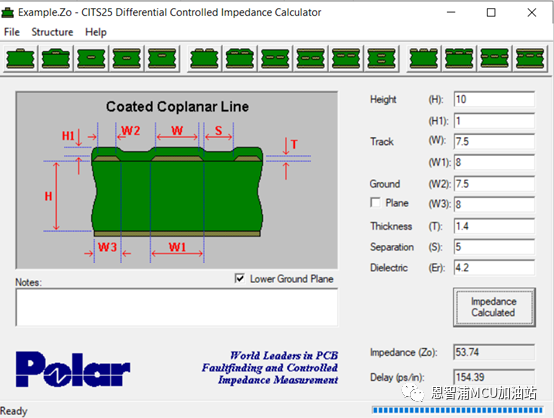

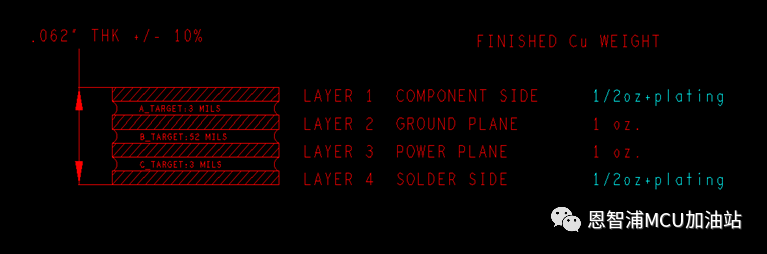

技巧2:弄清电路板制作工艺

同样,在放置电路元器件之前,你最好从电路生产商那儿弄清几个关键信息:

- 电路的组装工艺和测试流程;

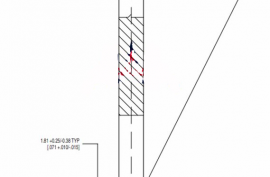

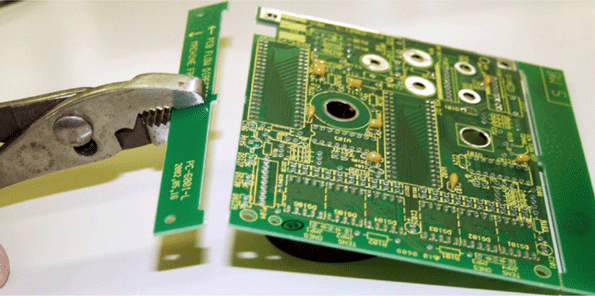

- 是否需要对PCB V型切槽预留空间;

- 元器件焊接工艺:是波峰焊、分区焊接还是手工焊接?

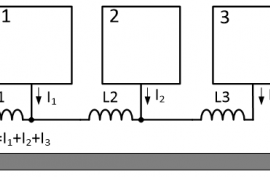

电路板制作工艺将会影响元器件之间空隙大小需求。还有,如果你的电路板将来会在流水线上被焊接,你就需要在电路板边缘额外留出空间(大于20mil)用于电路板固定在传送带上。电路板上额外的固定板,它在电路板焊接完之后被掰掉。

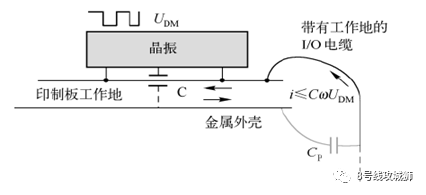

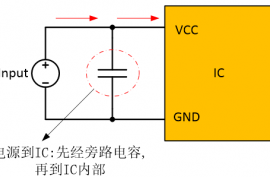

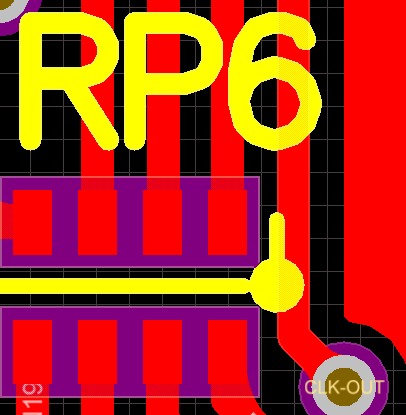

技巧3:给集成芯片留下喘气空间

注意,这里所说的“喘气”不是空气,至于是什么,看完下面你就清楚了 。在布置任何元器件的时候,都需要尽可能在它们之间留下至少350mil的距离,对于引脚多的芯片,留的空间需要更大。为何?

现在的芯片引脚原来越多,越来越密。如果集成芯片相距过于亲密,就会有很大可能无法将它们的引线轻松的引出布线。往往是越到后来布线越难,有的时候费心布通一根线就要消耗掉你100根头发,甚至到了叫天天不应,叫地地不灵的困境。(早知如此,何必当初)

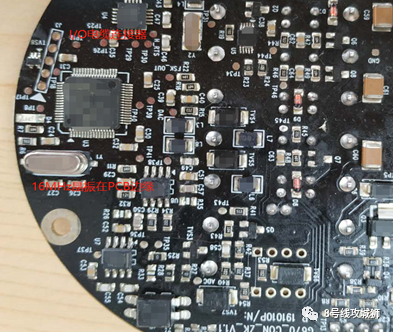

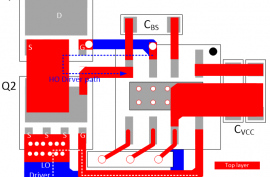

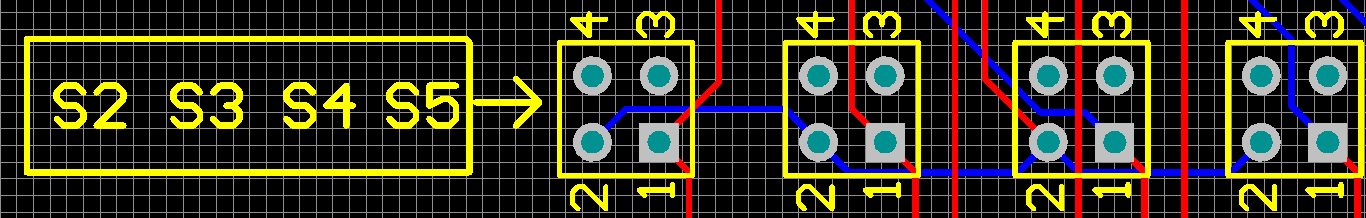

技巧4:相同器件方向一致

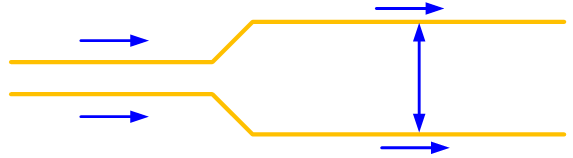

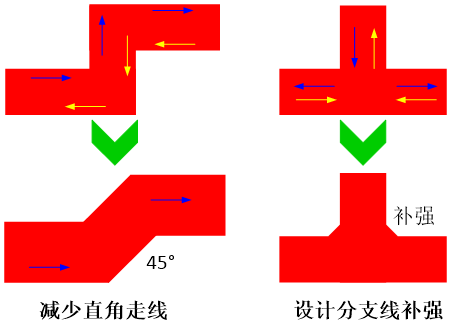

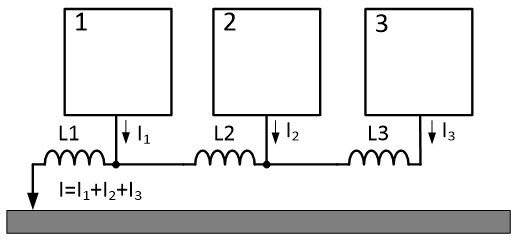

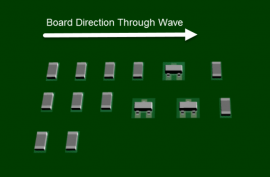

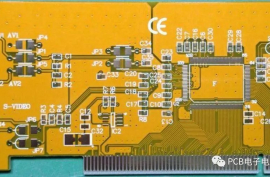

对于相同的器件尽可能让他们排好队,保持一致的队形。你有强迫症?这样做主要为了便于后期电路板的组装、检查和测试,尤其对表面封装的器件在波峰焊接过程中,电路板匀速经过融化焊锡波峰。均匀摆放的器件加热过程均匀,可以保证焊点一致性高。

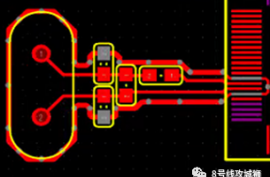

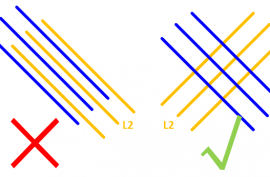

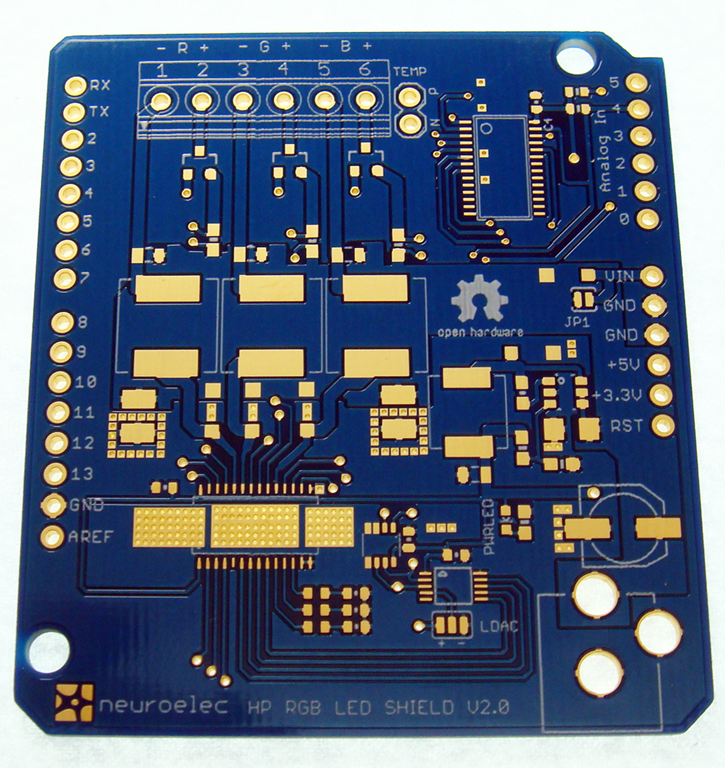

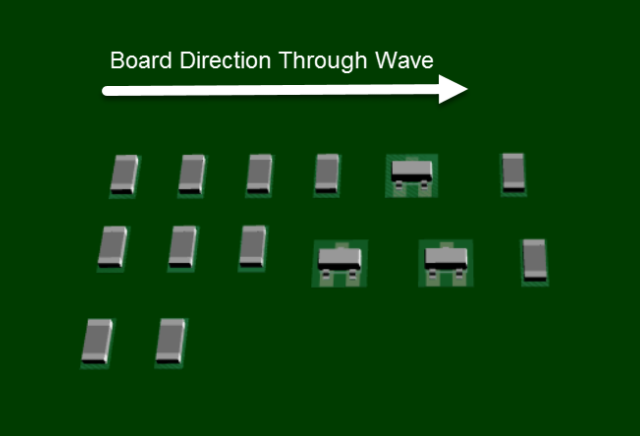

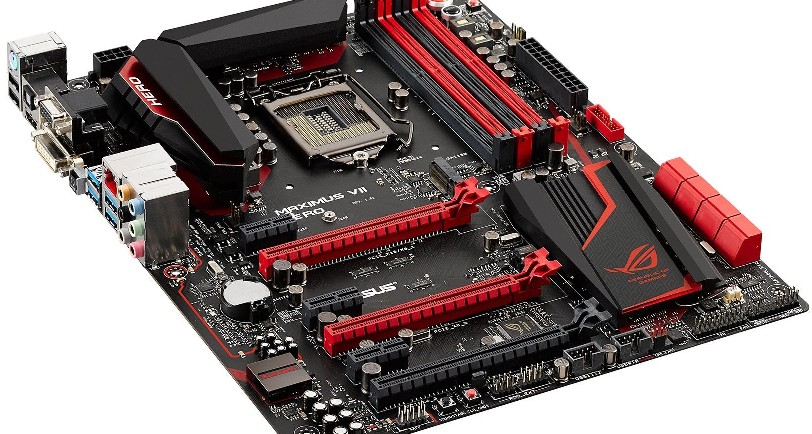

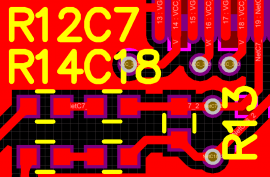

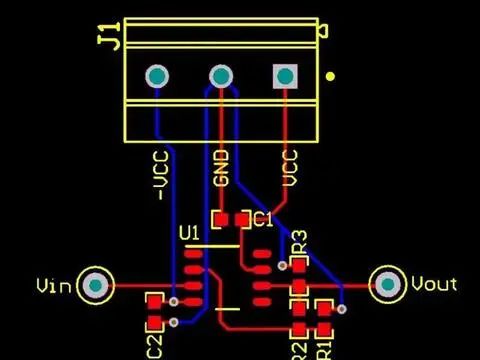

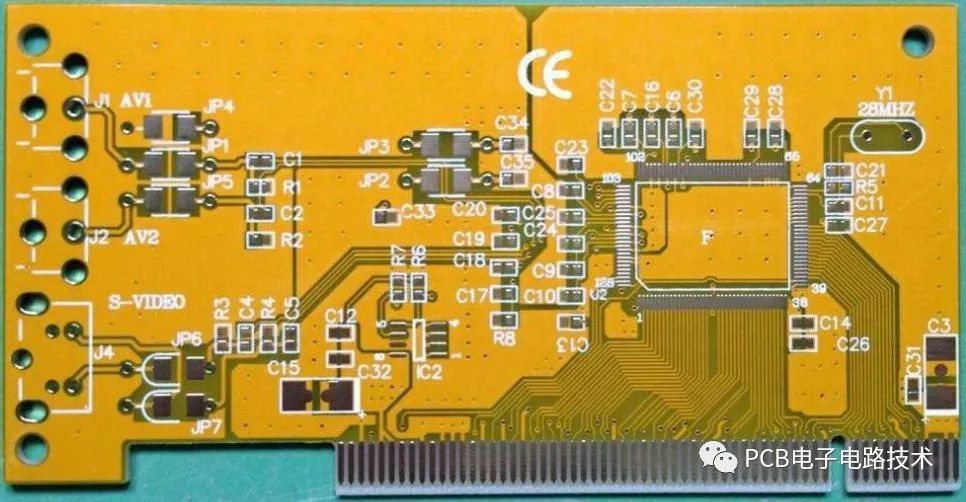

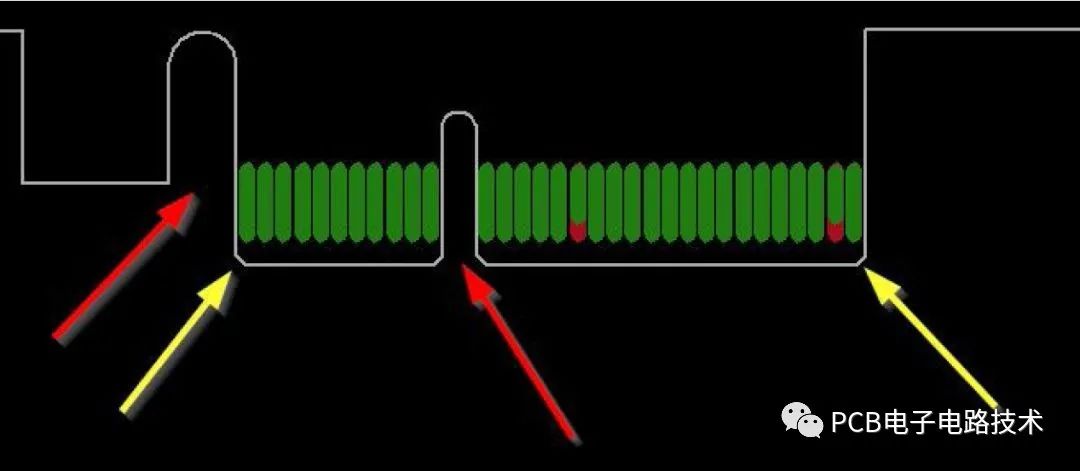

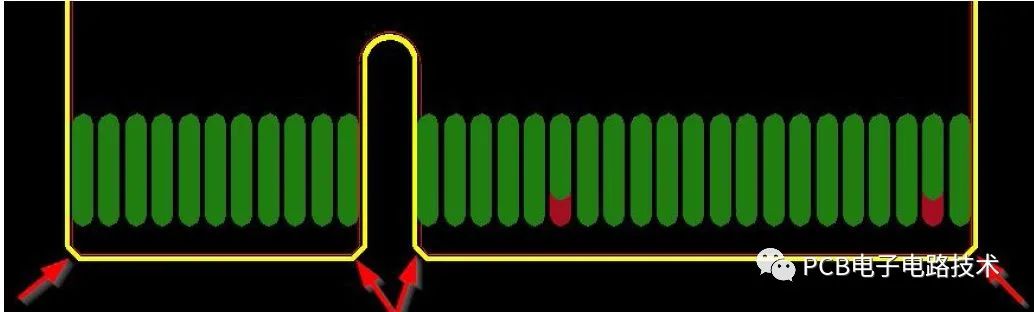

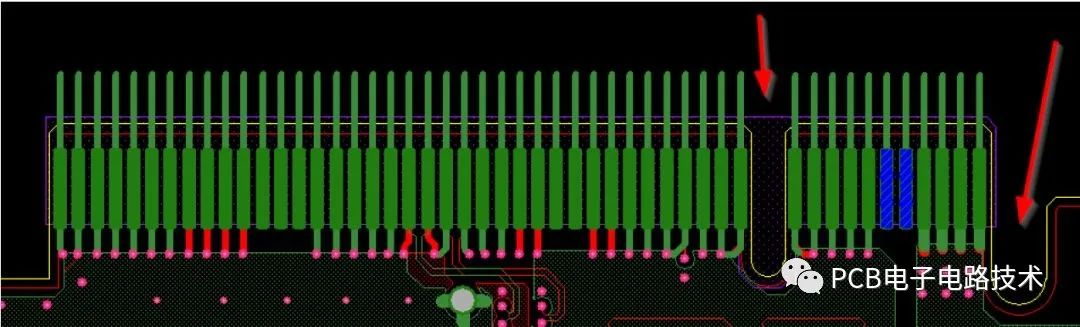

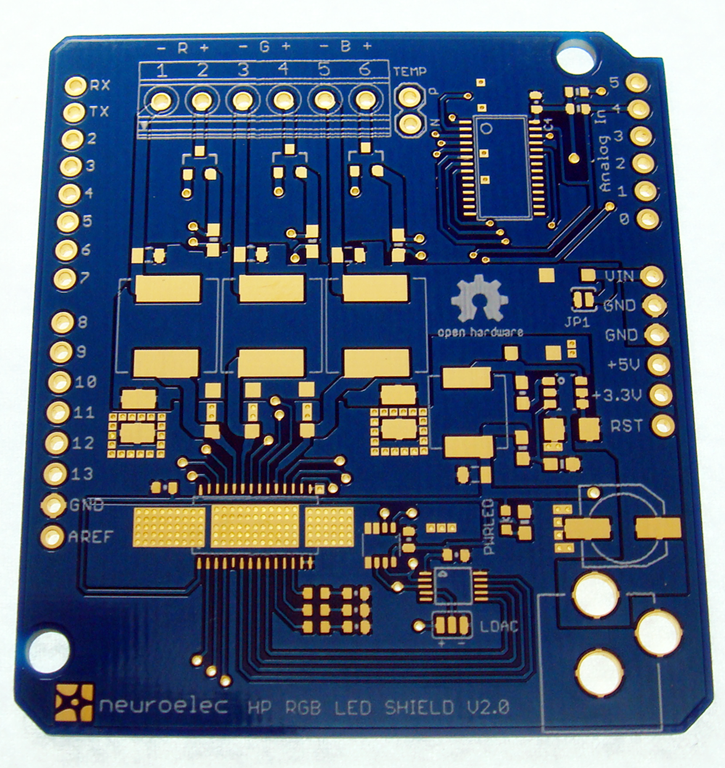

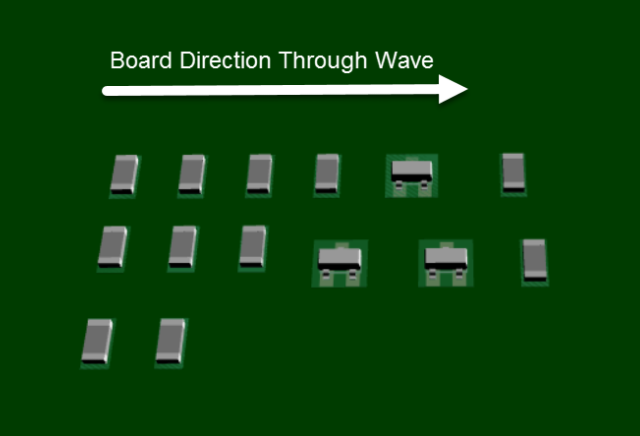

下面这个例子显示了均匀摆放器件适合匀速波峰焊接工艺。

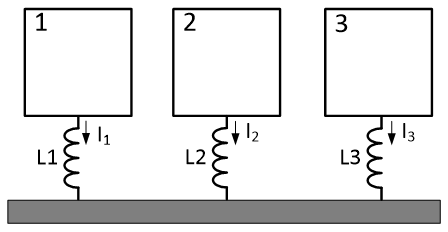

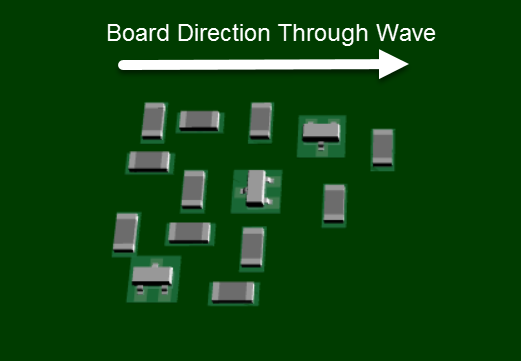

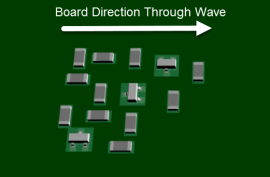

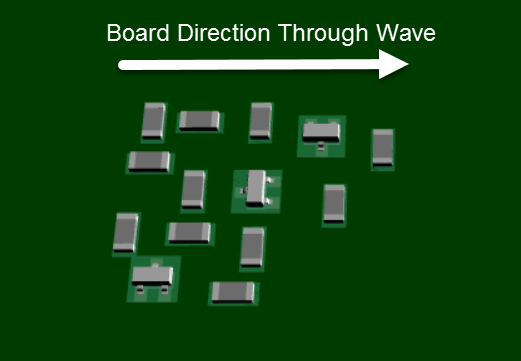

如果按照下面这样凌乱的摆放,波峰焊接对于不同器件的焊盘质量会有差异,特别当有些小型器件恰好位于大型器件之间时,就会形成“阴影”效应,小器件可能就会焊接不良。

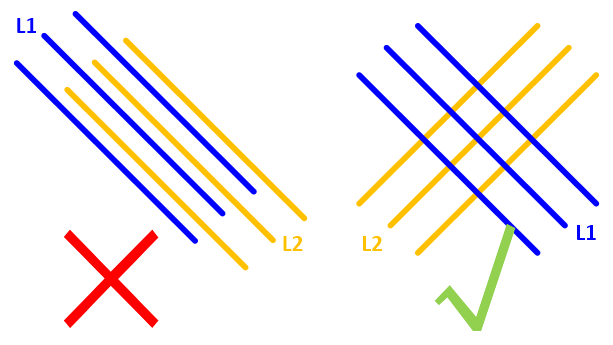

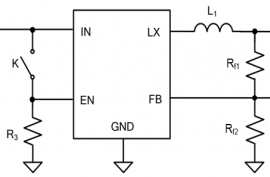

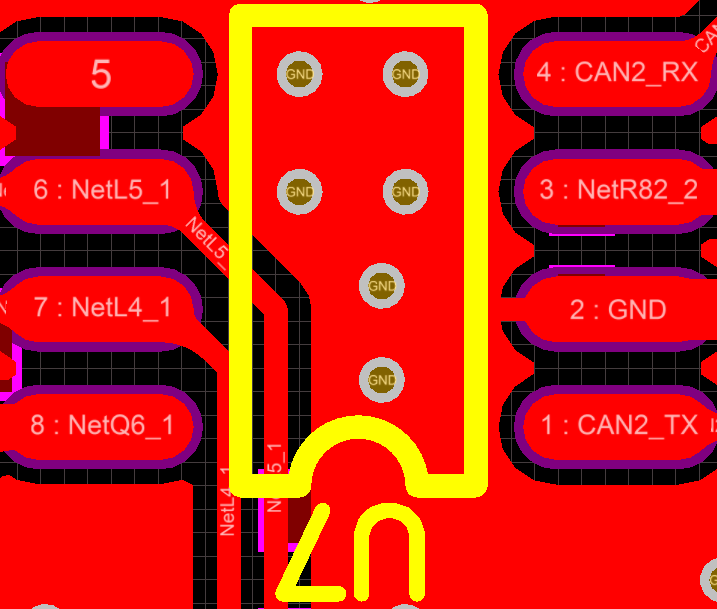

技巧5:减少引线交叉

通过调整器件位置和方向,减少引线交叉。咋弄?

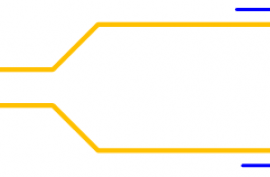

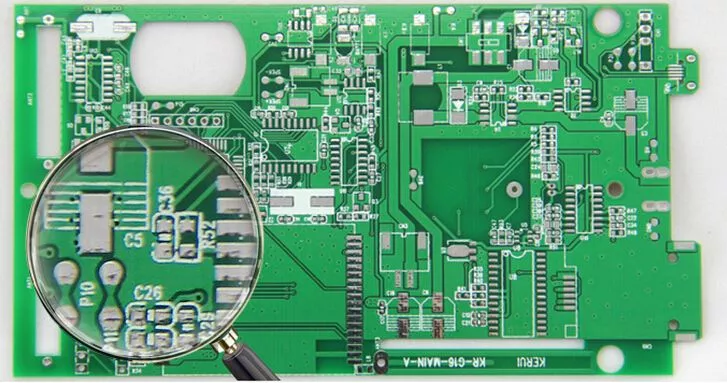

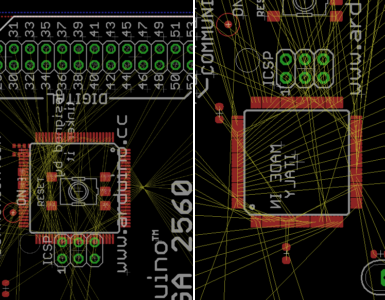

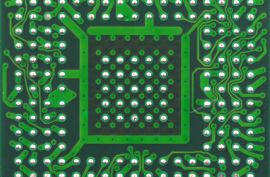

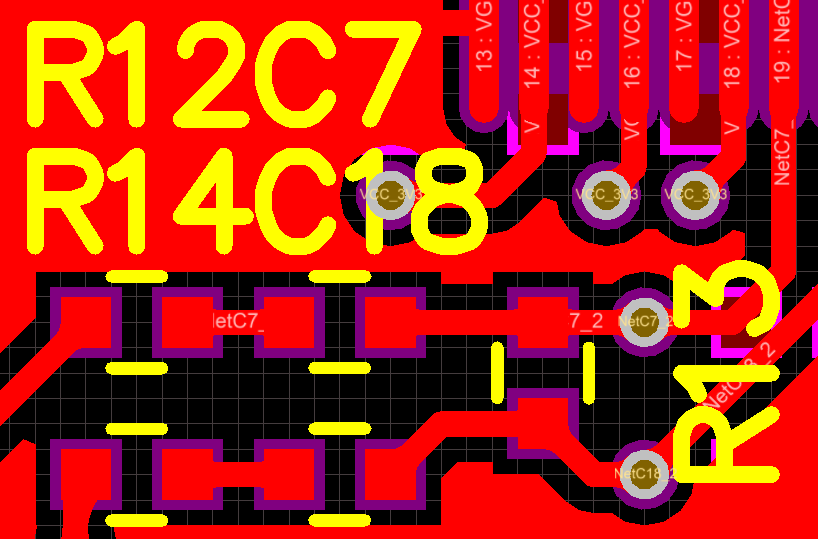

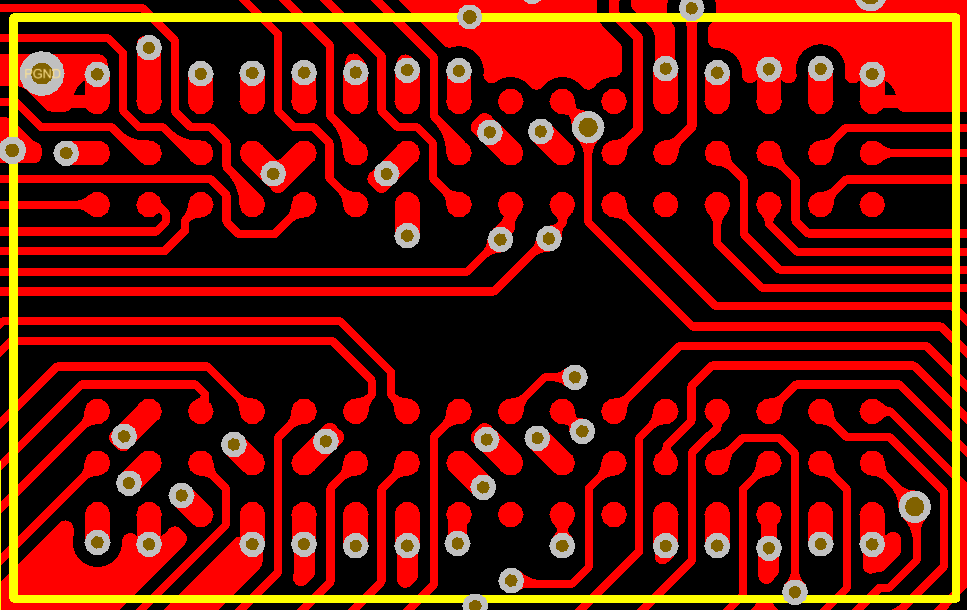

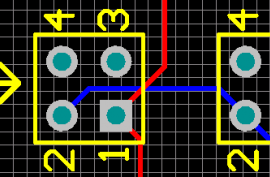

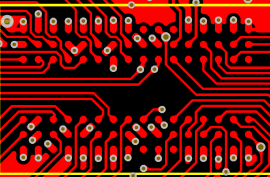

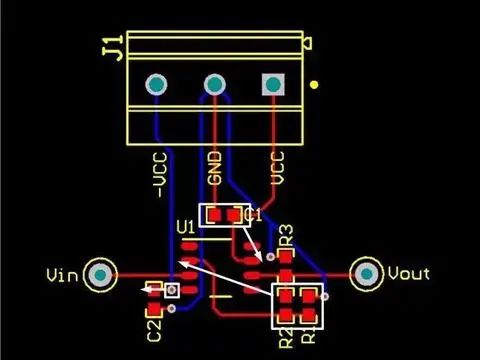

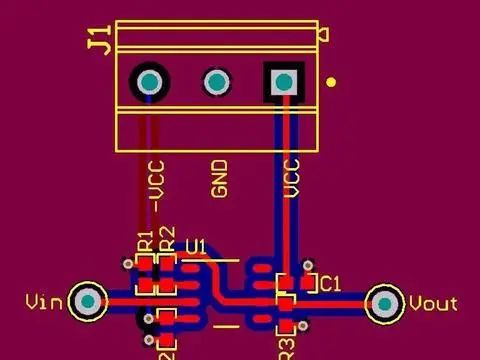

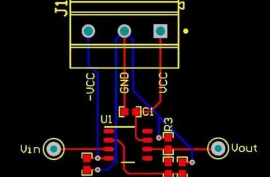

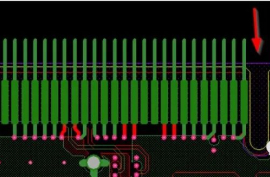

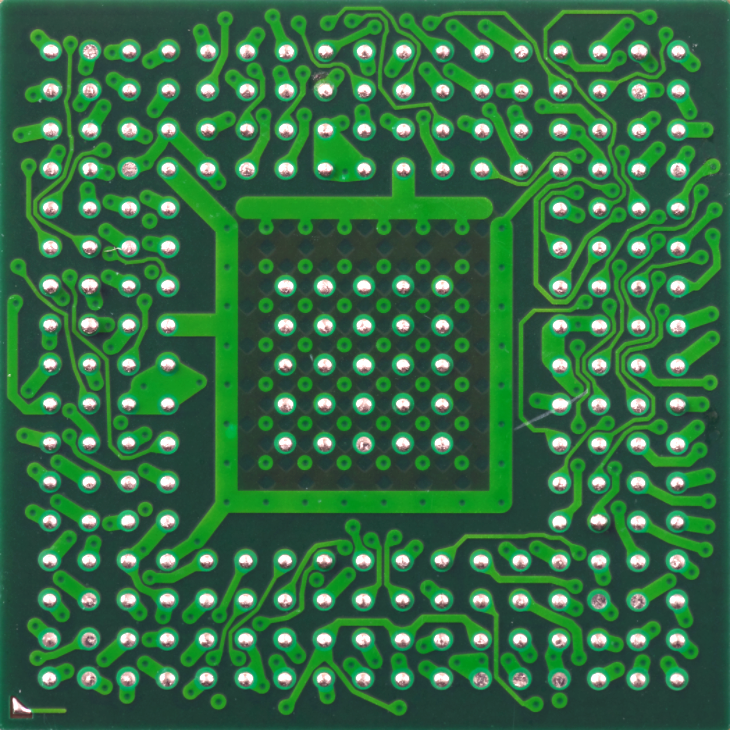

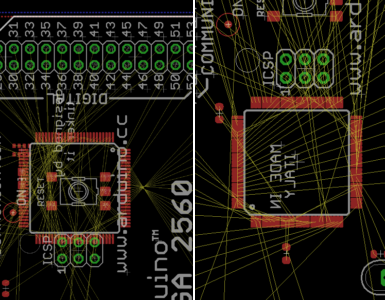

现在很多PCB设计软件都会提供一种功能,显示没有布通管脚对之间的连接关系。比如下图就显示了原理图中所有器件管脚之间的连接关系,通过图中细的灰色直线表示(这种线被称为ratsnest:y飞线,预拉线)。

通过改变器件的位置和方向,尽量减少器件之间引线交叉,可以为后面布线节省大量的精力。

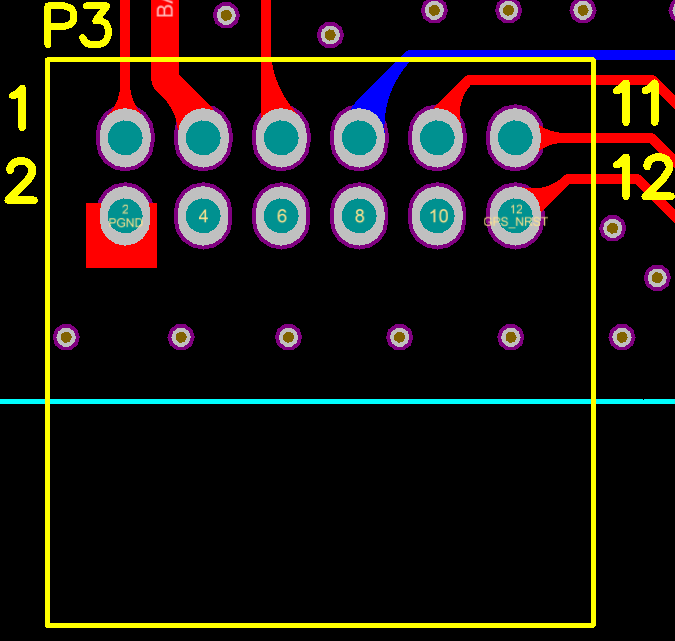

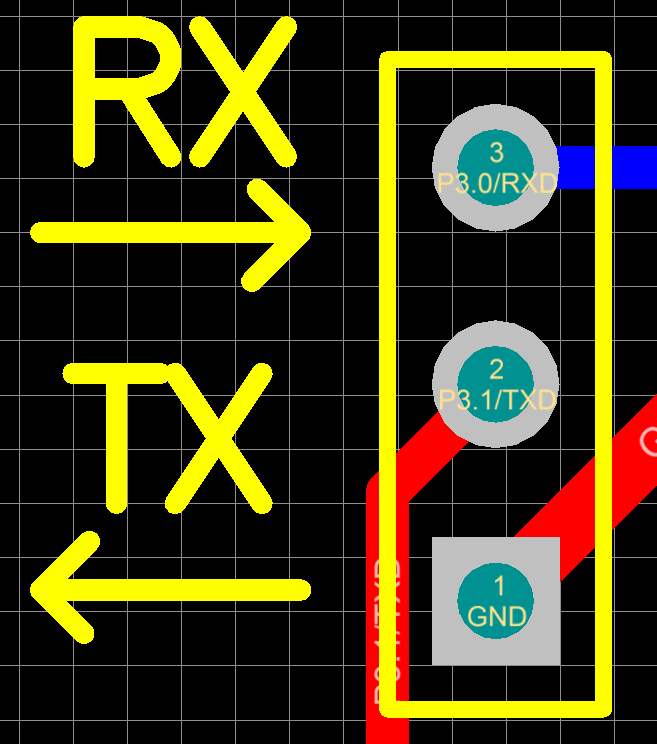

技巧6:先摆放电路边缘器件

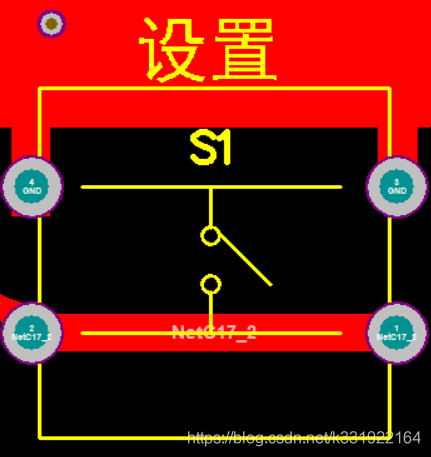

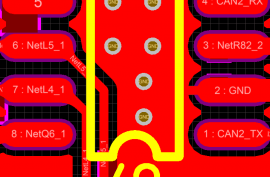

对于因受机械限制而无法任意移动的器件要先进行摆放,比如电路板上的外部接插件、开关、USB端口等等。为什么?

这些器件往往是有系统整体机械设计时就确定下的位置,不容更改。在摆放完这些器件之后,也就使得你在后面器件安排有了一个光荣的起点。搞定电路板边缘器件,剩下就是你发挥自己想象力和创造力的高光时刻了。

技巧7:避免器件之间冲突

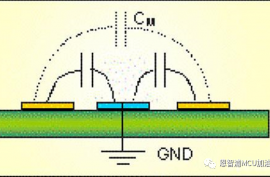

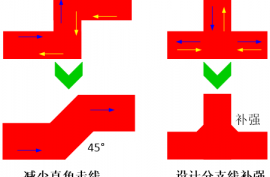

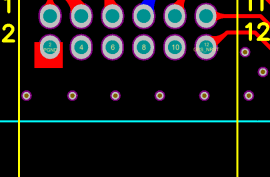

绝对避免为了在小的电路板中布线而将器件的焊盘重叠共用,或使得器件边缘重叠。最好在所有器件之间保持40mil(1mm)的距离。你有密集恐惧症?

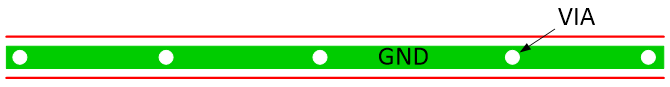

最重要原因是为了避免在之后电路制作过程中在焊盘之间产生短路故障。别忘了,紧密摆放也会使得布线变得更加的困难。同样,在放置过孔的时候也要避免过于密集。这些小圆孔将来也可能裸露出铜皮,造成电路的短路。

技巧8:将器件尽量放在同一面

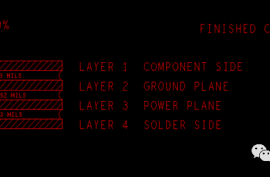

如果你设计两层电路板,最常见的建议就是将器件摆放在同一面。为什么呀?

如果不将器件放在电路板的同一面,就会使得后期电路板制作费事费力。下面告诉你原因,通常情况下,电路板上的器件是通过自动器件摆放机器完成,器件只在一面,生产PCB过程只需要一遍即可。否则,就需要两次器件摆放。浪费了生产时间,就是浪费金钱和生命。

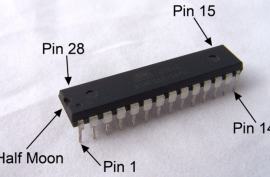

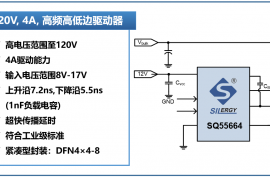

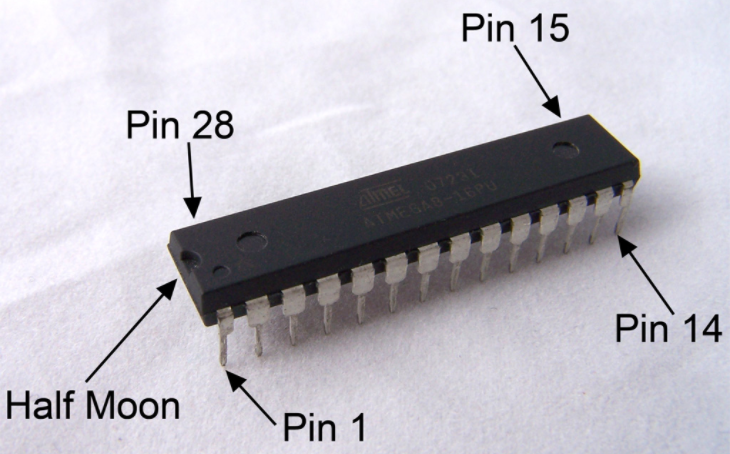

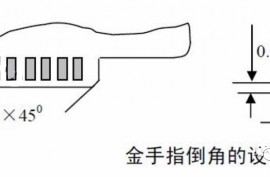

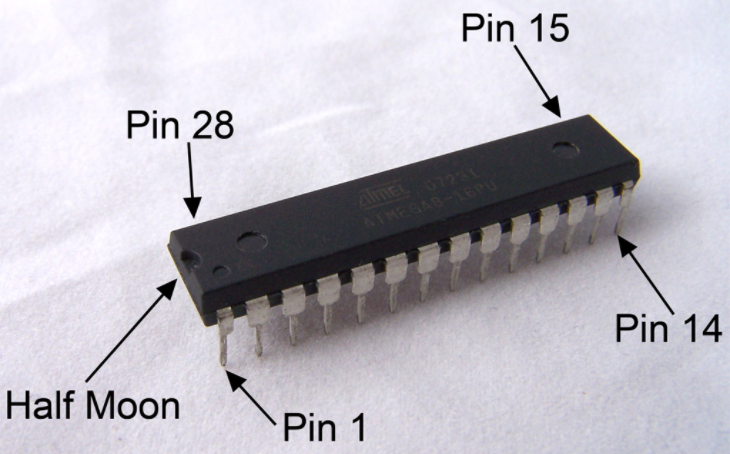

技巧9:保持芯片管脚和器件极性一致

每个集成芯片都有标志给出管脚1的起始位置。对于芯片的管脚1所在的方位,或者有极性的器件(电机电容、二极管、三极管、LED等等)方向保持一致,也会给电路板制作带来方便。有这必要吗?

如果你亲自焊接或者调试过电路板,你就不会怀疑这一点。想想看,当你焊接电路板上的元器件的极性和方向非常凌乱,是不是对于成功焊接电路板你心里也没有底?

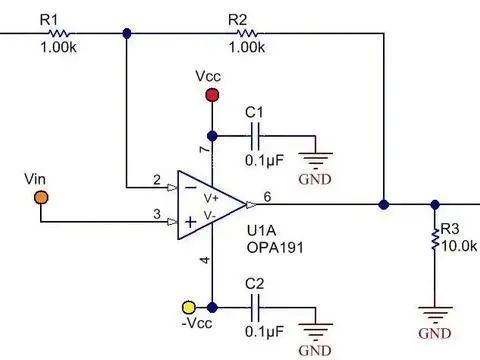

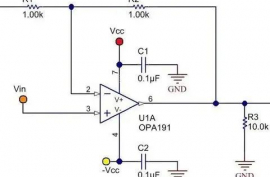

技巧10:器件位置与原理图上相似

在摆放元器件时,脑子里按照你的原理图上的位置关系进行摆放。原因何在?

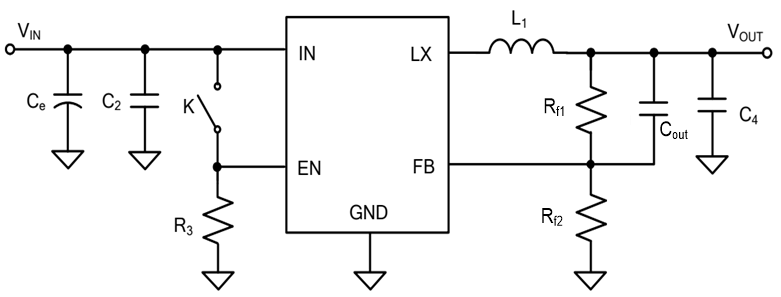

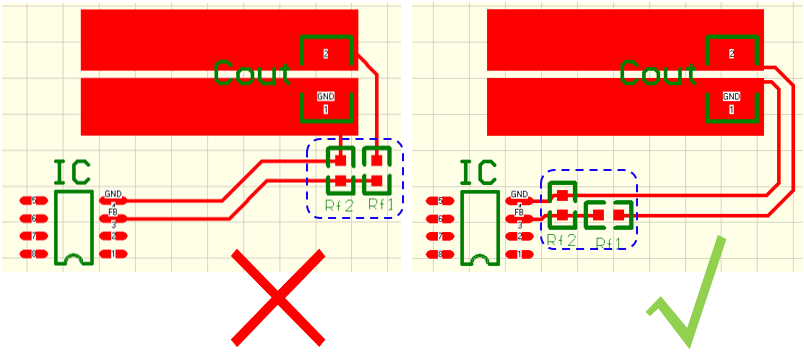

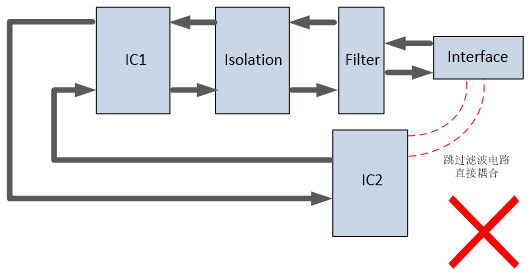

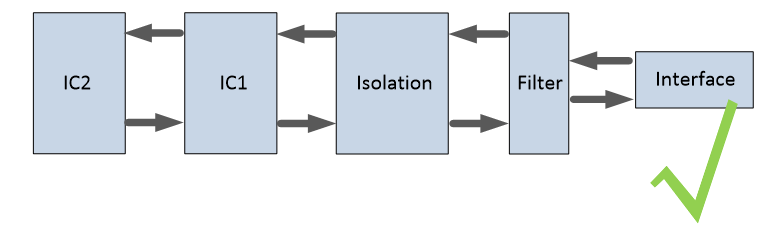

实际上,你在设计原理图的时候就已经优化了器件之间的位置关系(连线最短、交叉最少),所以呢,按照原理图上器件位置来直到PCB器件的摆放有天然的合理性。特别是,在后期手工布线的时候,脑子里的原理图也会暗地里帮你选择合理的短路径来布线。

约束下的创作

最好的PCB设计起源于器件非凡的布局,不要轻易糊弄过去。你要一直坚持把精力放在器件的合理摆放,这个过程所有的努力都是值得的,这也许是你在PCB设计中最值得全力以赴的过程。当你看到设计PCB变成电路板成品时,将是品尝劳动果实的幸福时光。

来源:网络

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。