一文搞懂啥是CPU、MPU、MCU、SoC!

1、CPU(Central Processing Unit),是一台计算机的运算核心和控制核心。

1、CPU(Central Processing Unit),是一台计算机的运算核心和控制核心。

文章来源: DIGITIMES

中国流传一句话:“黑猫白猫,能捉老鼠的就是好猫”,这是从“结果”论英雄,套用于市场法则,此话也一点不虚。

来源: http://www.tuicool.com/articles/YJfqUjV

最近在利用空余时间写一个兼容MIPS32指令集架构的CPU,尽管它和Intel的不同,但MIPS对nop指令的处理方式可以给你一点启发。

来源:玩转单片机

回到最初的问题,CPU是怎样访问内存的?简单的答案是,CPU执行一条访存指令,把读写请求发往内存管理单元。内存管理单元进行虚实转换,把命令发往总线。总线把命令传递给内存控制器,内存控制器再次翻译地址,对相应内存颗粒进行存取。之后,读取的数据或者写入确认按照原路返回。再复杂些,当中插入多级缓存,在每一层缓存都未命中的情况下,访问才会最终达到内存颗粒。

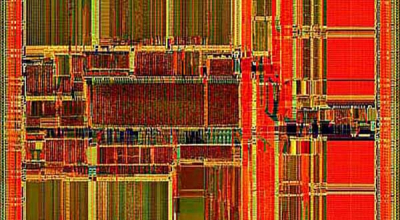

什么是单片机,相信很多人都还不知道。也不知道单片机的作用是什么。单片机简称为单片微控制器(Microcontroler),它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上,相当于一个微型的计算机,因为它最早被用在工业控制领域。单片机由芯片内仅有CPU的专用处理器发展而来。

CPU就是在一张硅片上,刻几百万个晶体二极管。制成二极管,硅的开启电压(死区电压)需要0.5V,锗的开启电压只需0.1V。也就是锗CPU只需零点几的电压就能运行,比现在的1V低多了,也算CPU的革命吧。电压更低,意味发热量更少,集成度和频率可以更高。即便开发锗CPU有困难,也比脑动大开的 量子CPU, 光子CPU, DNA CPU靠谱吧?

MCU ASE (特定应用扩展) 可扩展中断控制器支持,减少中断等待时间并加强微控制器系统设计常常要求的I/O外设控制功能。该扩展可用于MIPS32® M14K™系列处理器内核。

MCU ASE支持MIPS32和microMIPSTM指令集架构 (ISA)。

中断交付

Atmel 外设触摸控制器是电容式触摸传感模块,支持 1-256 信道的自主传感。PTC 支持在相同应用内进行自电容和互电容传感器布局,这就为系统设计师提供了极高的灵活度。由于自主运行,PTC 只使用了微乎其微的 CPU 资源和电,即使是面对高 Key Count 的设计时。凭借嵌入式自动调谐和校准,PTC 将提供高质量的触摸性能,即使是在恶劣环境下。

引言:物联网是雾计算,需推动公开参考架构如IP的发展以加快部署。

多线程编程是现代软件技术中很重要的一个环节。要弄懂多线程,这就要牵涉到多进程?当然,要了解到多进程,就要涉及到操作系统。不过大家也不要紧张,听我慢慢道来。这其中的环节其实并不复杂。