相关文章:

敏矽微电子Cortex-M0学习笔记01——芯片简介

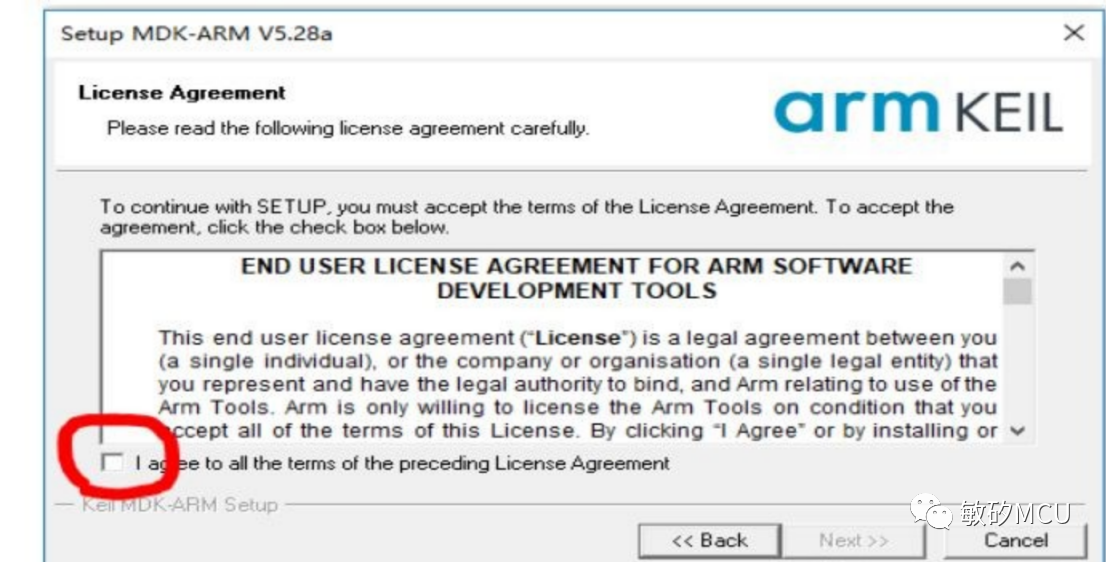

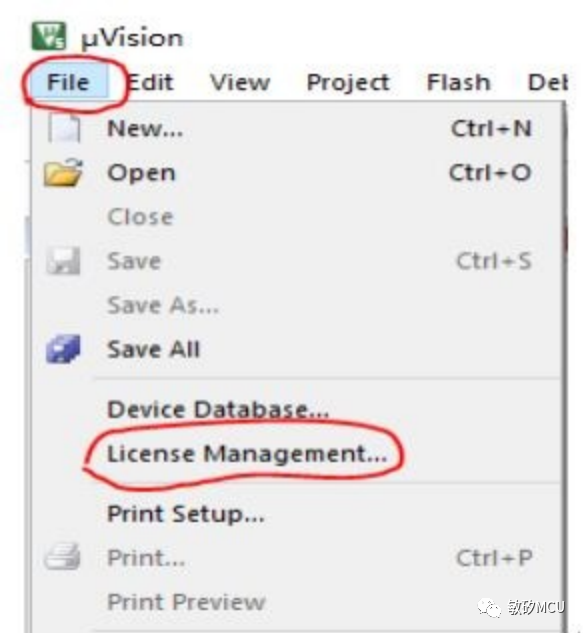

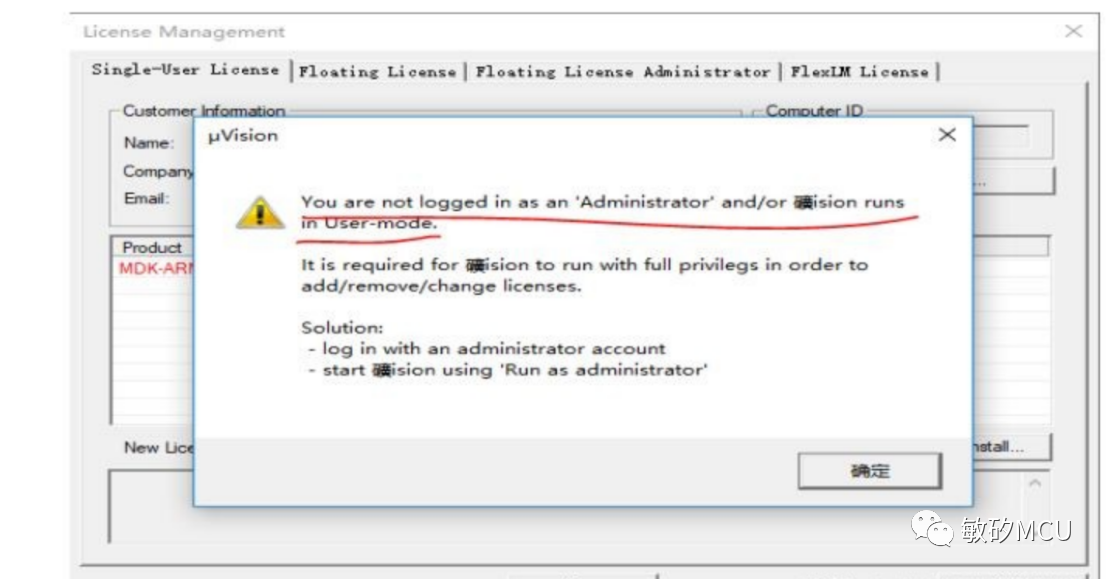

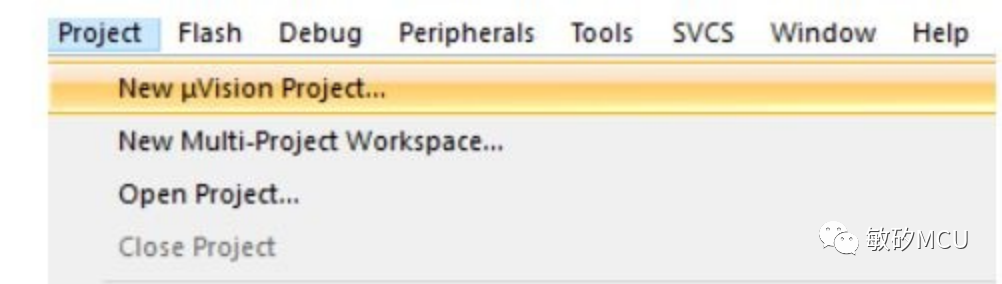

敏矽微电子Cortex-M0学习笔记02——Cortex-M0开发环境的建立及调试

敏矽微电子Cortex-M0学习笔记03——时钟系统设计例程

敏矽微电子Cortex-M0学习笔记04——GPIO详解及应用实例

敏矽微电子Cortex-M0学习笔记05——端口外部中断实例

敏矽微电子Cortex-M0学习笔记06——段式LCD液晶实例

1、UART串口简介

在单片机应用开发中,串口可以说是最常用的外设之一了。

串口最重要的功能就是能够让单片机和外部设备进行数据交互。例如在我们学习敏矽微电子的cortex m0时,可以将开发板与电脑相连,通过串口调试助手来调试程序、观察程序运行结果。还有很多其他的串口模块,比如蓝牙、 NBIOT、GPRS、4G 等模组,都是使用的串口来进行驱动的,因此掌握串口是嵌入式工程师必备的技能。

接下来我们就来学习如何驱动ME32F030上的串口。

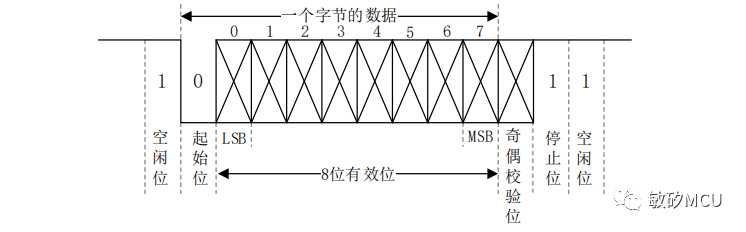

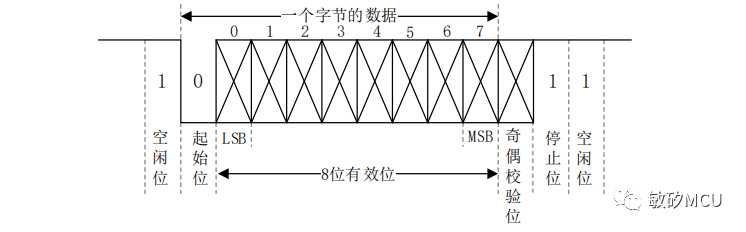

在正式学习之前,我们先对UART串口的通信格式做一个了解。UART的全称是:通用异步收发传输器(Universal Asynchronous Receiver/Transmitter)。串行传输数据是按照字节为单位进行移位传输的,因此通信速度较低。但其拥有线路简单、通信距离远的优点,使用两条线即可实现双向通信,一条用于发送,一条用于接收。因此在工业应用中受到广泛应用。其通信格式也十分简单,如下图所示:

图1 UART数据格式

空闲位:数据线在空闲状态的时候保持高电平,表示没有数据传输。

起始位:当要传输数据的时候,数据线会被拉低,表示开始数据传输。

数据位:数据位就是实际要传输的数据,一般都是按照字节传输数据的,即一次传输8 位数据的。一般都是低位在前,高位在后。当然也有相反的传输协议,但平时很少会遇到。

奇偶校验位:这是对数据中“1”的位数进行奇偶校验用的,可以根据需求进行选择。

停止位:数据传输完成标志位,停止位的位数可以选择 1 位、1.5 位或 2 位高电平,一般都选择 1 位停止位。

波特率:波特率就是 UART 数据传输的速率,也就是每秒传输的数据位数,一般选择 9600、19200、115200 等。

随着电脑日新月异的升级换代,现在很多电脑都不带传统的COM口,USB接口开始广泛应用。所以就有了USB转串口芯片来解决这个难题,常用的U转串芯片有CH340、PL2303 等。通过这些芯片就可以实现串口 TTL 转 USB。

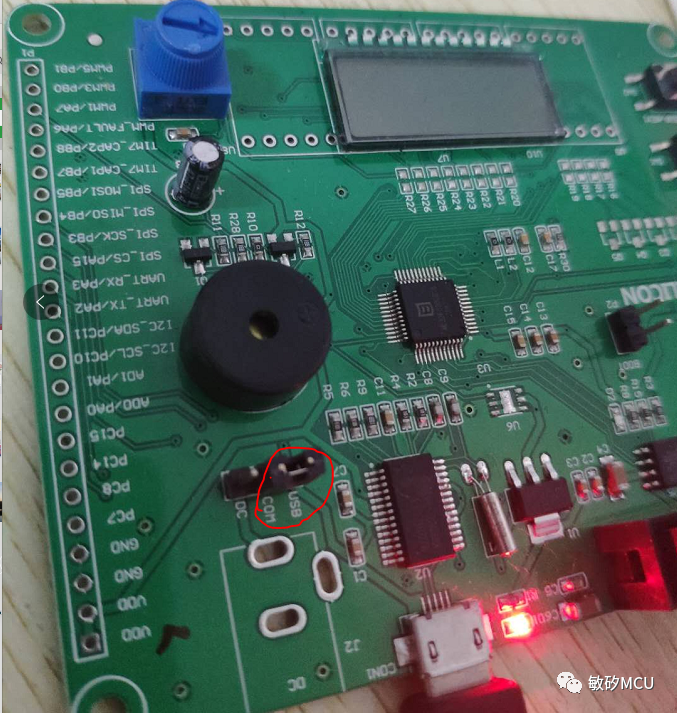

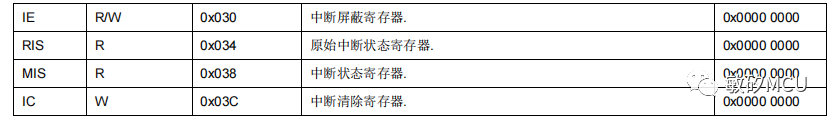

ME32F030开发板使用的是PL2303 芯片来完成串口和电脑之间的连接,只需要一条USB 线即可。在使用前需要注意两件事:第一,先下载并安装PL2303的驱动程序。第二,检查开发板的USB跳线帽是否接到COM、USB这边。正确的接法如下:

图2 跳线连接

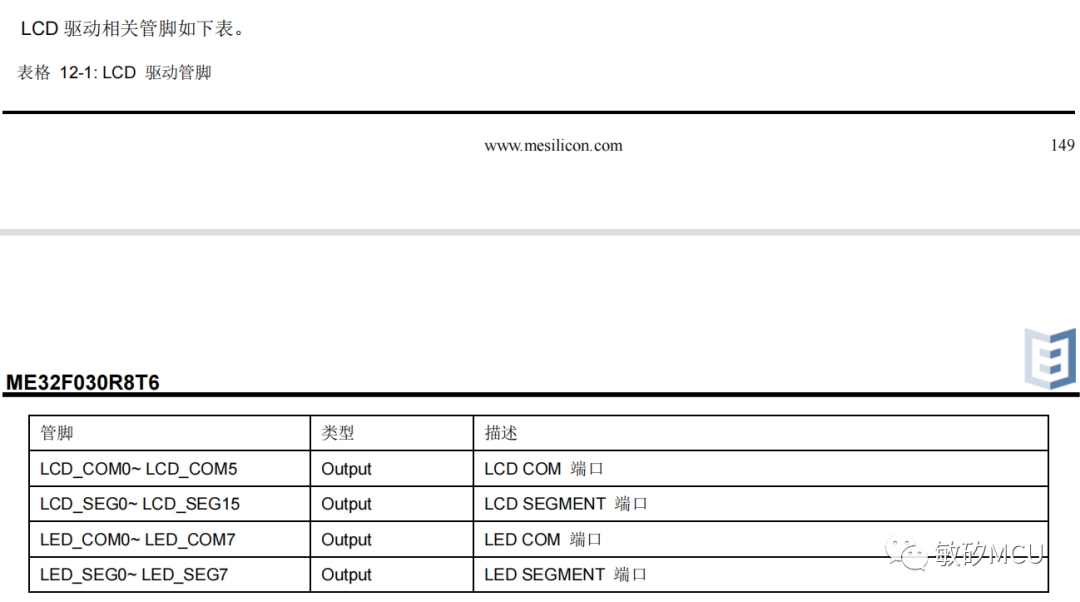

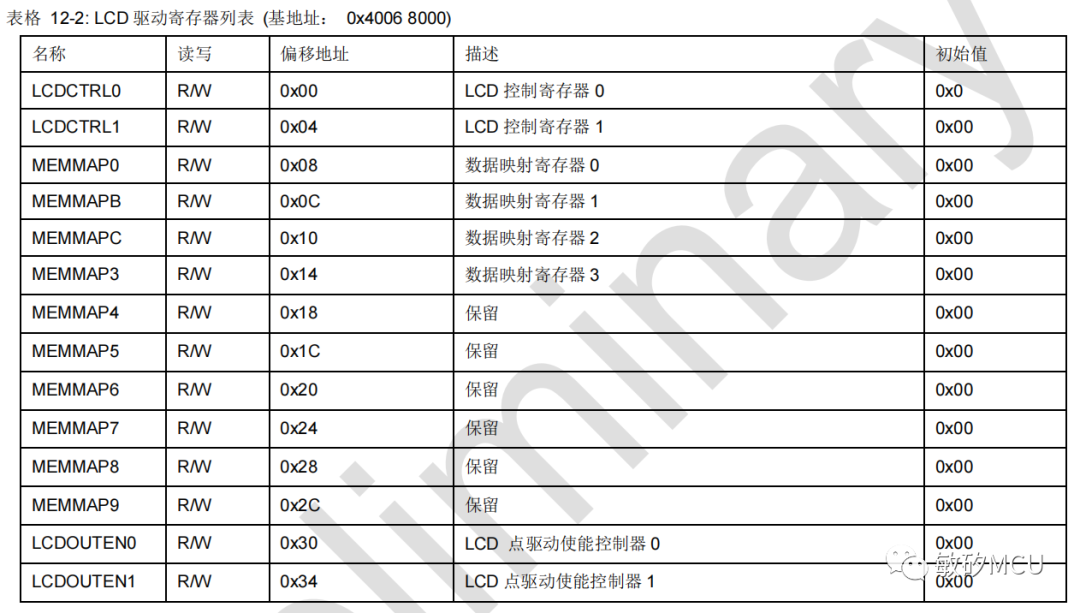

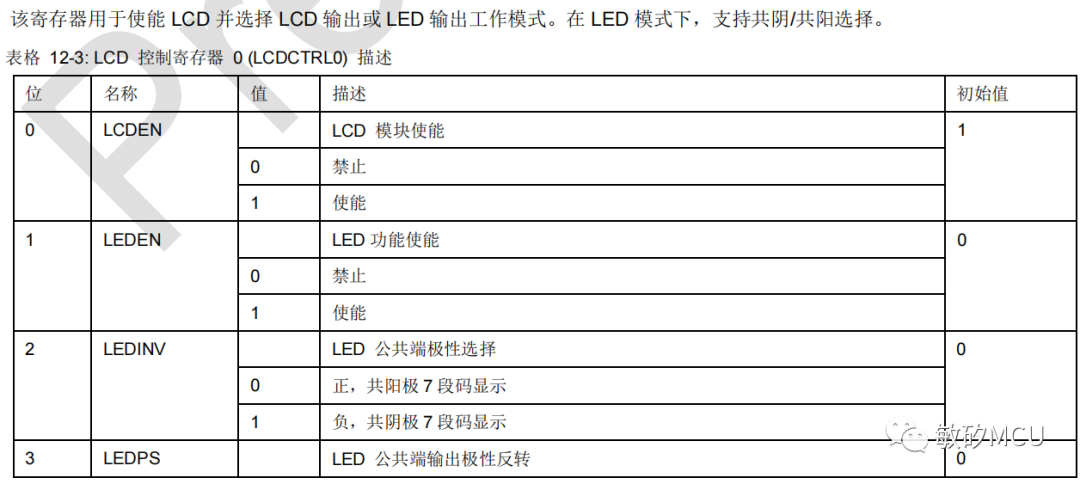

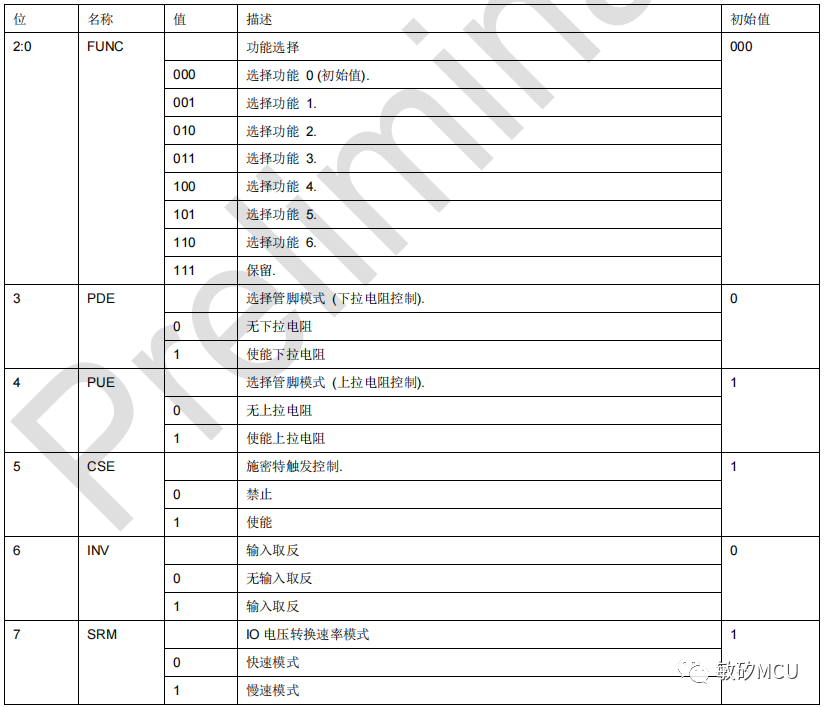

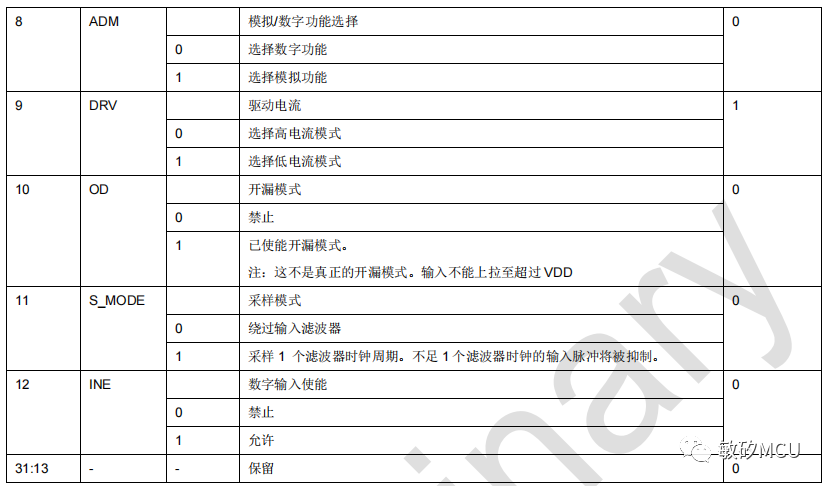

2、UART驱动寄存器

ME32F030 提供2个 UART 外设:UART0,UART1。串行接口都支持红外传输(IrDA)协议功能。时钟都受 SYSAHBCLKCTRL 寄存器控制。同时每个 UART 有独立的时钟分频器来产生波特率,并使之不受系统时钟和PCLK影响。UART对应的管脚映射图如下:

图3 UART管脚映射

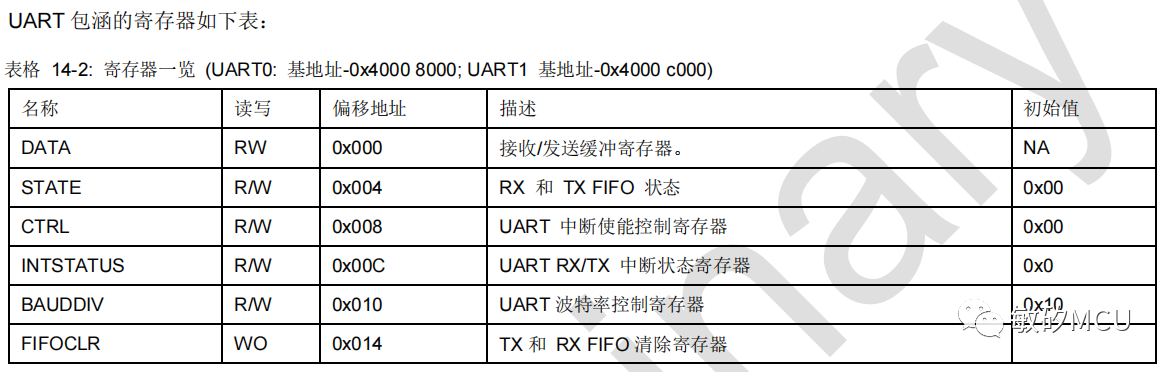

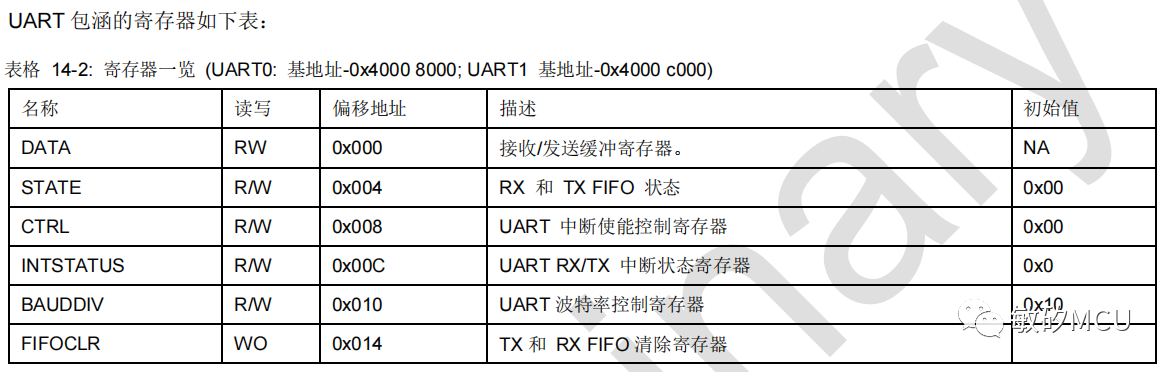

看完管脚的映射关系,接下来就列出与UART相关的寄存器组,随后会挨个进行讲解。

图4 UART寄存器

2-1 UART接收/发送缓冲寄存器

UART 接收/发送缓冲寄存器包含着 UART 接收到/将发送的字节,接收到的数据和待发送的串口数据都在该寄存器中。

2-2 UART状态寄存器

该寄存器用于提供 UART 接收发送缓存器的状态。大致可以归类为以下几种状态:

发送状态:发送FIFO空、发送FIFO半满、发送FIFO满。

接收状态:接收FIFO空、接收FIFO半满、接收FIFO满。

奇偶校验状态:没有奇偶校验错误,或检测到奇偶错误,写1来清除错误标志。

接收缓存器溢出状态 :用来表明缓存器是否溢出。

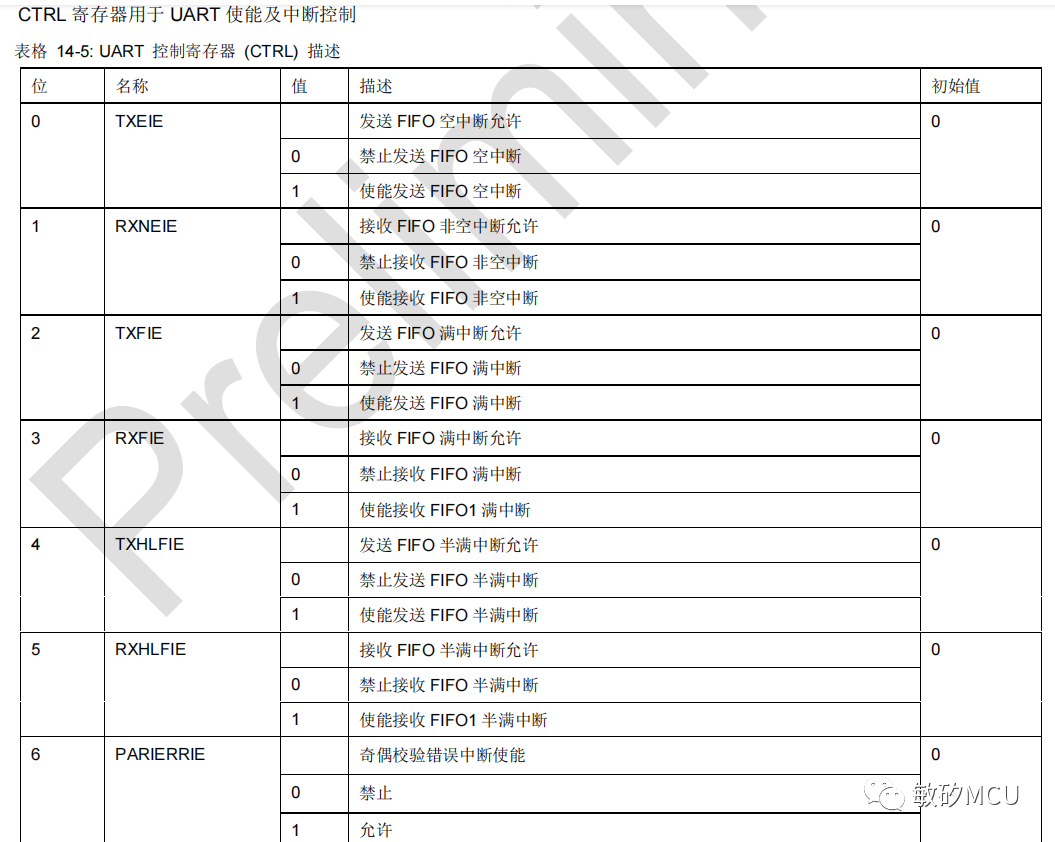

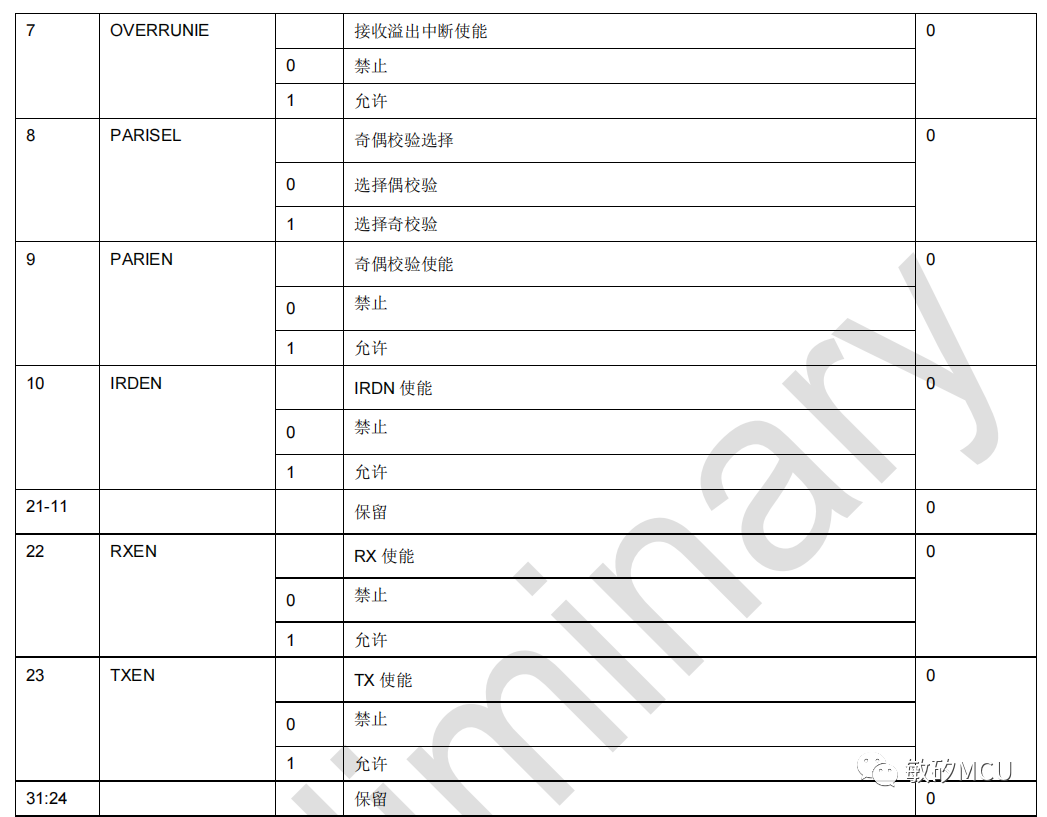

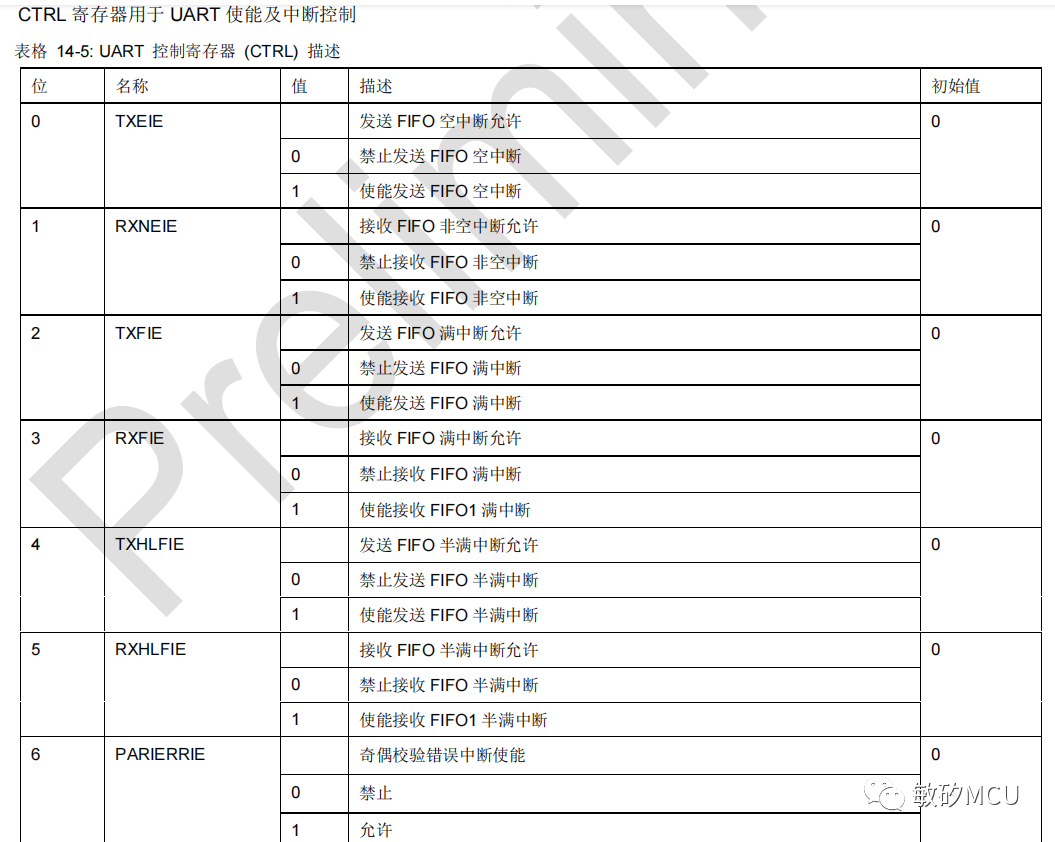

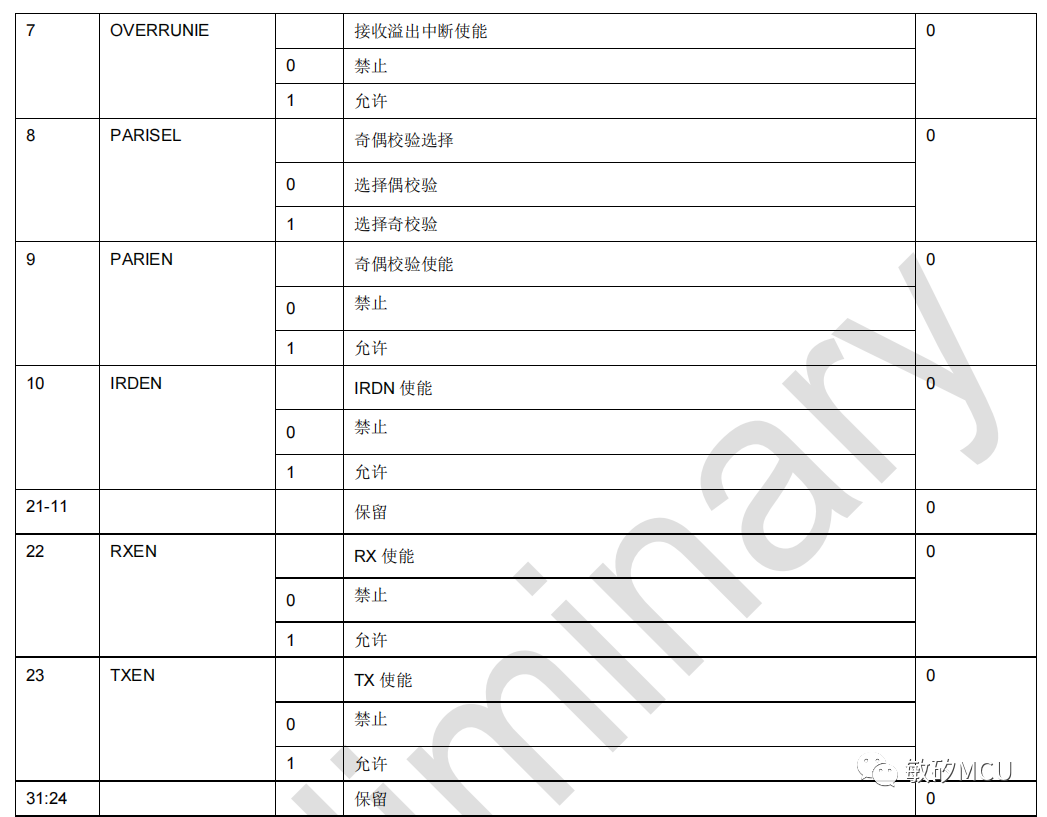

2-3 UART控制寄存器

接下来就要着重讲解下UART控制寄存器了。0-5位属于基本的接收、发送中断使位,这里不再累述。

BIT6:奇偶校验中断使能,使能该中断后,当接收到的数据发生奇偶校验错误后,会产生中断通知串口接收发生错误。

BIT7:接收溢出中断使能,使能该中断后,当接收到的数据超出FIFO容量就会产生中断。通知及时取出数据或者清空FIFO。

BIT8:奇偶校验方式选择位,0为偶校验,1为奇校验。这里注意,这只是选择了奇偶校验的方式,但是并不会生效,是否启动校验还需要下面介绍的寄存器。

BIT9:奇偶校验使能位,只有当该位置1才会使能奇偶校验,具体的校验方式由刚才介绍的奇偶校验方式选择位来决定。

BIT10:IRDA传输协议使能位,置1使能。

BIT22:RX接收使能,置1使能。

BIT23:TX发送使能,置1使能。

图5 UART控制寄存器

2-4 UART中断状态寄存器

既然刚才在介绍UART控制寄存器的时候,介绍了不少中断使能控制。肯定就会有相应的中断状态的管理。UART中断状态寄存器从低位开始依次管理着:①、发送结束中断状态,②、接收完成中断状态,③、发送FIFO满中断,④、接收FIFO满中断,⑤、发送FIFO半满中断,⑥、接收FIFO半满中断,⑦、奇偶校验错误中断,⑧、接收溢出中断。

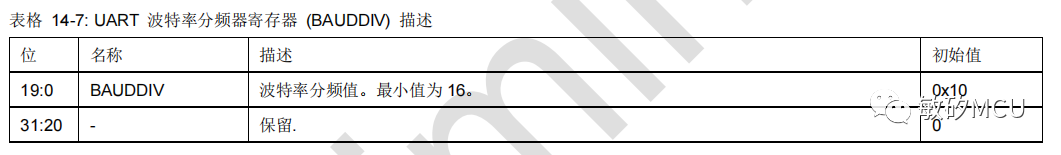

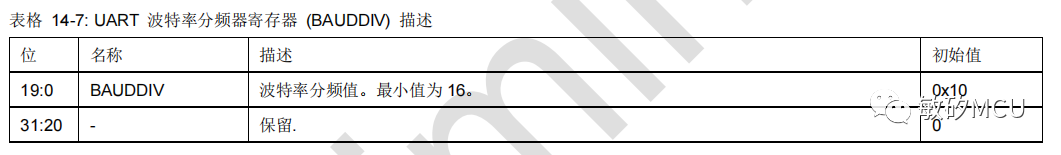

2-5 UART 波特率分频器寄存器

UART 波特率分频器寄存器 (BAUDDIV) 用于时钟分频从而产生相应的波特率。该寄存器可读写。该分频器的时钟源是由UARTnCLKDIV 控制 UART 的波特率源时钟(SCLK)。

图6 UART 波特率分频器寄存器

波特率分频值计算公式:

BAUDDIV = SCLK / UART BAUDRATE

2-6 UART TX/RX FIFO 数据清除寄存器

操作该寄存器可以快速对TX/RX FIFO进行数据清空。

图7 UART TX/RX FIFO 数据清除寄存器

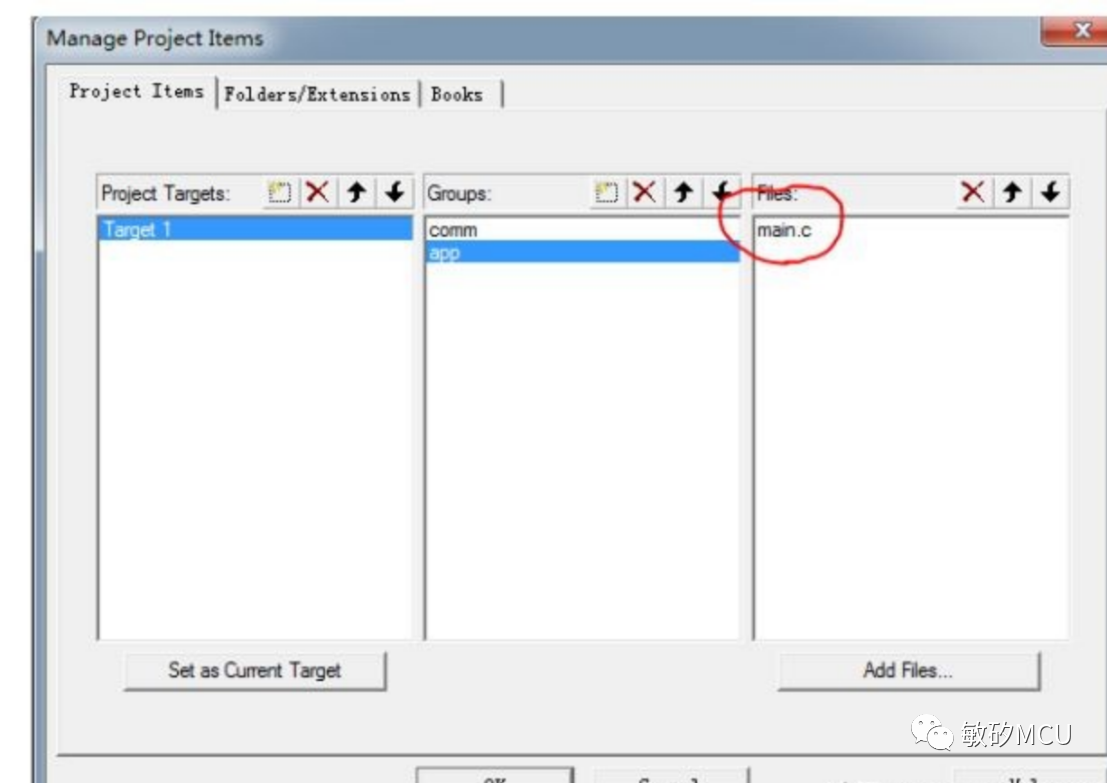

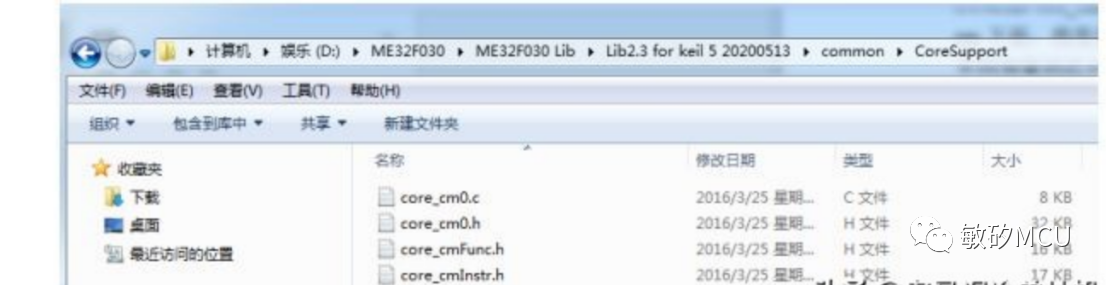

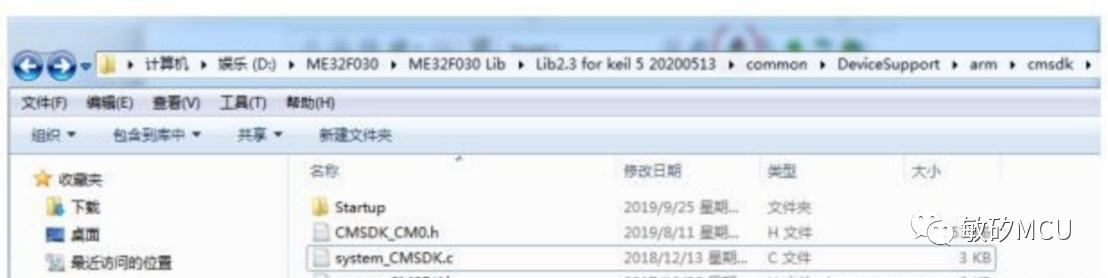

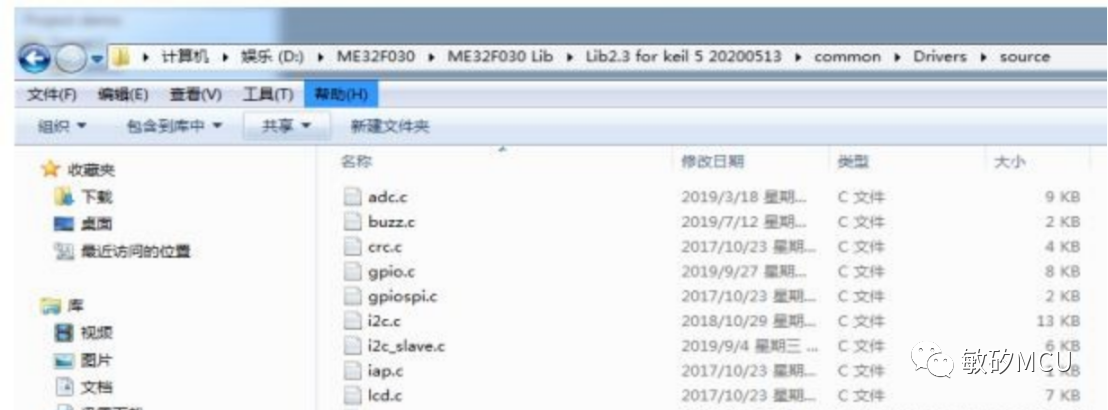

3、UART驱动函数

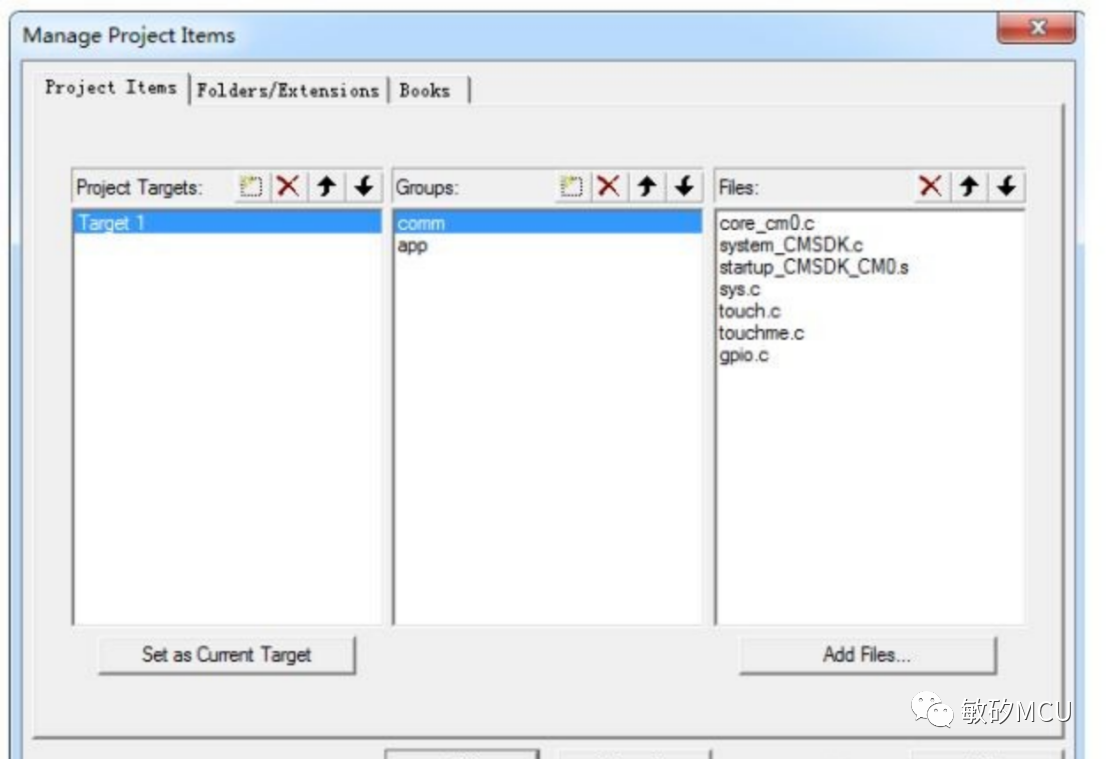

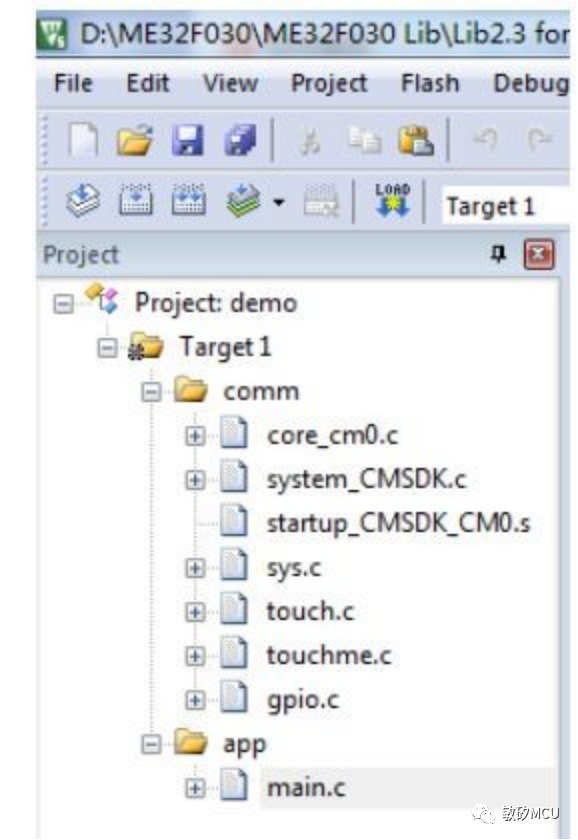

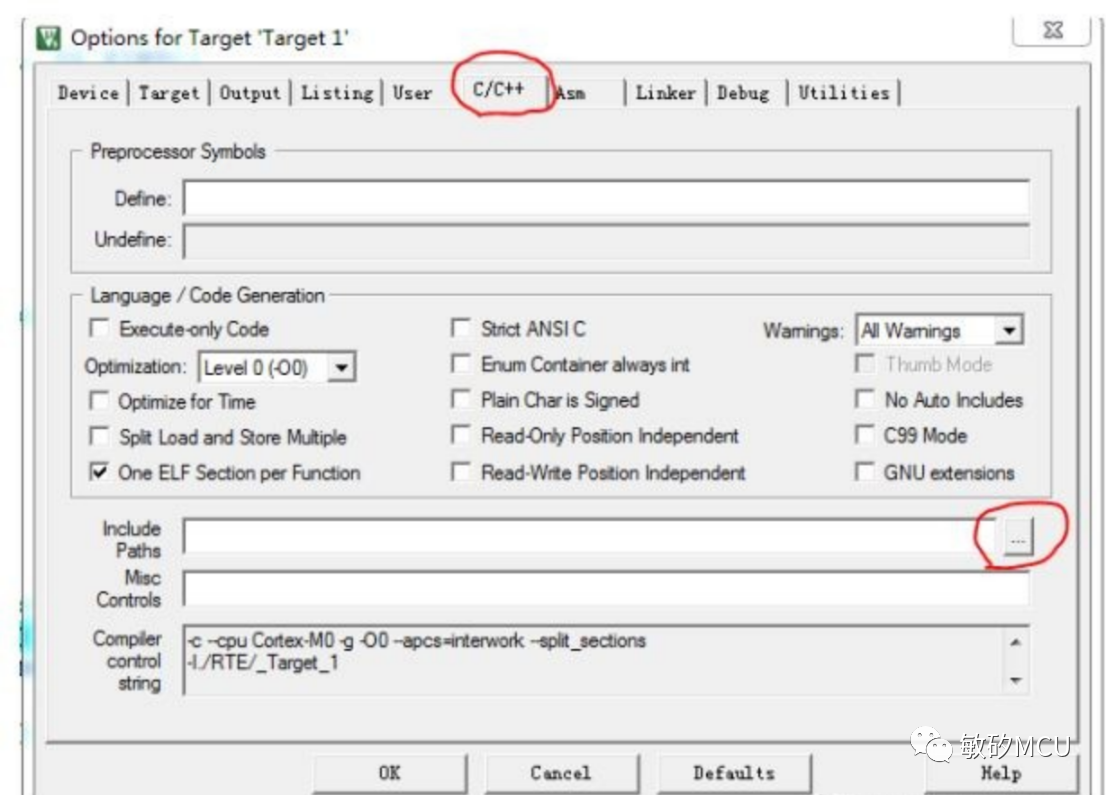

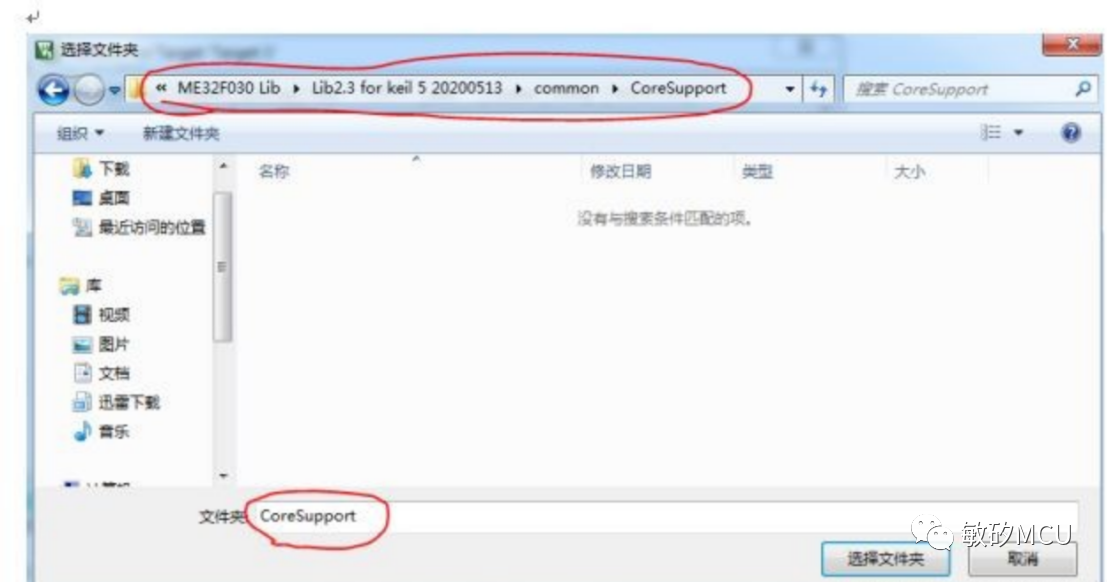

在例程LIB->common->Drivers->Source文件夹内有uart.c文件,这个就是提供的UART驱动文件,里面包含了一些基本的驱动函数,使用起来十分方便。下面会对每个函数进行讲解。

3-1 UART初始化

在每段源代码的后面,笔者对其进行一下注释,方便大家快速掌握和使用这个函数。这个函数的4个参数的意义如下:

uart:要使能的UART模块,可选UART0、UART1。

baudrate:要设置的串口的波特率。

parityoption:奇偶校验位,可选UART_EVEN_PARITY(奇校验)、 UART_ODD_PARITY(偶校验)、 UART_RX_NO_INT(无校验)。

rxinttriggerlevel:接收中断触发条件。

void UART_Open(UART0_Type *uart, uint32_t baudrate, uint8_t parityoption, uint8_t rxinttriggerlevel)

{

uint32_t volatile delays;

if (uart==UART0)

{

//初始化时关闭UART0 IRQ

NVIC_DisableIRQ(UART0_IRQn);

//使能 UART0 时钟

SYSCON->SYSAHBCLKCTRL_b.UART0_CLK=1; //enable UART0 PCLK

SYSCON->UART0CLKDIV_b.DIV = 0x1; /* divided by 1 */

//复位 UART0

SYSCON->PRESETCTRL_b.UART0_RST_N=0;

SYSCON->PRESETCTRL_b.UART0_RST_N=1;

}

else if (uart==UART1)

{

//初始化时关闭UART1 IRQ

NVIC_DisableIRQ(UART1_IRQn);

//使能 UART1 时钟

SYSCON->SYSAHBCLKCTRL_b.UART1_CLK=1; //enable UART1 PCLK

SYSCON->UART1CLKDIV_b.DIV = 0x1; /* divided by 1 */

//复位 UART1

SYSCON->PRESETCTRL_b.UART1_RST_N=0;

SYSCON->PRESETCTRL_b.UART1_RST_N=1;

}

else return ;

//设置波特率

uart->BAUDDIV_b.BAUDDIV = MainClock/baudrate;

//设置奇偶校验

if (parityoption==UART_ODD_PARITY)

uart->CTRL_b.PARISEL=1;

if (parityoption!=UART_NO_PARITY)

uart->CTRL_b.PARIEN=1;

//设置中断触发条件

if (rxinttriggerlevel==UART_RX_NOT_EMPTY)

uart->CTRL_b.RXNEIE=1;

if (rxinttriggerlevel==UART_RX_HALF_FULL)

uart->CTRL_b.RXHLFIE=1;

if (rxinttriggerlevel==UART_RX_FULL)

uart->CTRL_b.RXFIE=1;

//使能发送和接收功能

uart->CTRL_b.TXEN=1;

uart->CTRL_b.RXEN=1;

//插入延时

SYS_DelaymS(1);

//清空 FIFO

uart->FIFOCLR=0xFF;

return;

}3-2 UART关闭

这段函数用来关闭UART0或者UART1,只需要传入需要关闭的串口即可。

void UART_Close(UART0_Type *uart)

{

if (uart==UART0)

{

//关闭UART0_IRQ

NVIC_DisableIRQ(UART0_IRQn);

//关闭UART0时钟

SYSCON->SYSAHBCLKCTRL_b.UART0_CLK=0;

}else if (uart==UART1)

{

//关闭UART1_IRQ

NVIC_DisableIRQ(UART1_IRQn);

//关闭UART1时钟

SYSCON->SYSAHBCLKCTRL_b.UART1_CLK=0;

}

else return ;

//关闭相应UART的中断,并清除中断标志

UART_DisableInt(uart);

UART_ClearIntFlag(uart);

return;

}3-3 UART读取单个字节

这段函数的作用是UART读取单个字节的数据。

uint8_t UART_ByteRead(UART0_Type *uart, uint8_t *data)

{

if (uart->STATE_b.RXNE)

{

*data=uart->DATA;

return 0;

}

else

return 1;

}3-4 UART连续读取多个字节

UART连续读取串口数据,直到读取到指定长度的数据。

void UART_Read(UART0_Type *uart, uint8_t * rxbuf, uint8_t *readbytes)

{

uint8_t temp=0;

//get all data

while ((uart->STATE_b.RXNE)&&((*readbytes)--))

{

*rxbuf++=uart->DATA;

temp++;

}

//return number of read

*readbytes=temp;

return;

}3-5 UART发送单个字节

这段函数的作用是UART发送单个字节的数据。

uint8_t UART_ByteWrite(UART0_Type *uart, uint8_t data)

{

if (uart->STATE_b.TXF)

return 1;

uart->DATA=data;

return 0;

}3-6 UART连续发送多个字节

UART连续发送串口数据,直到发送完指定长度的数据。

void UART_Send(UART0_Type *uart, uint8_t * txbuf, uint32_t sendbytes)

{

while (sendbytes--)

{

while (uart->STATE_b.TXF);

uart->DATA=*txbuf++;

}

return;

}3-7 UART发送字符串

UART发送一段字符串数据,只需要将要发送的字符串数据首地址传入即可。

void UART_PutString (UART0_Type *uart, uint8_t * str)

{

while (!(* str=='\0'))

{

while (uart->STATE_b.TXF);

uart->DATA=*str++;

}

return;

}3-8 UART使能中断

有两个参数项,第一个是选择需要使能的UART,第二个选择触发中断的条件。

void UART_EnableInt(UART0_Type *uart, uint32_t intcon)

{

uart->CTRL |= intcon;

return;

}3-9 UART关闭中断

调用该函数后,所有的串口的中断触发条件都将关闭。

void UART_DisableInt(UART0_Type *uart)

{

uart->CTRL &= 0xFFFFFF00;

return;

}4、串口中断例程

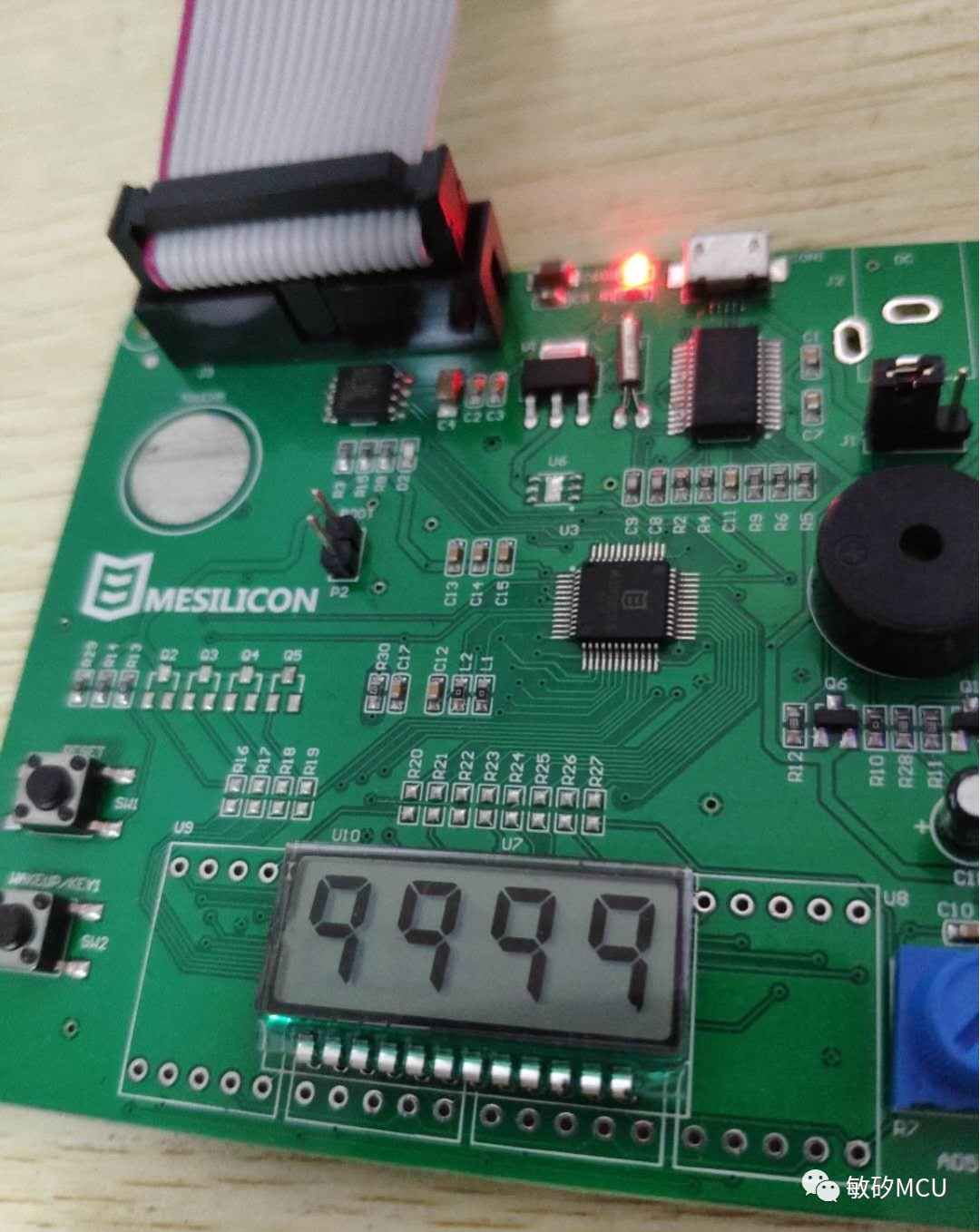

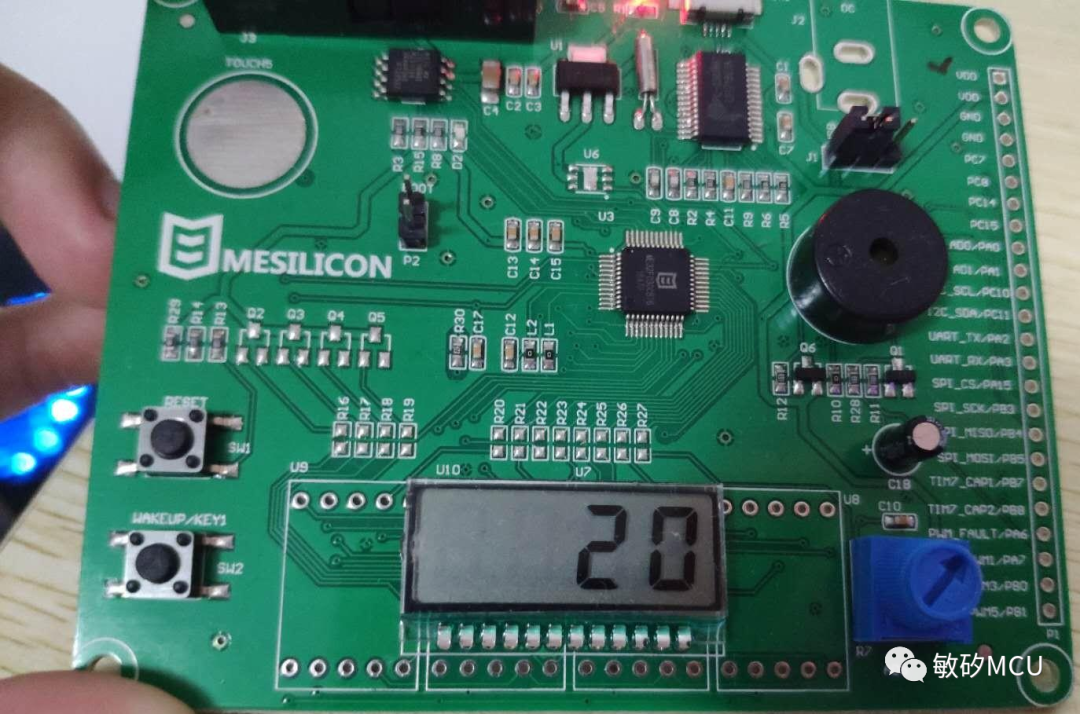

介绍完UART常用的驱动函数,接下来用个小例程来演示下UART的驱动。测试程序的功能是:通过串口助手发送一个字节的数据到单片机,单片机收到该数据后,将该数据通过单片机的串口发送到串口助手。

程序设计思路

首先是对UART0端口的初始化,将IO口复用为串口UART0的TX、RX功能。

随后将UART0初始化为波特率115200,无奇偶校验,接收非空触发中断。

下一步就是使能UART0的中断,中断触发条件为接收FIFO非空。

最后使能UART0_IRQn中断服务子程序。

测试程序的代码如下:

int main(void)

{

//UART0 端口初始化

PA_2_INIT(PA_2_TX0);

PA_3_INIT(PA_3_RX0);

//UART0 寄存器初始化

UART_Open(UART0,115200,UART_NO_PARITY,UART_RX_NOT_EMPTY);

UART_EnableInt(UART0,UART_RX_NOT_EMPTY);

NVIC_EnableIRQ(UART0_IRQn);

while(1)

{

}

}

//UART0 中断服务子程序

void UART0_IRQHandler(void)

{

uint8_t cdata;

//判断中断状态位

if (UART0->INTSTATUS_b.RXNEINT )

{

cdata = UART0->DATA; //将接收到的数据返回

UART0->DATA=cdata;

}

//清除中断状态

UART0->INTSTATUS = 0x0F;

}程序调试

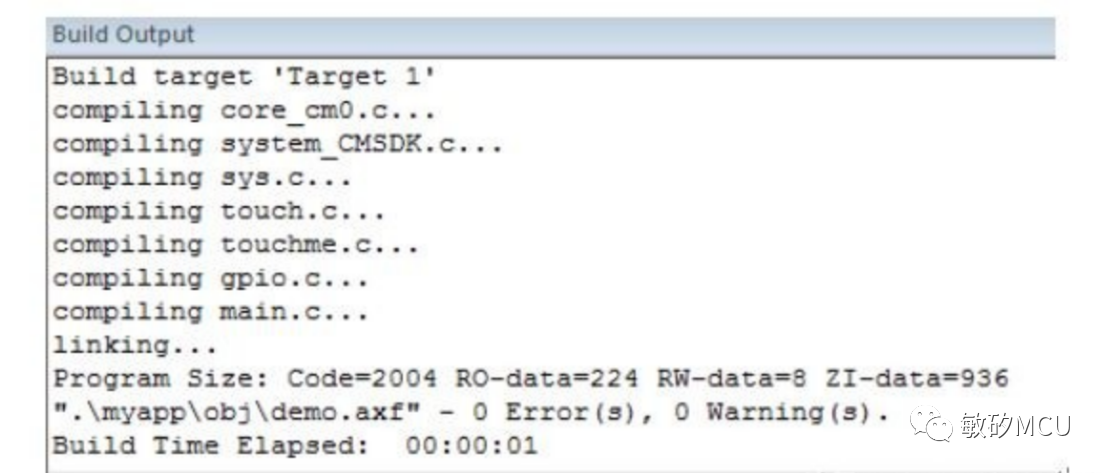

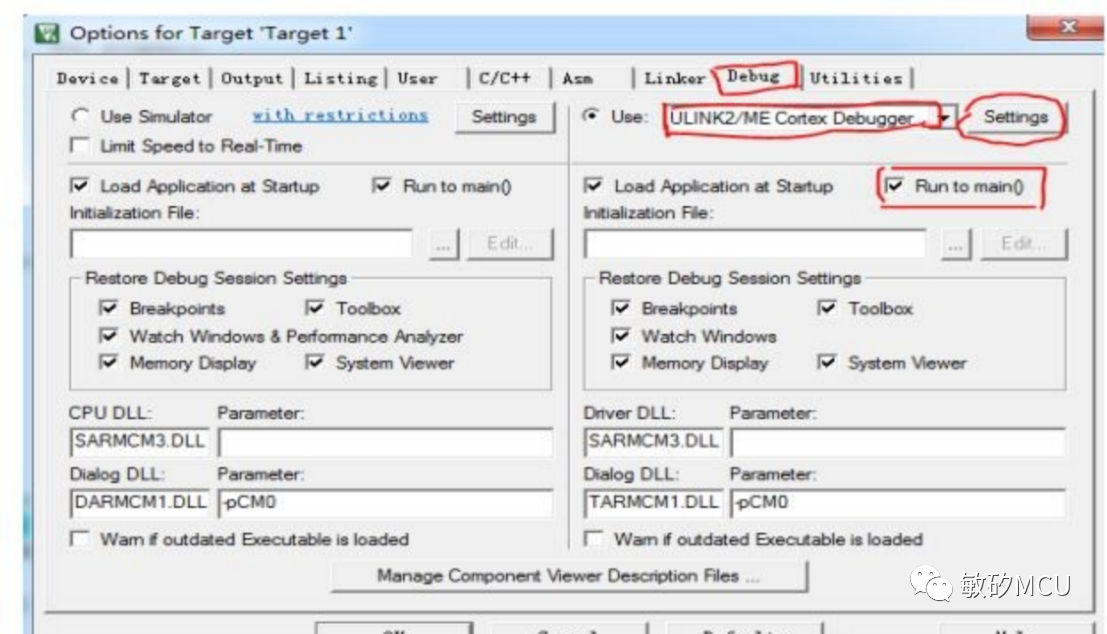

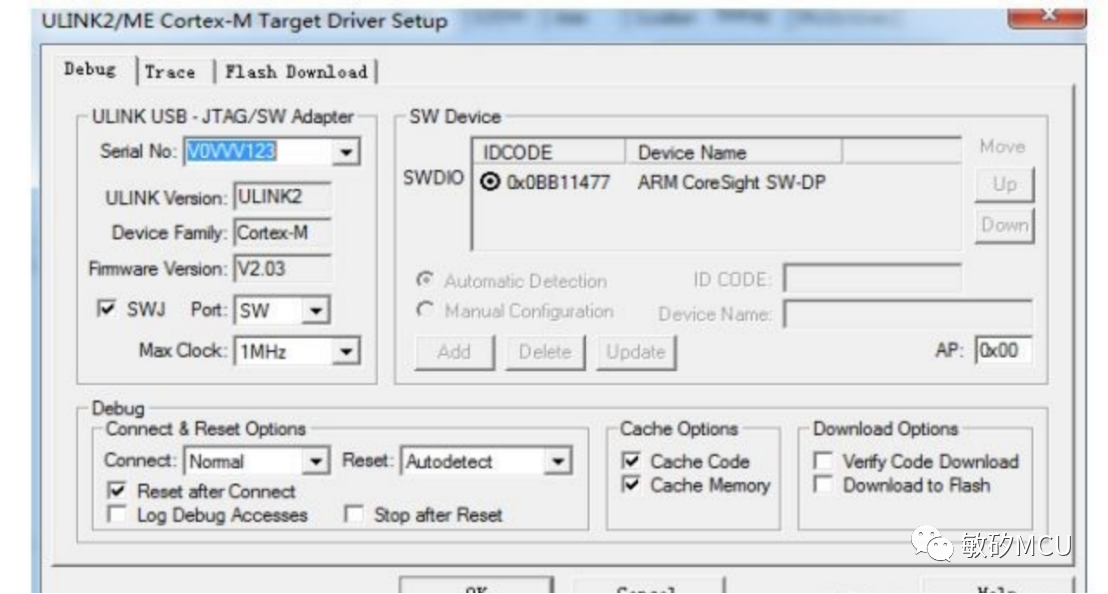

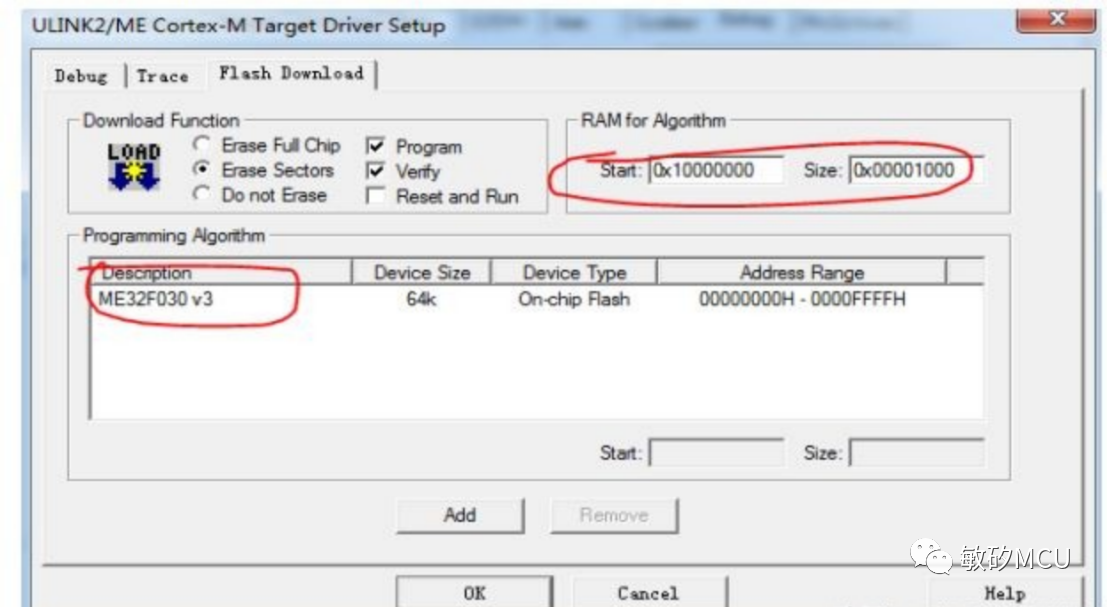

编写完程序,首先要在编译环境下进行编译、连接。没有错误后(最好连警告也没有)。就可以实际连接到电路板进行程序调试运行了。

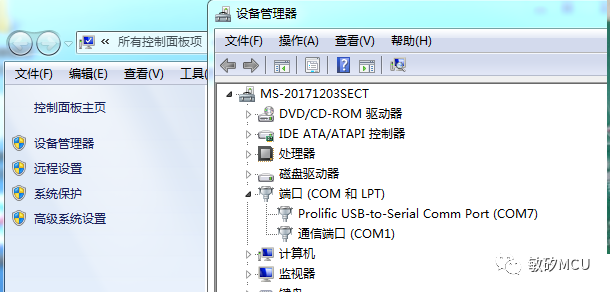

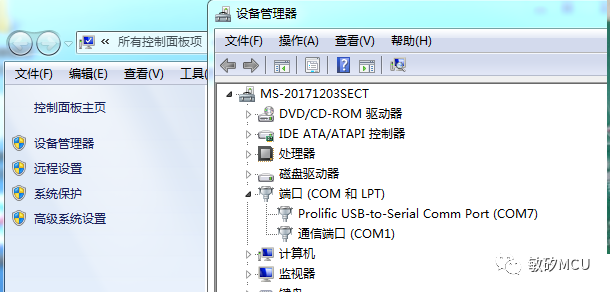

在实验前需要先确定U转串所使用的的串口号,通过windows的设备管理器中的端口(COM和LPT)查看我们的串口,比如本例中是COM7。

图8 串口端口号选择

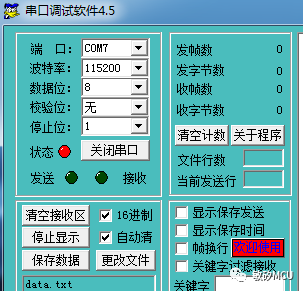

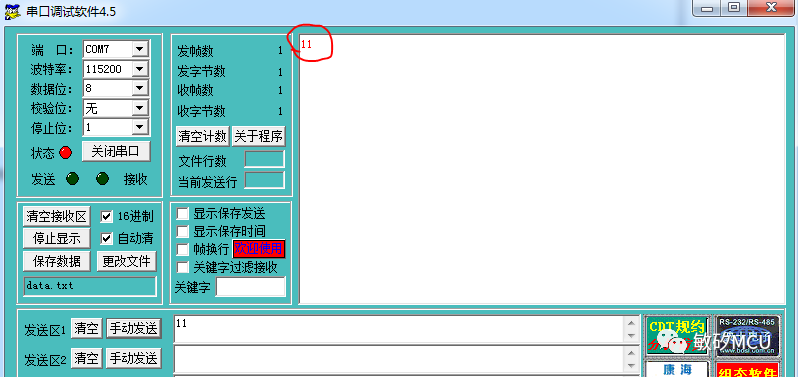

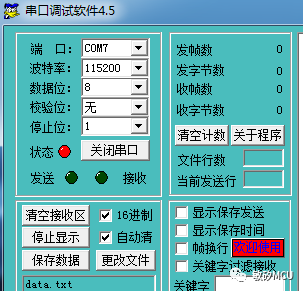

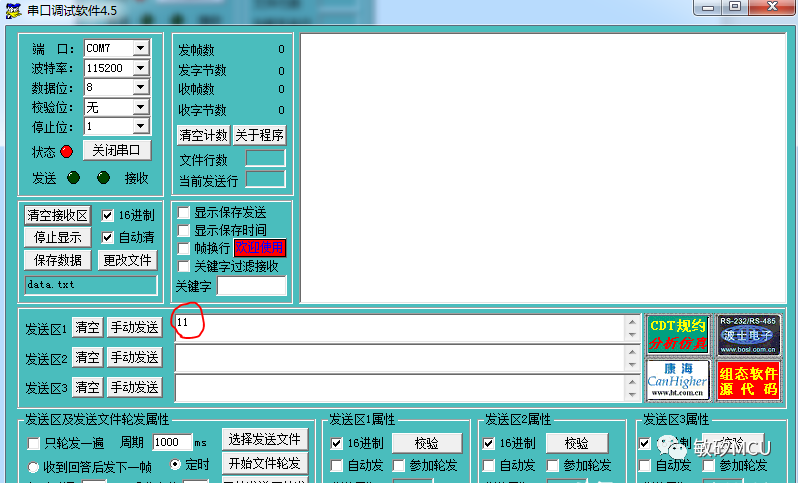

接下来打开串口上位机工具,本例使用的是“大傻串口工具”。按照程序中设置的串口参数配置好串口。端口选择COM7,波特率115200,数据位8位,无奇偶校验,1位停止位。最后点击打开串口即可。打开后如图所示:

图9 串口配置

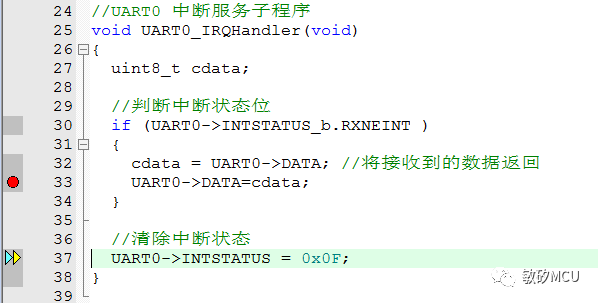

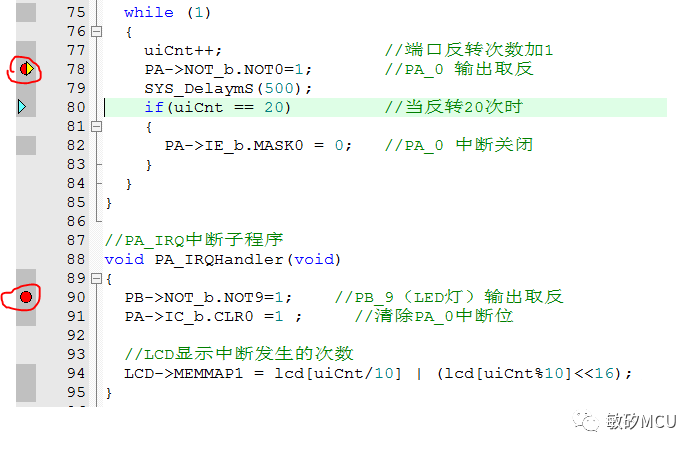

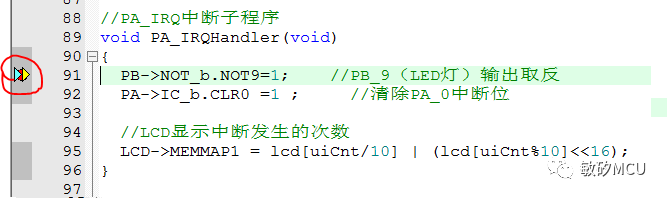

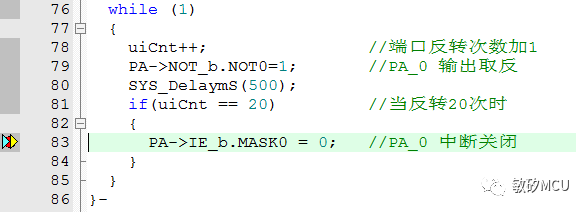

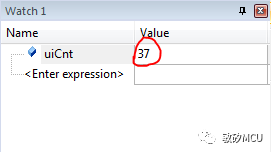

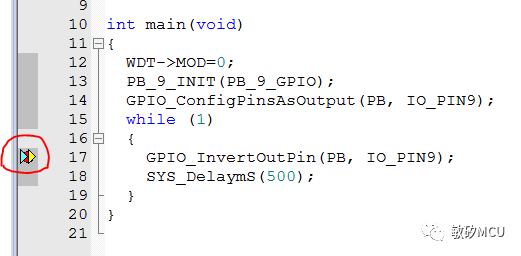

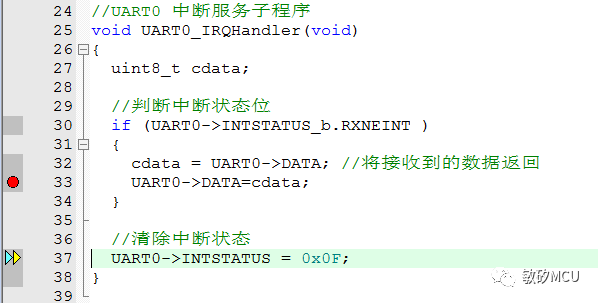

上位机环境配置好之后,接下里就可以下载并仿真程序了。首先我们在UART0_IRQ中断子程序中位置打上断点。随后全速运行程序。

图10 仿真界面

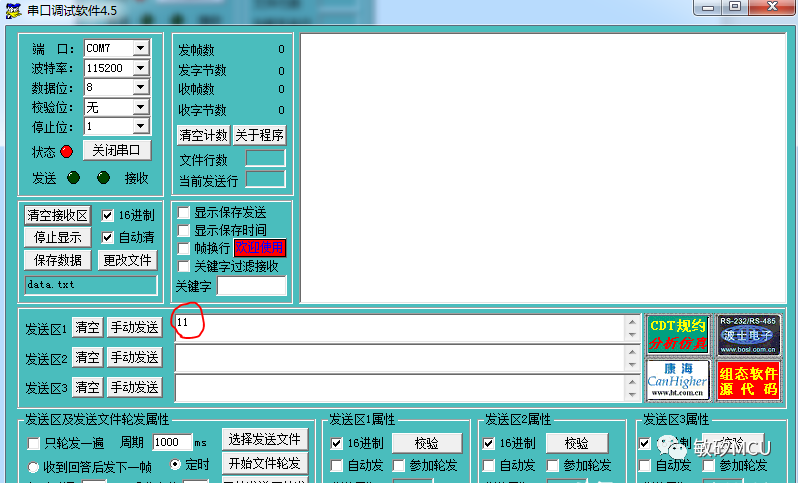

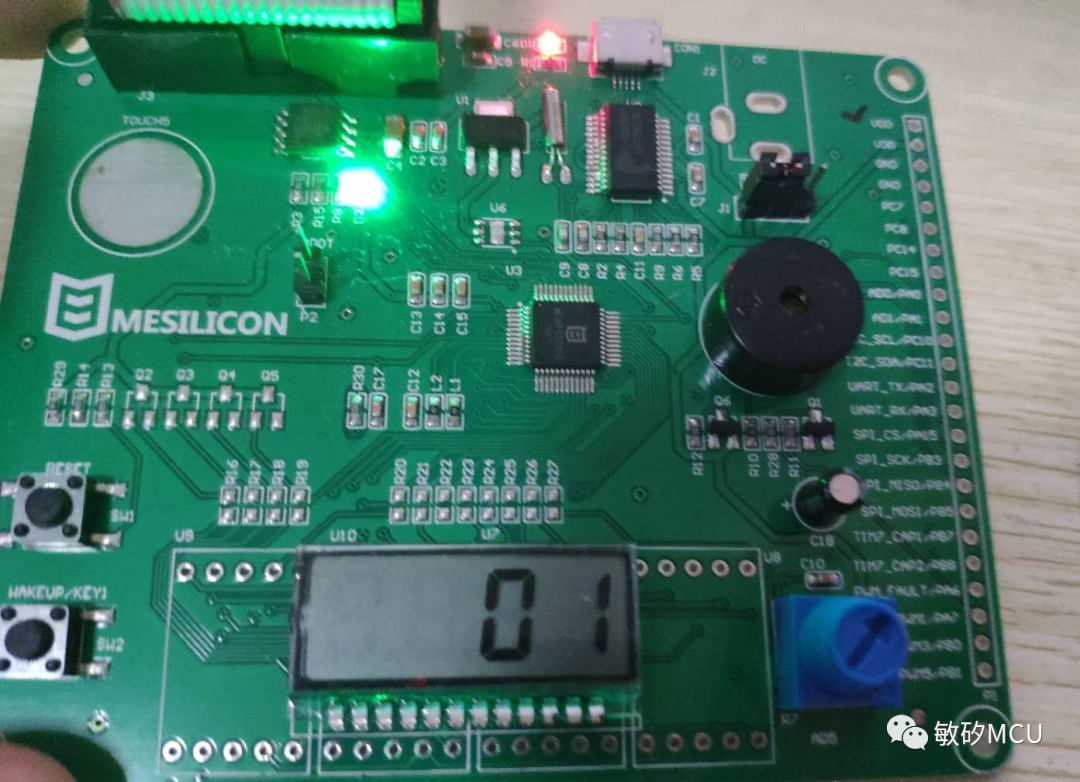

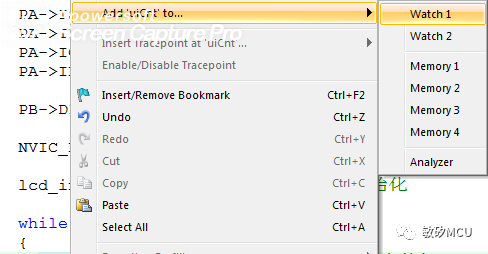

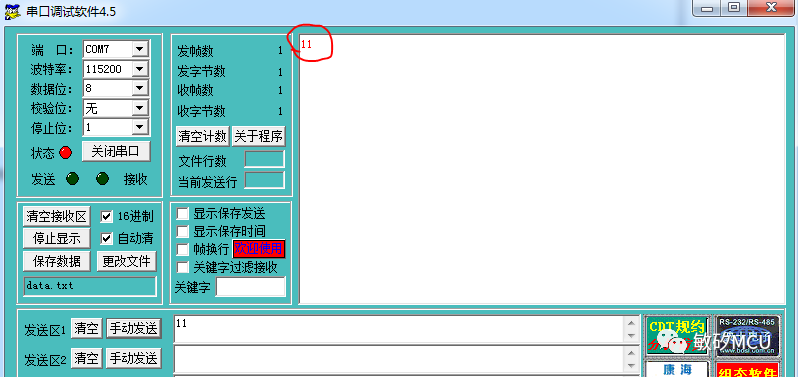

然后我们在上位机发送一个数据进行测试,例如发送一个字节0x11。这时候单片机便会进入串口中断服务程序,并且停止在断点处。这时候我们听过watch窗口看到接收的数据,就是0x11。

图11 数据发送

继续单步运行并退出中断服务程序,这时候我们再去看上位机,发现收到了单片机返回的数据。

图12 数据接收

来源:敏矽MCU

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。