时钟

本文提到的有以下内容:

• 时钟系统与总线矩阵

• SysTick系统定时器

• RTC实时时钟

• 看门狗定时器

• 通用定时器

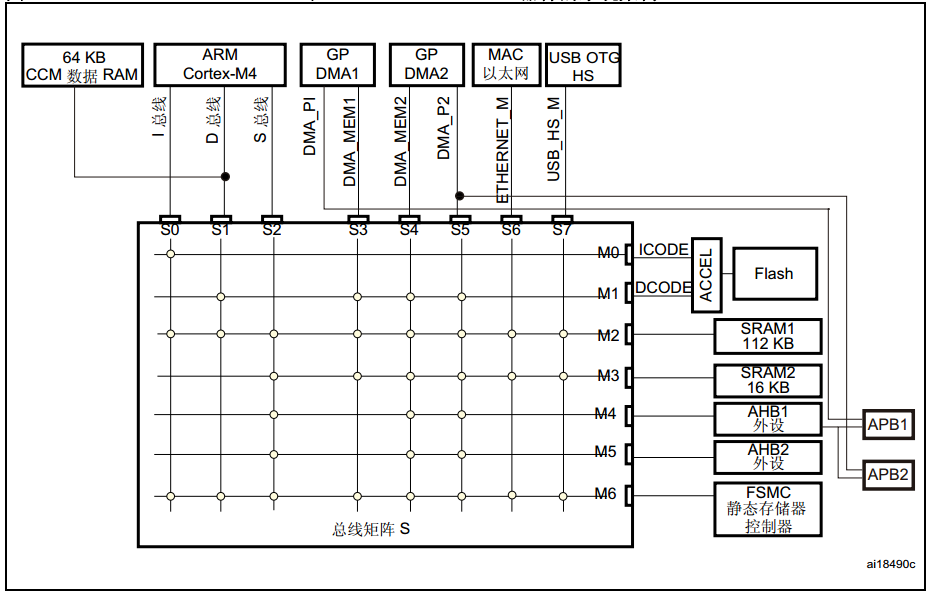

一、时钟系统与总线矩阵

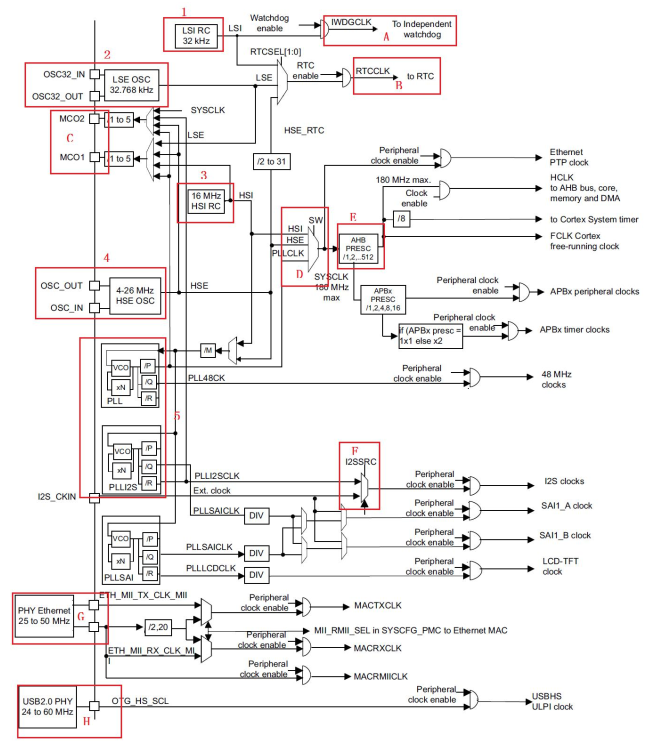

stm32F4的时钟树如下图所示:

在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

HSI是高速内部时钟,RC振荡器,频率为8MHz。

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

LSI是低速内部时钟,RC振荡器,频率为40kHz。

LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

我们在学习51单片机的时候,其内部是没有晶振的,而stm32是有的。stm32可以通过RCC(时钟控制寄存器)对时钟进行参数配置以及使能。我们还可以通过修改system_stm32f4xx.c文件,来配置上述时钟树上的一些分频、倍频参数,得到理想的频率。

在单片机系统中,CPU和总线以及外设的时钟设置是非常重要的,因为没有时钟就没有时序,组合电路需要好好理解清楚。我们先来看一下总线矩阵。

片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标

准片上结构。AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。二者分别适用于高速与相对低速设备的连接。

一般性的时钟设置需要先考虑系统时钟的来源,是内部RC还是外部晶振还是外部的振荡器,是否需要PLL。然后考虑内部总线和外部总线,最后考虑外设的时钟信号。遵从先倍频作为CPU时钟,然后在由内向外分频,下级迁就上级的原则。

二、SysTick系统定时器

SysTick—系统定时器是属于CM4内核中的一个外设,内嵌在NVIC中。系统定时器是一个24bit的向下递减的计数器,计数器每计数一次的时间为1/SYSCLK,一般我们设置系统时钟SYSCLK等于180M。当重装载数值寄存器的值递减到0的时候,系统定时器就产生一次中断,以此循环往复。

因为SysTick是属于CM4内核的外设,所以所有基于CM4内核的单片机都具有这个系统定时器,使得软件在CM4单片机中可以很容易的移植。

系统定时器一般用于操作系统,用于产生时基,维持操作系统的心跳。

一般用于系统内部运行以及延时函数。

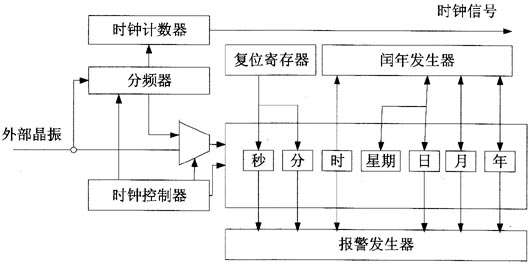

三、RTC实时时钟

RTC(Real-Time Clock)实时时钟为操作系统提供了一个可靠的时间,并且在断电的情况下,RTC实时时钟也可以通过电池供电,一直运行下去。

RTC通过STRB/LDRB这两个ARM指令向CPU传送8位数据(BCD码)。数据包括秒,分,小时,日期,天,月和年。RTC实时时钟依靠一个外部的32.768Khz的石英晶体,产生周期性的脉冲信号。每一个信号到来时,计数器就加1,通过这种方式,完成计时功能。

RTC实时时钟有如下一些特性:

1,BCD数据:这些数据包括秒、分、小时、日期、、星期几、月和年。

2,闰年产生器

3,报警功能:报警中断或者从掉电模式唤醒

4,解决了千年虫问题 (详见http://baike.baidu.com/view/9349.htm)

5,独立电源引脚RTCVDD

6,支持ms中断作为RTOS内核时钟

7,循环复位(round reset)功能

如图,RTC实时时钟的框架图,XTIrtc和XTOrtc产生脉冲信号,即外部晶振。传给2^15的一个时钟分频器,得到一个128Hz的频率,这个频率用来产生滴答计数。当时钟计数为0时,产生一个TIME TICK中断信号。时钟控制器用来控制RTC实时时钟的功能。复位寄存器用来重置SEC和MIN寄存器。闰年发生器用来产生闰年逻辑。报警发生器用来控制是否产生报警信号。

四、看门狗定时器

看门狗定时器又分为独立看门狗IWDG和窗口看门狗WWDG。

1、独立看门狗

独立看门狗IWDG其实是一个12位递减计数器,有故障时,计数器减到0,产生复位,无故障时,计数器减到0之前就刷新计数值(喂狗),不进行复位。其采用独立时钟,主要用于监视硬件错误(不受系统时钟影响)。

2、窗口看门狗

窗口看门狗WWDG其实是一个7位递减计数器,有计数上下限,下限位0x40,上限由用户指定,上下限之间刷新计数值则不复位,其他都复位。采用系统时钟,主要用于监视软件错误。

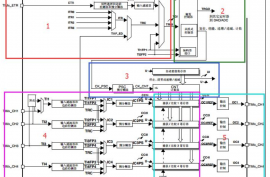

五、通用定时器

stm32的定时器有基本定时器、通用定时器和高级定时器。这里以通用定时器为例,其内部结构如下图所示,需要设置预分频系数,并不是直接使用APB1的时钟。

通用定时器的计数模式分为5种:

• 向上计数:计数器从0计数到自动装载值。

• 向下计数:从自动装载值计数到0。

• 向上向下计数(中心对齐计数):计数器从0计数到自动装载值,再从自动装载值计数到0,反复循环。

• 输入捕获:测量输入信号的脉宽、PWM波的占空比等。

• 输出比较:PWM波用的就是这种模式。

定时器的时间公式:T=((n-1)*(pre-1))/Tclk,其中n为计数值,pre为预分频系数,Tclk为定时器时钟。

为什么计数值和预分频系数要减一?因为计数是从0开始的,而预分频系数为0时,表示不分频。

定时器用于中断时,注意更新中断标志位。

转自: steed-博客

MSP430根据型号的不同最多可以选择使用3个振荡器。我们可以根据需要选择合适的振荡频率,并可以在不需要时随时关闭振荡器,以节省功耗。

这3个振荡器分别为:

(1)DCO 数控RC振荡器。

它在芯片内部,不用时可以关闭。DCO的振荡频率会受周围环境温度和MSP430工作电压的影响,且同一型号的芯片所产生的频率也不相同。但DCO的调节功能可以改善它的性能,他的调节分为以下3步:

a:选择BCSCTL1.RSELx确定时钟的标称频率;

b:选择DCOCTL.DCOx在标称频率基础上分段粗调;

c:选择DCOCTL.MODx的值进行细调。

(2)LFXT1 接低频振荡器。

典型为接32768HZ的时钟振荡器,直接连接在XIN与XOUT之间,此时振荡器不需要接负载电容。也可以接450KHZ~8MHZ的标准晶体振荡器,此时需要接负载电容.LXFT1产生的频率信号为ACLK.低速时钟需要上百毫秒的建立时间才能稳定下来.

(3)XT2 接450KHZ~8MHZ的标准晶体振荡器。

外部标准晶体振荡器接在XT2IN和XT2OUT之间,此时需要接负载电容,不用时可以关闭。

低频振荡器主要用来降低能量消耗,如使用电池供电的系统,高频振荡器用来对事件做出快速反应或者供CPU进行大量运算。

MSP430的3种时钟信号:

MCLK系统主时钟;

SMCLK系统子时钟;

ACLK辅助时钟。

(1)MCLK系统主时钟。除了CPU运算使用此时钟以外,外围模块也可以使用。MCLK可以选择任何一个振荡器所产生的时钟信号并进行1、2、4、8分频作为其信号源。

(2)SMCLK系统子时钟。供外围模块使用。并在使用前可以通过各模块的寄存器实现分频。SMCLK可以XT2CLK或者DCOCLK振荡器所产生的时钟信号并进行1、2、4、8分频作为其信号源。

(3)ACLK辅助时钟。供外围模块使用。并在使用前可以通过各模块的寄存器实现分频。但ACLK只能由LFXT1进行1、2、4、8分频作为信号源。可以作为后台时钟用来唤醒CPU.

(4)ACLK/N, ACK缓冲输出,他可以有ACL.1.2.4.8分频获得 ,且只能为外部所用.

PUC复位后,MCLK和SMCLK的信号源为DCO,DCO的振荡频率为800KHZ。ACLK的信号源为LFXT1。

MSP430内部含有晶体振荡器失效监测电路,监测LFXT1(工作在高频模式)和XT2输出的时钟信号。当时钟信号丢失50us时,监测电路捕捉到振荡器失效。如果MCLK信号来自LFXT1或者XT2,那么MSP430自动把MCLK的信号切换为DCO,这样可以保证程序继续运行。但MSP430不对工作在低频模式的LFXT1进行监测。

来源: 电子工程世界

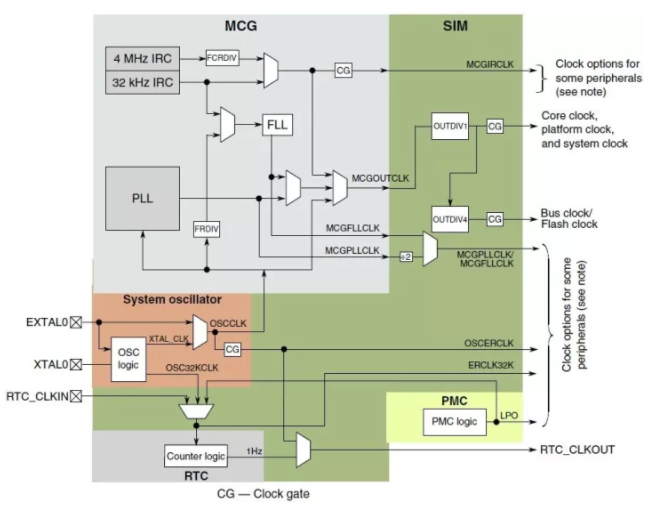

时钟模式的配置以及使用对MCU来说一直是最基础的东西,在何种情况下使用哪一种时钟模式是我们在使用MCU的过程中最常见的问题之一。

Kinetis系列微控制器具有复杂的时钟系统,时钟系统中多功能时钟发生器、锁相环、锁频环、晶振系统等功能模块相互之间的协调工作能为MCU以及各种外设模块提供稳定的时钟源。通过对KL25时钟系统的结构和配置方法的剖析,以及对多功能时钟发生器运行机制的梳理,提出了时钟源性能的测试方法以及各外设模块时钟源的选择方法。

可见,时钟的正确合理配置对于MCU以及各种外设模块来说是非常重要的,下面我将着重介绍八种模式的时钟如何正确配置。

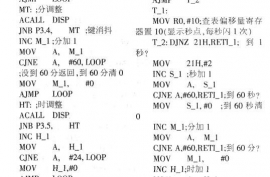

KL25芯片的时钟系统包含2路内部参考时钟以及1路外部参考时钟。内部参考时钟分为高频4MHz和低频32KHz,可作为MCU的时钟源或可选外设时钟MCGIRCLK。1路外部参考时钟通过系统振荡器利用外部引脚XTAL与EXTAL接入时钟系统,支持低频32KHz或高频3MHz~8MHz和8MHz~32MHz,其可作为MCU的时钟源或可选外设时钟OSCERCLK和ERCLK32K。

由上图可知,KL25时钟系统的内部参考时钟和外部参考时钟均接入到多功能时钟发生器MCG,通过MCG模块内部包含的一个锁频环FLL以及一个锁相环PLL可以实现对相应参考时钟倍频。锁相环FLL可以接收内外参考时钟作为时钟源,而锁相环PLL只能使用外部参考时钟。

通过MCG的各时钟信号会通过系统集成模块SIM分配到各个指定的系统功能模块上,同时SIM还提供了2个分频器OUTDIV1、OUTDIV4,通过不同分频使得在同一个MCGOUTCLK时钟源驱动的情况下生成系统以及总线时钟。

各种模式与工作态的关系:

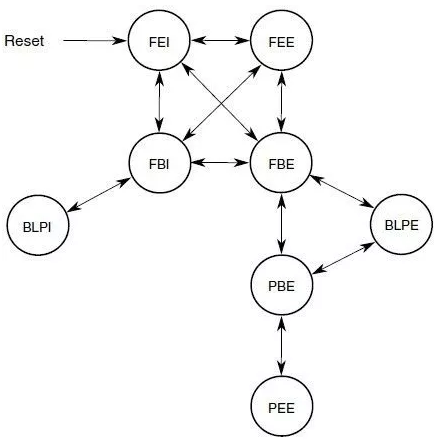

八种时钟模式相互转换示意图:

Kinetis系列MCU的时钟系统可以通过内外参考时钟将频率信号源接入到芯片,由多功能时钟发生器MCG为各个功能模块提供所需要的时钟源,利用CG等门控模块启停系统功能模块时钟和时钟分配机制为各功能模块在满足其工作要求的前提下选择相对比较低的模块工作频率,这样既可以做到功能模块的正常工作以及保证功耗为最低。

来源: 周立功单片机

本文针对用单片机制作电子钟或要求根据时钟启控的控制系统时,出现的校准了的电子时钟的时间竟然变快或是变慢了的情况而提出的一种解决方案。

单片机应用中,常常会遇到这种情况,在用单片机制作电子钟或要求根据时钟启控的控制系统时,会突然发现当初校准了的电子时钟的时间竟然变快或是变慢了。

于是,尝试用各种方法来调整它的走时精度,但是最终的效果还是不尽人意,只好每过一段时间手动调整一次。那么,是否可使时钟走时更精确些呢?现探讨如下:

一、误差原因分析

1、单片机电子时钟的计时脉冲基准,是由外部晶振的频率经过12分频后提供的,采用内部的定时,计数器来实现计时功能。所以,外接晶振频率的精确度直接影响电子钟计时的准确性。

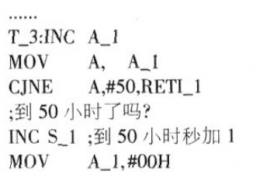

2、单片机电子时钟利用内部定时,计数器溢出产生中断(12MHz晶振一般为50ms)再乘以相应的倍率,来实现秒、分、时的转换。大家都知道,从定时,计数器产生中断请求到响应中断,需要3_8个机器周期。定时中断子程序中的数据人栈和重装定时,计数器的初值还需要占用数个机器周期。此外。从中断人口转到中断子程序也要占用一定的机器周期。例如:

从上述程序可以看出,从中断人口到定时/计数器初值的低8位装入需要占用2+2+2=6个机器周期。所以,在编程时一般会把这6个机器周期加入定时/计数器的初值中。但是,从定时,计数器溢出中断请求到执行中断需要几个机器周期(3~8个机器周期)。就很难确定准确值,正是这一原因导致了电子时钟计时的不准。

二、解决方法

1、采用高精度晶振方案

虽然采用高精度的晶振可以稍微提高电子钟计时的精确度,但是晶振并不是导致电子钟计时不准的主要因素,而且高精度的晶振价格较高,所以不必采用此方案。

2、动态同步修正方案

从程序人手,采用动态同步修正方法给定时,计数器赋初值。动态同步修正方法如下:由于定时,计数器溢出后,又会从O开始自动加数,故在给定时/计数器再次赋值前,先将定时,计数器低位(TLO)中的值和初始值相加,然后送人定时,计数器中,此时定时,计数器中的值即为动态同步修正后的准确值。具体程序如下:

采用此种方法后,相信制作的电子时钟的精度已有提高了。

3、自动调整方案

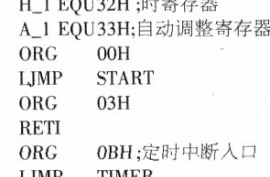

采用同步修正方案后,电子时钟的精度虽然提高了很多,但是由于晶振频率的偏差和一些其他未知因素的影响(同一块电路板、同样的程序换了一片单片机后,走时误差不一样,不知是何原因),时间长了仍然会有积累误差。为此,可采用自动调整方案。实际上是一种容错技术。其自动调整原理为:实测出误差Is所需的时间,然后每隔这样一段时间后就对秒进行加“1”或减“1”调整。例如:电子钟每过50小时就慢1秒,其自动调整程序如下:

以下是一个完整实例:

结语

使用此方法调整较费时间,但效果非常好。经实验,一次调整可/以将月误差控制在Is左右,如按此方法再次测出误差Is所需的天数并进行二次调整,其精度会更高。

来源:广电电器网(该文章仅供学习参考使用,版权归作者所有。)