时钟

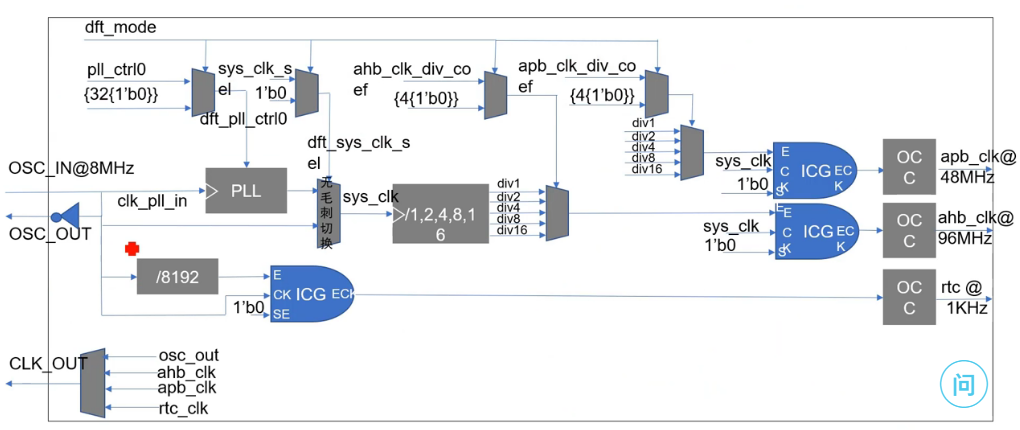

1 CRG的SPEC参考

1.1 时钟设计需求

(1)生成AHB时钟,APB时钟,RTC时钟;

(2)AHB最高时钟频率为98MHz;

(3)APB时钟为AHB同步时钟,且可以配置AHB时钟的1/2,1/4,1/8;

(4)RTC时钟单独控制时钟,时钟频率1KHz;

(5)各外设时钟可以单独门控,满足低功耗要求。

1.2 时钟设计要点

(1)DFT可控,隔离,可观测。

(2)上电工作外部参考时钟,PLL稳定后,时钟自动切换。

(3)低功耗要求,在系统不工作时,时钟自动关闭。

(4)各个外设时钟均能门控。

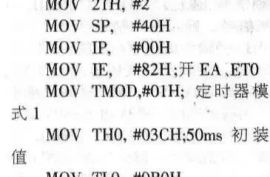

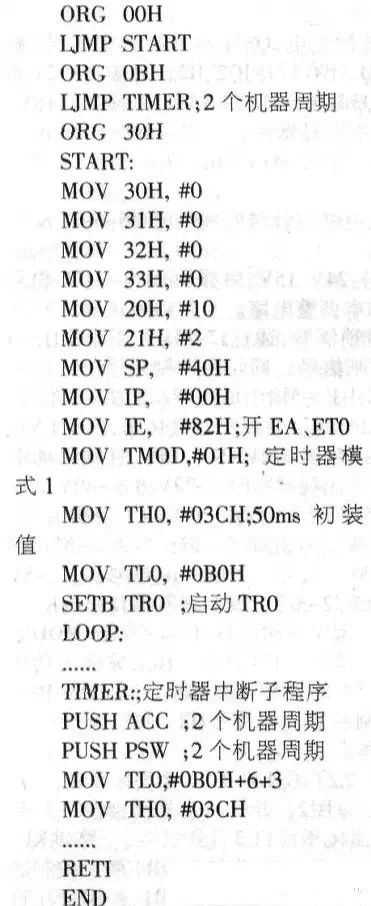

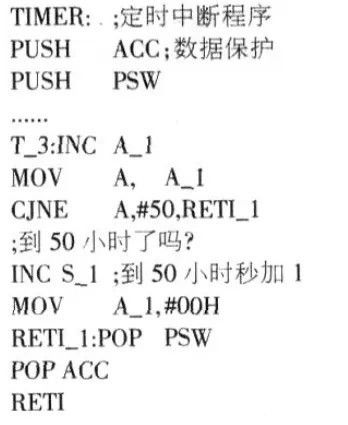

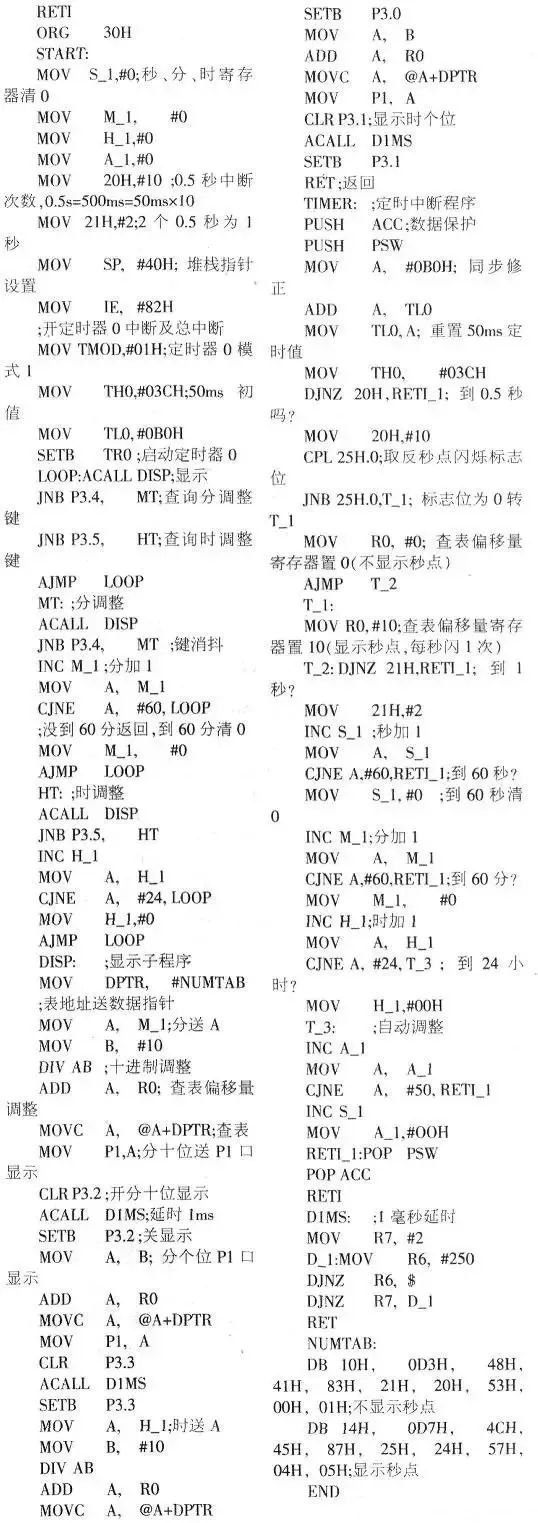

1.3 时钟设计电路

看上图,首先进来的是8M时钟,给PLL倍频。OSC_OUT是OSC_IN取反得到的,这是外部时钟要求的。经过无毛刺切换后,就产生sys_clk系统时钟,然后进入一个分频模块;分频之后的时钟进入ICG,产生apb和ahb时钟。这个ICG看做是一个buffer,对sys_clk做门控,时钟路径时钟是sys_clk系统时钟,注意这里出来是不是分频时钟,而是sys_clk出来的,分频时钟只是控制作用而已。

2 时钟的无毛刺切换

2.1 毛刺的产生

两个时钟频率可以彼此完全无关,或者它们可以是彼此的倍数。在任何一种情况下,都有可能在切换时在时钟线上产生毛刺。时钟线上的毛刺对整个系统是危险的,因为它可能被某些寄存器解释为捕获时钟边沿而被其他寄存器忽略。毛刺的处理分为两种,当时钟是彼此的倍数时是一种,完全无关的两个时钟处理又是一种。

2.2 倍数关系的时钟毛刺解决方案

这一篇文章很值得参考!

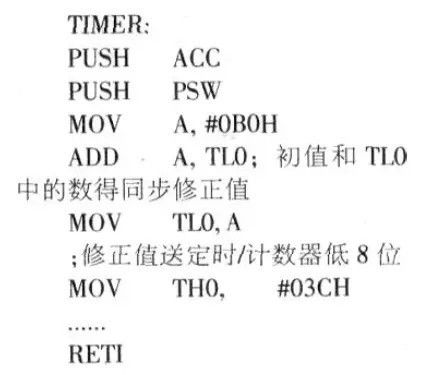

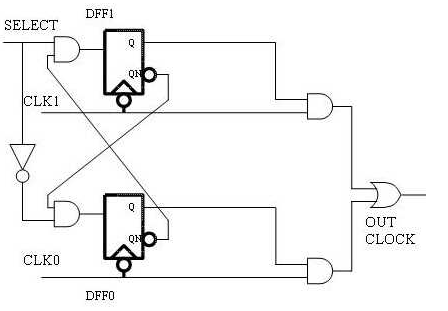

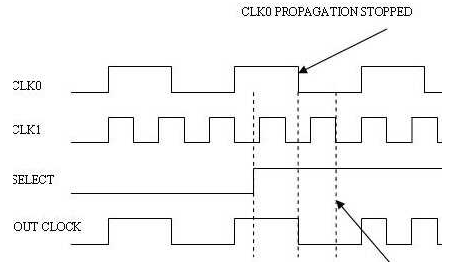

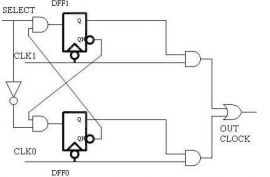

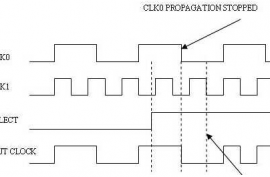

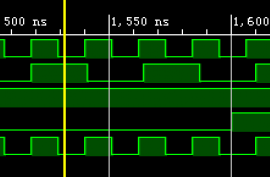

其原理是,先gating住之前选择的时钟,然后再放开将要选择的时钟。下图显示了防止源时钟相互倍数的时钟开关输出出现毛刺的解决方案。在每个时钟源的选择路径中插入一个负边沿触发的D触发器。

2.3 针对无关时钟源的毛刺保护

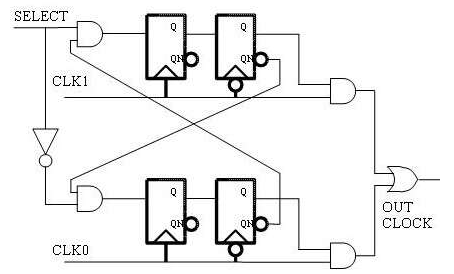

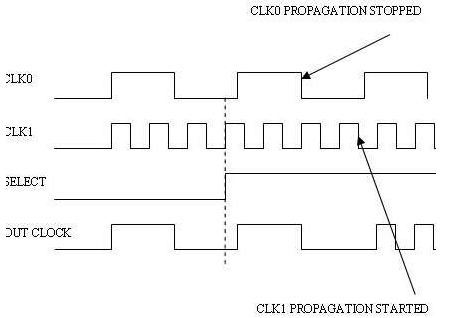

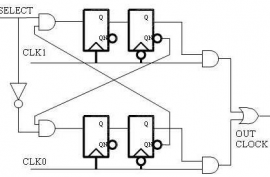

先前避免时钟开关输出处的毛刺的方法需要两个时钟源彼此的倍数,在该实现中没有处理异步信号的机制。当两个时钟源彼此完全无关时,异步行为的源可以是SELECT信号或从一个时钟域到另一个时钟域的反馈。同步器只是两级触发器,其中第一级通过锁定数据来帮助稳定数据,这一级可以用上升沿,也可以用下降沿,用上升沿是为了节省时间然后将数据传递到下一级,后一级的DFF必须使用clock下降沿,因为是用AND门进行gating。

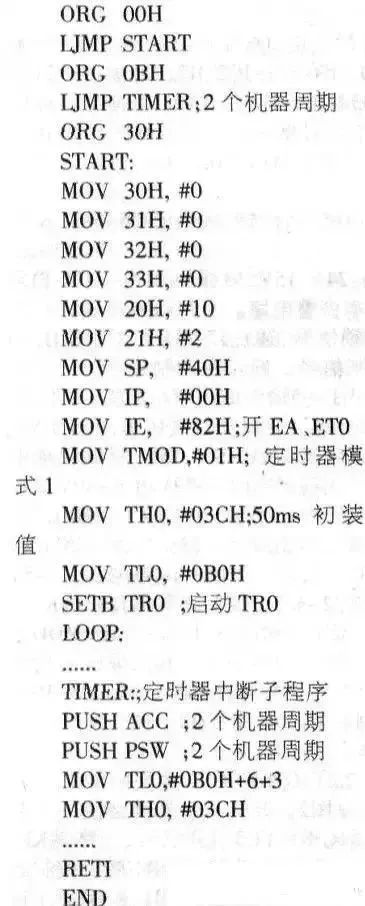

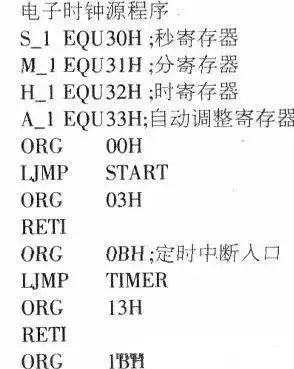

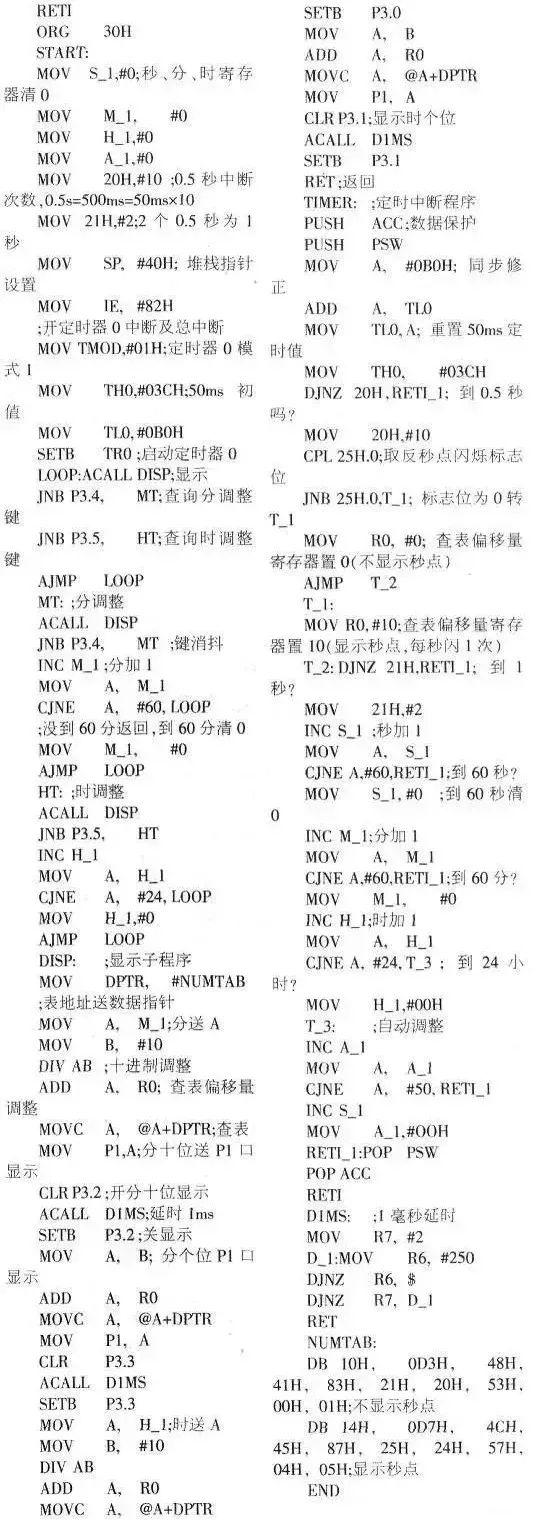

2.4 RTL代码

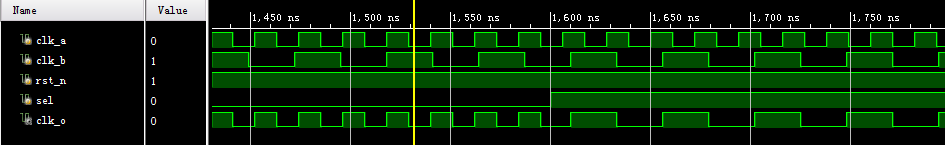

module clk_sw(

input wire clk_a,

input wire clk_b,

input wire rst_n,

input wire sel,

output wire clk_o

);

reg clk_a_en ;

reg clk_b_en ;

always @(posedge clk_a or negedge rst_n) begin

if(~rst_n)

clk_a_en <= 1'b0 ;

else

clk_a_en <= ~sel & ~clk_b_en ;

end

always @(posedge clk_b or negedge rst_n) begin

if(~rst_n)

clk_b_en <= 1'b0 ;

else

clk_b_en <= sel & ~clk_a_en ;

end

assign clk_o = (clk_a & clk_a_en) | (clk_b & clk_b_en) ;

endmodule本文转自:博客园 - yiwenbo,转载此文目的在于传递更多信息,版权归原作者所有。

概念基础:

STM32时钟系统基本一致,不同系列之间有细微差别。此文档主要针对STM32F446的时钟系统进行介绍。

1. 时钟树概述

① 为何不是采用一个系统时钟?如51

因为STM32本身非常复杂,外设非常多,但是并非所有外设都需要系统时钟这么高的频率,比如看门狗和RTC只需要几十K的时钟即可。同一个电路,时钟越快,功耗越大,同时抗电磁干扰能力也会越弱,所以对于较为复杂的MCU一般采用多时钟源的方法来解决这些问题。

② 主要时钟源:

5个最主要的时钟源:

高速时钟源:HSI、HSE、PLL

低速时钟源:LSI、LSE

其中PLL实际又分为3个时钟源:主PLL、I2S部分专用PLLI2S、SAI部分专用PLLASI。

详解:

LSI是低速内部时钟,RC振荡器,频率为32K,供独立看门狗和自动唤醒单元使用。

LSE是低速外部时钟,接频率为32.768Khz的石英晶体,这个主要是RTC的时钟源。

HSE是高速外部时钟,频率范围为4Mhz-26Mhz,可以直接作为系统时钟或PLL输入。

HSI是高速内部时钟,RC振荡器,频率为16Mhz,可以直接作为系统时钟或PLL输入。

PLL为锁相环倍频输出,STM32F4有三个PLL:

a、 主PLL由HSE或HSI提供时钟信号,并具有两个不同的输出时钟。

第一个输出PLLP用于生成高速的系统时钟(最高180Mhz)

第二个输出PLLQ为48M,用于USB OTG FS时钟,随机数发生器的时钟和SDIO时钟。

b、 第一个专用PLL(PLLSAI)用于生成精确时钟,用作SAI输入时钟。Q是SAI时钟分频系数。P可以生成PLL48CLK用于给USB FS或SDIO提供48M时钟。

c、 第二个专用PLL(PLLI2S)用于生成精准时钟,在I2S和SAI上实现高品质音频性能。R是I2S时钟的分频系数,Q是SAI时钟的分频系数。

2. 常用时钟源选择

① 看门狗时钟:看门狗时钟只能是低速的LSI时钟,32Khz。

② RTC时钟源:可以选择LSI(32Khz)、LSE(32.768Khz)、HSE分频后提供(2-31分频)

③ 系统时钟SYSCLK:可选择HSE、HSI和PLL

④ USB高速设备会有外部PHY提供60Mhz

⑤ NOTE:

在上述的很多时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等。

APB1是外设低速总线

APB2是外设高速总线

一般时钟总线是设备总线的2倍

时钟主频可以设置为168Mhz,通过设置Over-driver模式可以超频到180Mhz

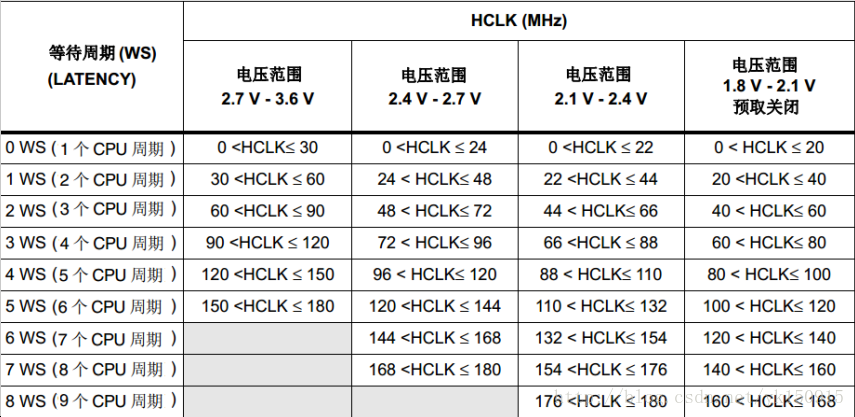

FLASH Latency 延时配置参考:

3. 时钟源使能和配置

在配置好时钟系统之后,如果我们要使用某些外设,例如GPIO、ADC,还要使能这些外设时钟,如果在使用外设之前没有使能外设时钟,这个外设是不可能正常运行的。

IO引脚复用器和映射

一个GPIO如果可以复用为内置外设的功能引脚,那么这个GOIO作为内置外设使用的时候,就叫做复用。

4. 寄存器配置

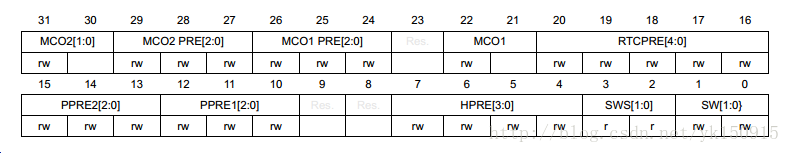

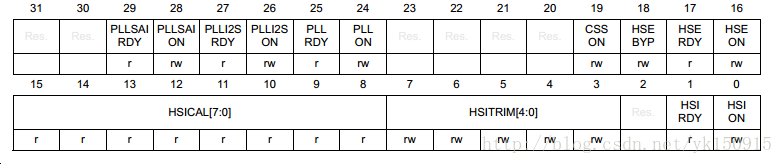

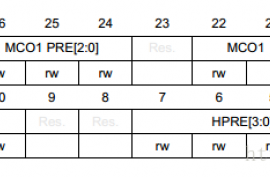

① RCC_CFGR,时钟配置寄存器

Bit2 bit3代表使用的时钟源,具体可查参考手册,系统刚上电时默认为内部HSI。

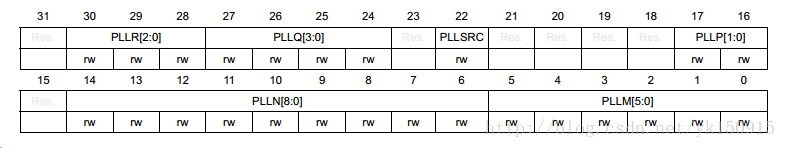

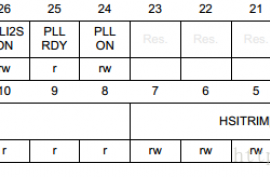

② RCC_PLLCFGR,PLL时钟配置寄存器

上电默认情况为HSI做为主PLL和I2SPLL的时钟入口。

③ RCC_CR,RCC时钟控制寄存器

通过Bit16可以切换为外部晶振。在时钟初始化的时候被调用。时钟切换之后,根据时钟设置逻辑,如果外部晶振使能了,则等待外部晶振正常起震。起震后查看RCC_CFRG寄存器,当前使用的还是HSI。下一步需要判断程序中是否要使用PLL,若使用,则继续进行PLL配置。

配置结束PLL的各种分频后,一块进行寄存器配置。此时再切换到外部HSE工作。

时钟配置过程:

(1)AHB配置预分频,得到HCLK时钟,分频值写入RCC_CFGR bit4-bit7

(2)系统时钟配置 RCC_CFGR bit0-bit1

(3)检查系统时钟状态是否切换成功 RCC_CFGR bit2-bit3

(4)APB1、APB2配置预分频,得到PCLK1、PCLK2时钟RCC_CFGR bit10-bit15

(5)更新系统全局变量SystemCoreClock

5. I2S时钟配置

(1)选择I2S外设的时钟源

(2)配置各项时钟分频系数,一般情况下使用PLLI2SR时钟

(3)计算时钟分频,需要在PLLI2SR上获得需要的48K

下列公式为参考手册提供:

When the master clock is generated (MCKOE in the SPIx_I2SPR register is set):

fS = I2SxCLK / [(16*2)*((2*I2SDIV)+ODD)*8)] when the channel frame is 16-bit wide

fS = I2SxCLK / [(32*2)*((2*I2SDIV)+ODD)*4)] when the channel frame is 32-bit wide

When the master clock is disabled (MCKOE bit cleared):

fS = I2SxCLK / [(16*2)*((2*I2SDIV)+ODD))] when the channel frame is 16-bit wide

fS = I2SxCLK / [(32*2)*((2*I2SDIV)+ODD))] when the channel frame is 32-bit wide

将计算额I2SDIV和奇数值ODD写入相应寄存器。

此例中,I2SxCLK为192MHz,使用48K时可以被整除,时钟准确,但是96K时不能被整除,造成时钟偏移。所以若需要进行I2S时钟动态调节,需要好好计算I2SxCLK。

版权声明:本文为CSDN博主「yk150915」的原创文章,

遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/yk150915/article/details/79112766

STM32的时钟系统分析

demi 在 提交

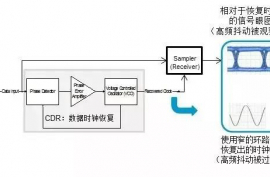

对于高速的串行总线来说,一般情况下都是通过数据编码把时钟信息嵌入到传输的数据流里,然后在接收端通过时钟恢复把时钟信息提取出来,并用这个恢复出来的时钟对数据进行采样,因此时钟恢复电路对于高速串行信号的传输和接收至关重要。

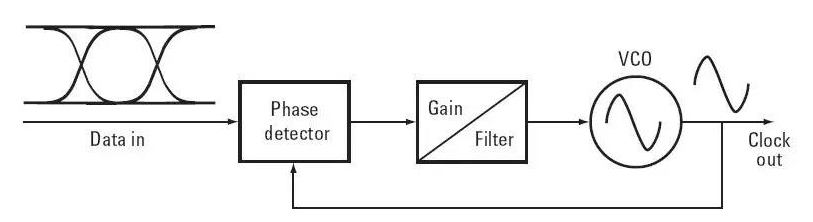

CDR电路原理

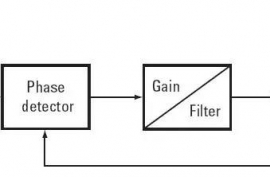

时钟恢复的目的是跟踪上发送端的时钟漂移和一部分抖动,以确保正确的数据采样。时钟恢复电路(CDR:Clock Data Recovery)一般都是通过PLL(Phase lock loop)的方式实现,如下图所示。

输入的数字信号和PLL的VCO(Voltage-controlled oscillator,压控振荡器 )进行鉴相比较,如果数据速率和VCO的输出频率间有频率差就会产生相位差的变化,鉴相器对这个相位误差进行比较并转换成相应的电压控制信号,电压控制信号经过滤波器滤波后产生对VCO的控制信号从而调整VCO的输出时钟频率。

使用滤波器的目的是把快速的相位变化信息积分后转换成相对缓慢的电压变化以调整VCO的输出频率,这个滤波器有时又称为环路滤波器,通常是一个低通的滤波器。通过反复的鉴相和调整,最终VCO的输出信号频率和输入的数字信号的变化频率一致,这时PLL电路就进入锁定状态。

环路带宽对眼图、抖动测量的影响

值得注意的是,在真实的情况下,输入的数字信号并不是一个纯净的信号,而是包含了不同频率成分的抖动。对于低频的抖动来说,其造成的是数据速率的缓慢变化,如果这个缓慢变化的频率低于环路滤波器的带宽,输入信号抖动造成的相位变化信息就可以通过环路滤波器从而产生对VCO输出频率的调整,这时VCO的输出时钟中就会跟踪上输入信号的抖动。

而如果输入信号中抖动的频率比较高,其造成的相位变化信号不能通过环路滤波器,则VCO输出的时钟中就不会有随输入信号一起变化的抖动成分,也就是说输入信号中的高频抖动成分被PLL电路过滤掉了。

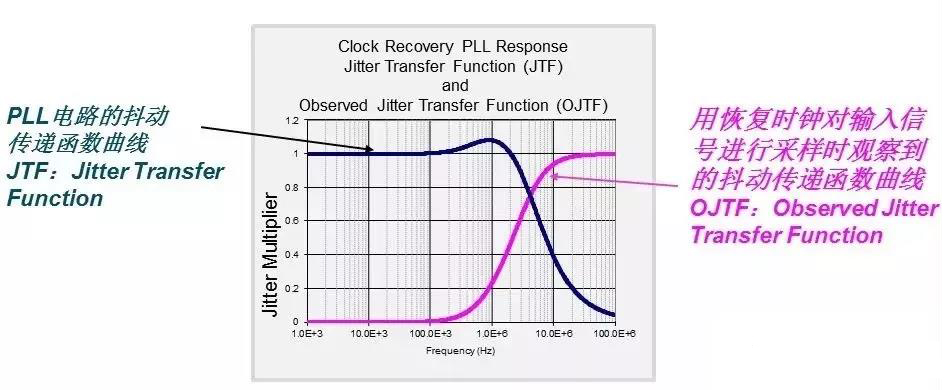

如下图所示,我们通常会用PLL电路的JTF(Jitter Transfer Function,抖动传递函数)曲线描述PLL电路对于不同频率抖动的传递能力。JTF曲线通常是个低通的特性,反映了PLL电路对于低频抖动能很好跟踪而对高频抖动跟踪能力有限的特性。

对于低频的抖动,PLL电路能够很好地跟踪,恢复出来的时钟和被测信号一起抖动。如果接收端的芯片用这个恢复时钟为基准对输入信号进行采样,由于此时时钟和被测信号一起抖动,所以这种低频的抖动不会被观察到,对于数据采样的建立保持时间也没有太大影响。

相反地,高频的抖动会被PLL电路过滤掉,因此输出的时钟里不包含这些高频的抖动成分。如果用这个时钟对数据信号进行采样,就会观察到输入信号里明显的抖动。接收端用恢复时钟进行采样时能够看到的抖动与抖动频率间的关系有时我们会用OJTF(Observed Jitter Transfer Function,观察到的抖动传递函数)曲线来描述,其随频率的变化曲线正好JTF曲线相反。

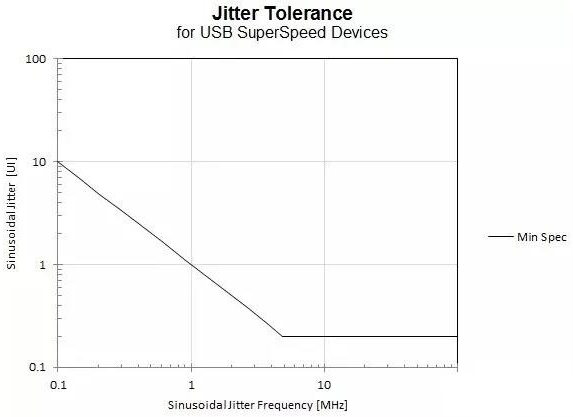

正因为时钟恢复电路对于低频抖动的跟踪特性,因此很多高速串行总线的接收芯片对于低频抖动的容忍能力会远远超过对高频抖动的容忍能力。下图是USB3.0总线对于接收端芯片对于不同频率抖动容忍能力的要求的一条曲线,可以看到其对低频的容忍能力非常大,甚至可以远超过1个UI(数据比特宽度)。

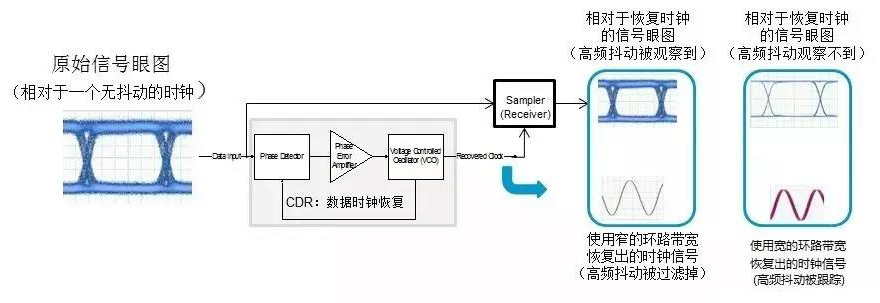

时钟恢复电路的PLL的环路带宽设置不同,对于不同频率抖动跟踪能力也不一样。一般情况下,PLL的带宽设置越窄,恢复出来的时钟越纯净,但是对于抖动的跟踪能力越弱,用这个时钟为基准对数据做采样时看到的信号上的抖动会越多,看到的信号的眼图会越恶劣。

相反,如果PLL的带宽设置越宽,对于抖动的跟踪能力越强,恢复出来的时钟和信号的抖动越接近,用这个时钟为基准对数据做采样时看到的信号上的抖动会越少,看到的信号的眼图会越好。下图反映出的就是不同的PLL带宽设置对于恢复时钟抖动和以这个恢复时钟为基准对信号进行采样时看到的眼图的情况。

转自:至秦单片机