MCU AI/ML - 弥合智能和嵌入式系统之间的差距

本文将探讨MCU技术和AI/ML的交集,以及它如何影响低功耗边缘设备。同时将讨论在电池供电设备的MCU上运行人工智能的困难、创新和实际应用场景。

本文将探讨MCU技术和AI/ML的交集,以及它如何影响低功耗边缘设备。同时将讨论在电池供电设备的MCU上运行人工智能的困难、创新和实际应用场景。

正当人们尽情享受智能化带来的种种便利的同时,殊不知那些隐藏在边缘设备中的一些漏洞随时有可能诱发严重的安全隐患。

通用MCU、安全微控制器和车规微控制器都集成新后量子密码加密算法

在本篇博文中,我们将 探讨各类应用如何从 I3C 协议中受益,并介绍作为嵌入式系统解决方案而全新推出的 PIC18-Q20 单片机(MCU)。

人工智能(AI)和机器学习(ML)是使系统能够从数据中学习,进行推断并随着时间的推移提高其性能的关键技术。这些技术通常用于大型数据中心和功能强大的GPU,但是将它们部署在资源有限的设备(如微控制器MCU)上的需求越来越大。

德州仪器 (TI) 今日推出可扩展的 Arm® Cortex®-M0+ 微控制器 (MCU) 产品系列,进一步扩大德州仪器广泛的模拟和嵌入式处理半导体产品组合。该产品系列具有丰富的计算、引脚排列、存储器和集成模拟选项。

作为Microchip Technology解决方案的全球授权分销商,贸泽备有其新一代MCU、混合信号、模拟和闪存IP解决方案,以降低各类应用的产品开发风险并加快上市。贸泽还为工程师提供了电子书等丰富的Microchip资源,为设计提供支持。

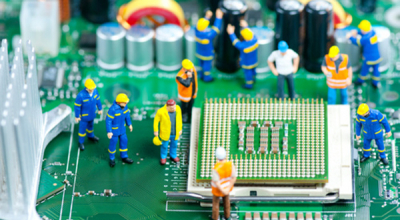

从规范完善的开发周期到严格执行和系统检查,开发高可靠性嵌入式系统的技术有许多种。本文介绍了7个易操作且可以长久使用的技巧,它们对于确保系统更加可靠地运行并捕获异常行为大有帮助。

本文主要介绍嵌入式系统的一些基础知识,希望对各位有帮助。

开发人员可以采用几种技术来简化保护系统的任务。Silicon Labs(亦称“芯科科技”)是ioXt联盟(ioXt Alliance)的创始成员之一。ioXt联盟是一个由行业主导的倡议,通过业内各个领域的合作伙伴协力创建物联网安全规范,并已经制訂了8项关键原则。