C语言操作寄存器的常见手法

使用C语言对寄存器赋值时,常常需要用到C语言的位操作方法。

使用C语言对寄存器赋值时,常常需要用到C语言的位操作方法。

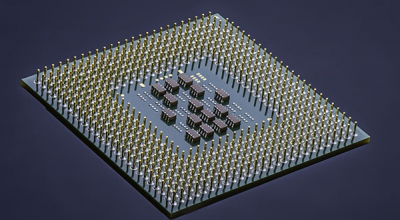

使用寄存器可以直接控制硬件,这个在早期的单片机(比如51、MSP430等)特别明显,大多数都是直接寄存器编程。

本应用笔记用于演示如何在应用中利用16 位配置寄存器设置数据保护。

在对某些不容易复现的问题进行代码调时,需要观察内部时钟的情况,但往往代码之前并没有使能 MCO 功能,在这种情况下就可以使用寄存器直接配置来输出内部时钟到GPIO 脚位上进行观察和测试。下面的例子就是在调试 STM32G474 很难复现的一个问题,调试暂停时,通过 PC 端调试工具直接更改寄存器配置来使能 MCO 功能输出 SYSCLK 到 GPIO 口的方法。

寄存器写保护功能可防止重要寄存器因软件错误而被覆盖。使用保护寄存器(PRCR)设置要保护的寄存器。表9列出了PRCR位与要保护的寄存器之间的关联。

某客户测试 STM32H753xi 板子上的 ECC 功能,用于监控 AXI-SRAM 区域,但不是很明白 RAMECC FAR 寄存器在 RM0433 中的描述, “Bits 31:0 FADD[31:0]: ECC error failing address”。

Cortex-M3拥有R0~R15通用寄存器和一些特殊功能寄存器。R0~R12这些通用寄存器,复位初始值都是不可预料的。

要操作 STM32寄存器,我们就需要使用 C 语言对其封装,这部分程序我们都放在 stm32f10x.h中。

我们知道 STM32 有很多寄存器,看起来特别费劲,当然如果通过前面的直接查看寄存器值的方法确实可以观察数据,但在这里我要介绍一个特别方便的查看方式。

库函数和寄存器操作的区别可能和 C 语言与汇编语言的区别差不多吧,都是跟效率有关,但有时候效率并不是唯一指标。