什么是复位电路?

复位电路在单片机小系统中很常见,今天我们就探讨下单片机阻容复位电路的构成、特点和改进方法,本文内容选自龙顺宇老师的新书 《深入浅出STC8增强型51单片机进阶攻略》 。

如果朋友们学习过《数字电子技术》这门课程的相关内容就肯定知道触发器和时序逻辑电路章节中必学的 初态 和 次态 问题,简单来说就是需要明确电路之前的状态才能推导出后面的状态,由此可见,在数字电路(特别是时序电路)中一个已知的初始状态有多么重要。

我们学习的单片机其实就是个数字/模拟的混合系统,很多片内资源和相关寄存器都需要一个默认的起始状态。

我们现在讲的“复位”,其作用就是通过相关电路产生“复位信号”让单片机能在上电后或者运行中恢复到默认的起始状态。

“复位”动作之后单片机会产生一系列的重置操作,例如I/O口默认的模式和状态、相关寄存器的默认取值、所有标志位的状态重置、通信/定时相关的数据内容设定等等。

由此可见, 复位的意义就是让单片机相关单元进行初始重置且程序从内存起始地址重新执行 。

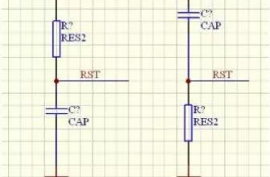

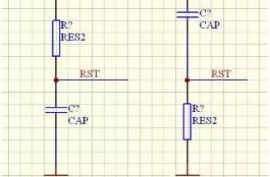

要让单片机正确复位就需要在RST引脚(等同于RESET引脚)上产生符合复位要求的有效信号,有的单片机需要高电平复位信号,有的则需要低电平复位信号。

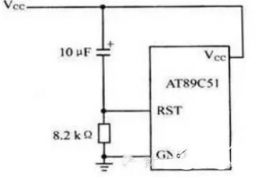

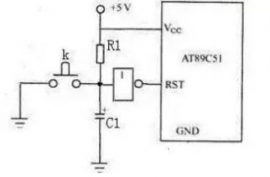

我们以经典51单片机高电平复位为例,单片机正常运行时RST引脚应保持低电平,当需要复位时应拉高RST引脚的电平,并维持“系统时钟源、内部电路单元稳定周期+2个机器周期”的时间长度( 为保证有效复位,复位信号应持续20至200ms为宜 )。

我们知道,在12T型单片机中,1个机器周期等于12个时钟周期,时钟周期其实就是振荡周期,比如晶振频率是12M,振荡周期就是1/12000000秒,由此可见,在设计具体复位电路时需要考虑单片机工作时钟频率后再去匹配复位电路的相关参数。

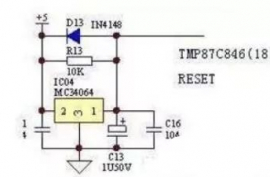

在早期的51单片机产品中,复位信号一般是由外部复位电路产生,所以很多经典的单片机原理类书籍将复位电路称作最小系统的必要组成,随着单片机技术的不断发展,很多单片机不再单独拿出一个RST引脚仅做复位之用,而是在晶圆设计时集成了 片内上电复位POR(Power On Reset)电路 ,很多单片机就都具备片上POR电路,POR电路在芯片上电后会产生一个内部复位脉冲并使器件保持静态,直至电源电压达到稳定阈值后再释放复位信号。

这样一来,用户就可以省略外部复位电路将RST引脚闲置或者当做普通I/O使用。

如果读者朋友们实际应用的单片机不具备片上POR电路也没事,我们可以搭建符合复位要求的外置电路产生复位信号。

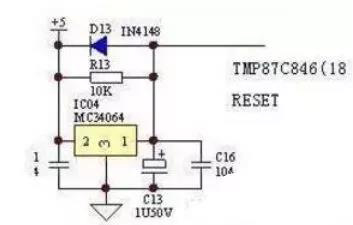

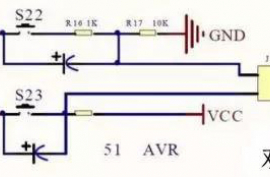

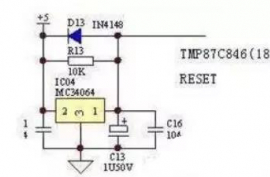

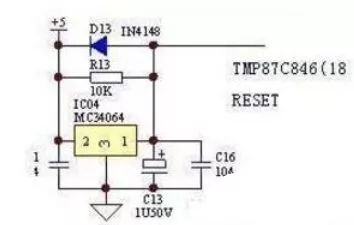

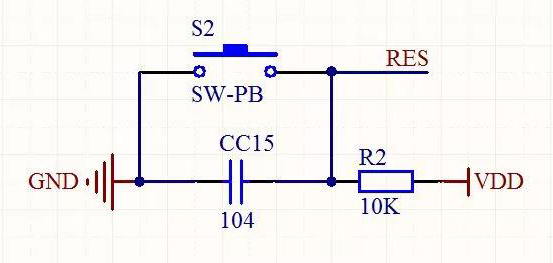

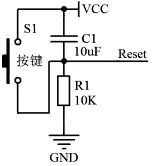

一般来说,单片机复位电路主要有四种类型:微分型复位电路 、 积分型复位电路 、 比较器型复位电路 和 看门狗型复位电路 。接下来小宇老师就拿出相对简单的微分和积分型电路进行讲解,让读者朋友们能有一个直观的感受。

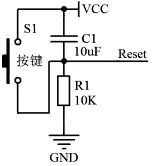

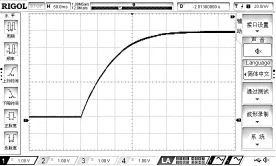

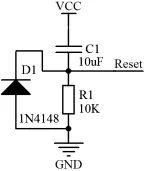

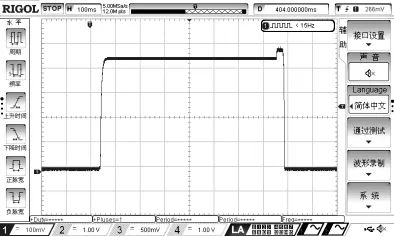

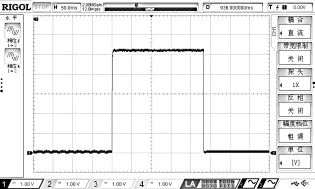

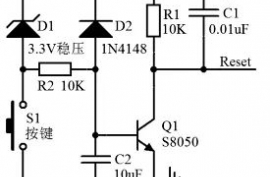

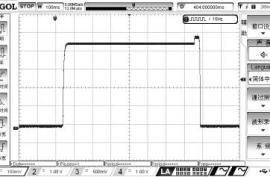

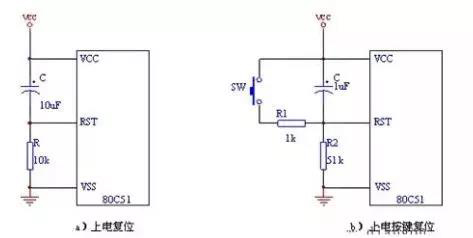

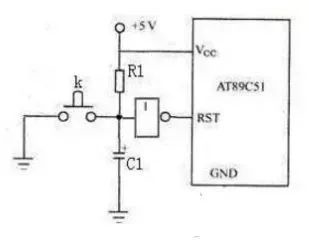

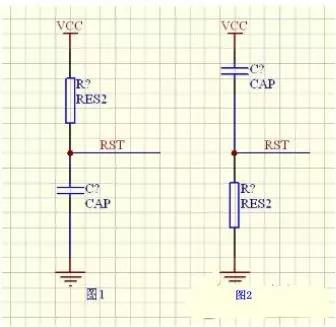

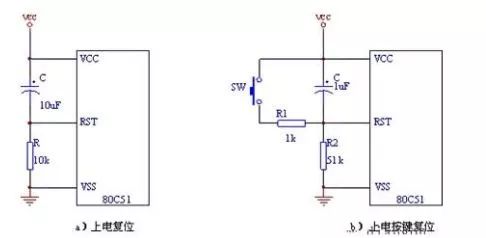

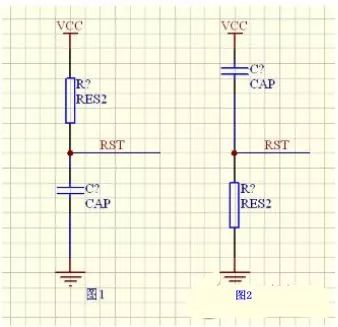

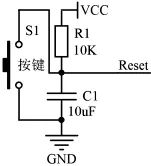

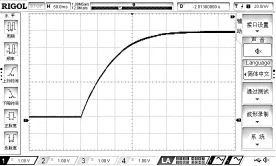

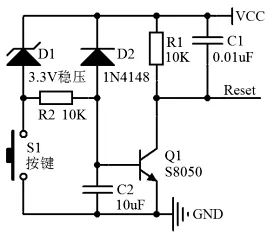

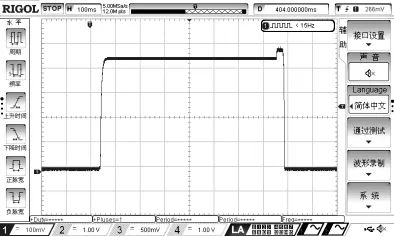

常见的阻容式微分复位电路如图1(a)所示,电路中的“Reset”电气网络连接至单片机“RST”引脚。该电路上电后的波形如图(b),其波形在上电后先是高电平,经过100ms后跌落到了1V以下最终保持低电平状态,我们常将其称为“高电平”复位电路。

(a)

(a)

(b)

(b)

图1 微分型高电平复位电路原理图

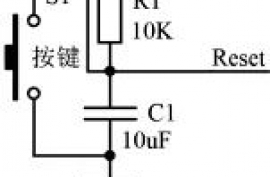

分析微分复位电路,该电路的组成十分简单,其核心实现仅有1个电阻和1个电容组成,外加的S1按键主要实现手动复位功能,当S1按下时“Reset”电气网络被强制拉高实现复位。

在设计该电路时一定要先根据单片机工作的时钟频率去考虑阻容的取值,若系统选用12MHz石英晶振,则1个机器周期就是1us,复位信号的脉冲宽度最小也要2us以上,但是真正设计时最好不要贴近理论值去构造电路,复位信号脉冲宽度最好是20至200ms为宜。当晶振频率大于或等于12MHz时,常见取值C1为10uF,R1为10k。

当系统上电时C1相当于通路,“Reset”电气网络上电瞬间为高电平,随着R1不断泄放C1的电荷,“Reset”电气网络的电压逐渐降低,最终降到低电平区间。在放电的过程中“Reset”电气网络的高电平持续了100ms左右才跌落到1V以下,这远大于2个机器周期的复位时间要求,即复位有效。

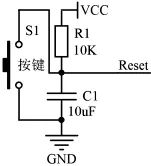

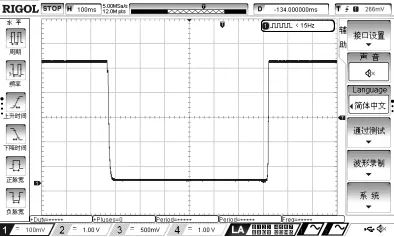

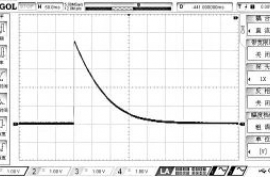

若将图2中的电阻R1和电容C1互换位置就可以变成阻容式积分复位电路,电路原理图如图2(a)所示。该电路上电后的波形如图(b)所示,其波形在上电后先是低电平,然后经过50ms左右就超过了1.6V并继续上升,最终保持在高电平电压区间,我们常将该电路称为“低电平”复位电路。

当系统上电时C1相当于通路,故而“Reset”电气网络上电瞬间为低电平,随着电源通过R1不断的向C1充电,“Reset”电气网络的电位逐渐抬升并最终保持高电平。外加的S1按键主要实现手动复位功能,当S1按下时“Reset”电气网络被强制拉低实现复位。

(a)

(a)

(b)

(b)

图1 微分型高电平复位电路原理图

阻容式复位电路非常简单,成本也很低,但是可靠性如何呢?可能有的读者朋友会说:市面上的开发板都用这个电路,我在实验室也用这个电路,从来没遇到过问题,而且这种经典电路每本书都这么讲的,你敢说不可靠?

小宇老师得站出来说:这电路确实简单,但可靠性确实不高。首先来说,阻容器件本身存在器件误差,误差会直接导致RC时间常数和充放电时间的差异,批量制造时难以保证产品的一致性。其次,阻容器件存在老化现象和温漂问题,在长期使用或者严苛温度环境中容易造成较大误差导致失效。

最后,简单的阻容复位电路会有电容的迟滞充放电问题,导致复位信号可能不满足复位电平阈值要求,且面对来自电源的波动或者快速开关机情况会出现无法复位的问题。

朋友们可能会说,器件参数误差、老化和温漂在一般产品中都可以接受,一致性问题也没有那么高要求,本着“能用就行”的原则,这个电路也凑合用吧!也不是不行,但是可以稍微改进下,且看小宇老师做个实验。

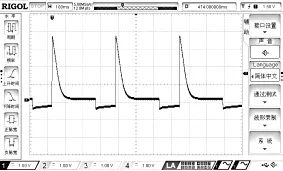

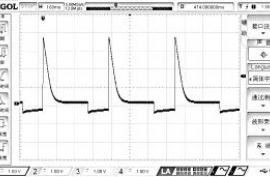

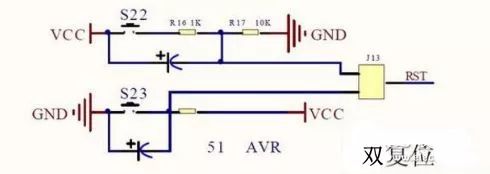

以图1(a)所示的阻容式微分复位电路为例,若将电源周期性通断,其复位波形就不再完美了,实际波形如图3(a)所示,复位波形由于电容的缓慢放电原因出现了下降迟缓且无法到达低电平阈值的问题(也就是复位电压“下不去”的情况),这种复位信号就不能保证单片机系统的有效复位,若工业控制有关的板卡遇到电源波动出现无法复位的情况,无疑是危险的。

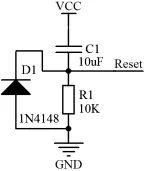

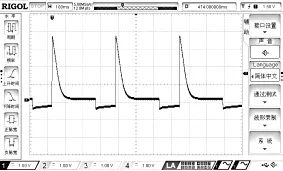

若将微分复位电路按图3(b)改进,在电阻R1的两端并联个D1,再次将电源周期性通断,复位波形就会变成如图3(c)所示的波形。从波形上看,电路改造后复位波形得到了明显的改善,图中波形下降迅速且可以下降到低电平阈值以下,不会出现频繁上电时复位电压“下不去”的情况。

(a)

(a)

(b)

(b)

(c)

(c)

图3 微分型高电平不可靠复位及优化实验

这个“不起眼”的D1为电容C1在掉电情况下提供了一条迅速泄放电荷的通道,这样一来就可以保证在电源频繁波动或者周期性上电情况下的正常复位。有的朋友可能要说了,这个复位波形看起来还是很“怪异”啊!虽说是高电平复位波形,但是看起来和“毛刺”一样,就不能通过什么电路把复位信号搞成类似于高低电平的波形样式吗?

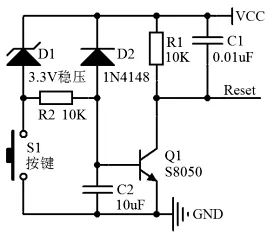

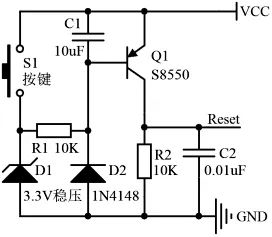

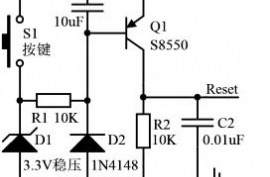

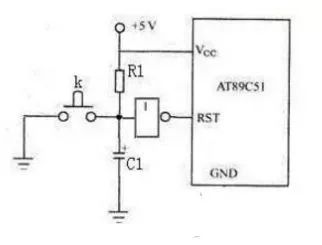

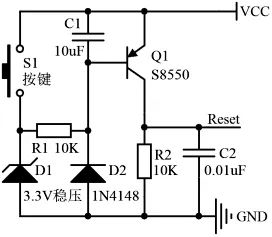

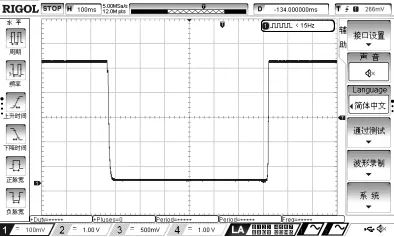

当然也是可以的,我们再把电路优化一次。添加三极管和二极管进去,最终搭建出一种阈值电压比较型高电平复位电路如图4(a)所示。电路的目的就是构造一个“复位阈值电压比较器”,电路中的稳压二极管D1(实际选用3.3V稳压管)和开关二极管D2(实际选用1N4148,导通压降为0.6V左右)决定了复位信号的电平阈值,大致就是3.3V+0.6V=3.9V左右(朋友们也可以更替D1的稳压参数构成更多复位阈值)。

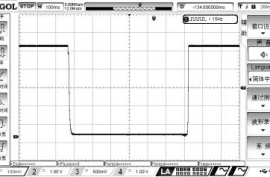

电路中的三极管Q1及外围电路构成了一个简单的比较器电路,当电源波动的时候也可以有效的根据阈值比较完成复位动作。R2的大小可以改变输出信号的驱动能力,R1和C2一起决定了复位延时的长度,C1是为了抑制和旁路电源中的高频噪声。该电路上电后的复位波形如图4(b)所示,这样的波形总算是“漂亮”了。

(a)

(a)

(a)

(a)

图4 一种阈值电压比较型高电平复位电路原理图

虽说图4(b)所示波形的高电平末端有个向上的小“凸起”,但这并不影响复位信号的有效性,因为复位电压只要在1.6V以上就满足高电平复位系列单片机的复位要求了,如果有朋友和小宇老师一样是个“强迫症”,那您也可以微调R1和C2的取值去优化波形。

基于图4(a)所示的高电平复位电路,我们也可以稍加变形做成如图5(a)所示的“低电平复位电路”,该电路适用于低电平复位的单片机。该电路上电后的复位波形如图5(b)所示,该波形相当于图4(b)的取反波形。

(a)

(a)

(a)

(a)

图5 一种阈值电压比较型低电平复位电路原理图

由此可见,小电路也有很多讲究。此处的改进只是抛砖引玉,朋友们别被“抛出去的砖”砸晕了,复位电路还存在很多改进电路和一些实际问题,希望读者朋友们可以自行延展,单片机复位端口处还可并联0.01至0.1uF的瓷片电容,以抑制电源高频噪声干扰或配置施密特触发器电路,进一步的提高单片机对串入噪声的抑制。

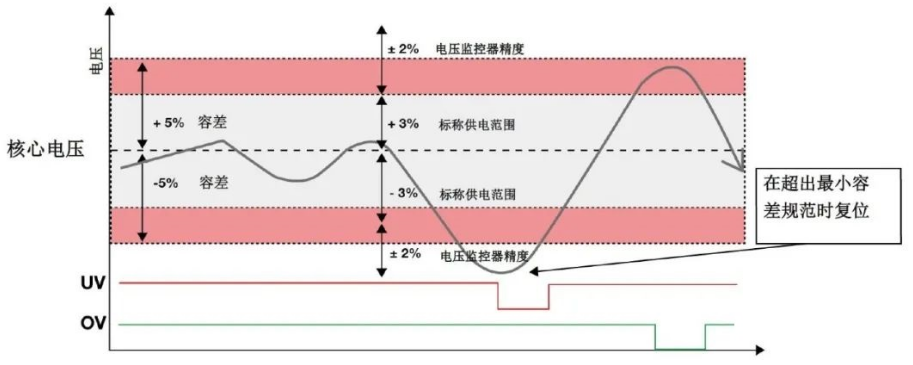

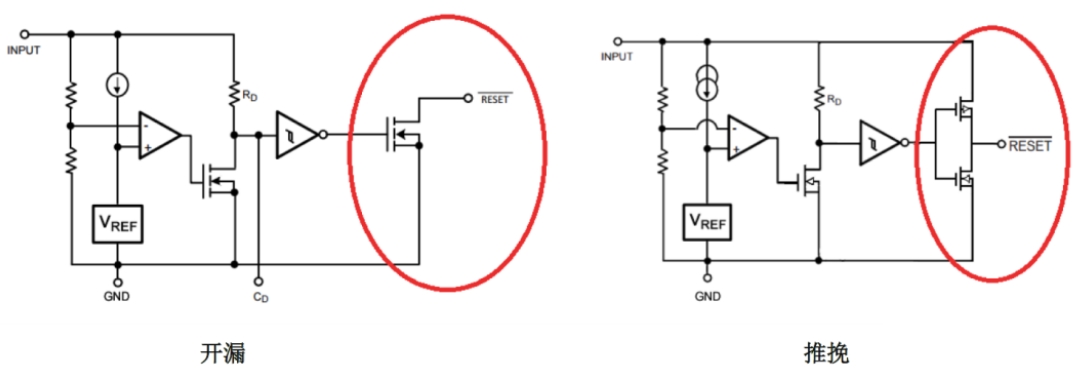

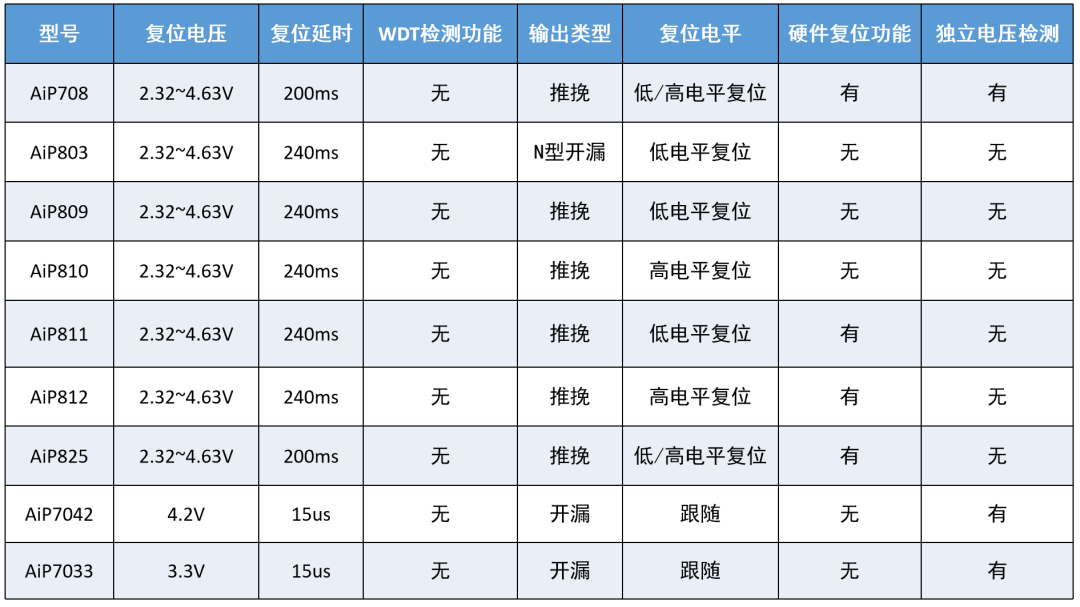

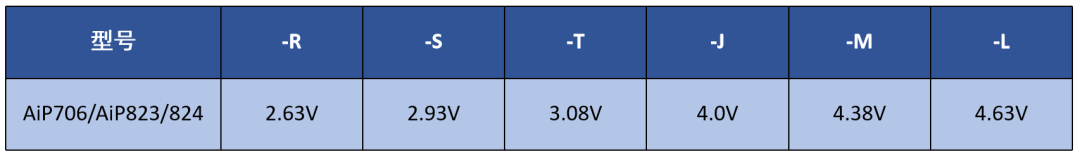

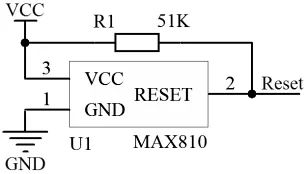

可能有的朋友还是不满意这种RC充放电电路产生的复位波形,能不能有什么电路或者器件使用简单又能产生类似方波一样的复位波形呢?答案是肯定的,想要高可靠复位单元可以选择专用的复位监控芯片。如飞利浦半导体、美信半导体公司均有此类产品,这些芯片的体积小、功耗低、门槛电压可选。

集成度的提高使抗干扰能力和温度适应性都得到了大幅提高,可以保证系统在不同的异常条件下进行可靠的复位。其原理其实是通过确定的电压阈值启动复位操作,同时排除瞬间干扰的影响,又有防止单片机在电源启动和关闭期间的误操作效果,以保证程序的正常执行。

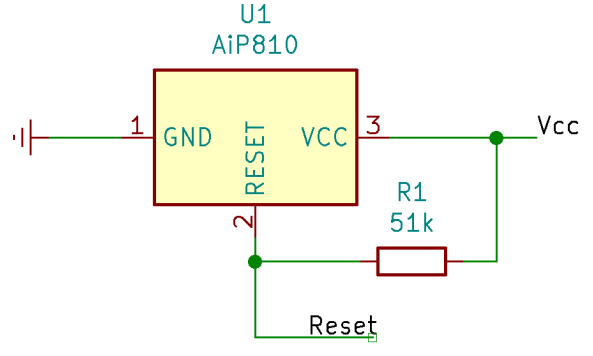

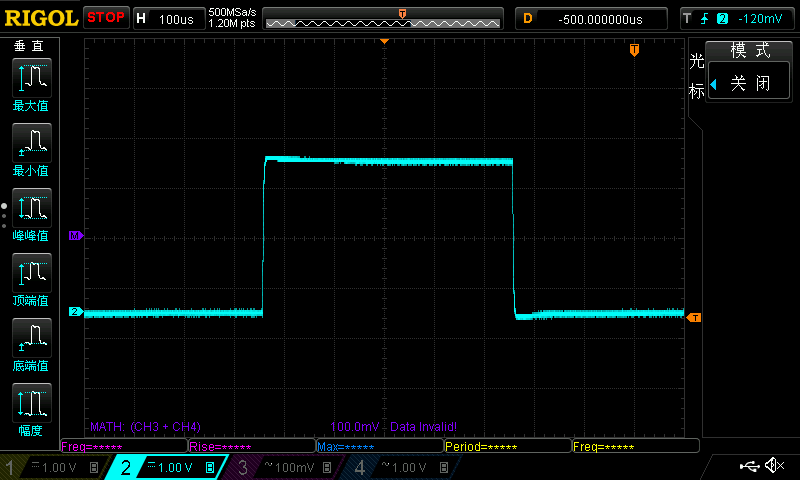

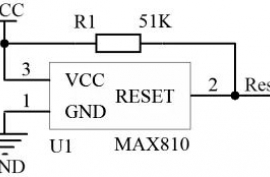

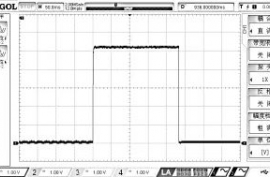

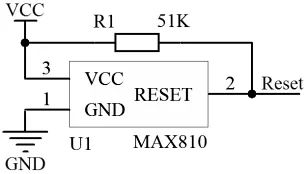

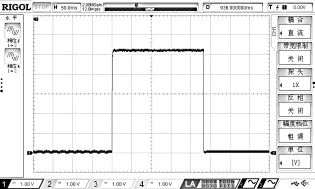

我们以美信公司生产的MAX810这款高电平复位电路专用芯片为例,搭建如图6(a)所示电路,上电后测量“Reset”电气网络可以得到如图6(b)所示波形,这个波形就堪称“完美”了。

(a)

(a)

(a)

(a)

图6 专用复位芯片MAX810电路及复位波形

常见的低电平复位电路有MAX705、MAX706、MAX809、MAX811等器件。高电平复位电路有MAX810、MAX812等器件。而MAX707、MAX708、MAX813L等器件同时有高、低电平复位输出信号和看门狗输出,在实际产品中经常会看到它们,需要注意的是,不同芯片的复位脉冲时间不一样,但是一般都可以达到100至200ms左右,完全满足常见处理器对复位时间的需求,有的芯片还支持复位阈值设定、备份电池切换、看门狗定时器、门限值检测器、复位脉冲极性选择等更为高级的功能,此处就留给读者朋友们自行去研究了。

来源:嵌入式大杂烩

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。