单片机

一、引言

单片机软件开发过程中,软件调试遇到的各种问题常令初学者感到不知所措。实际上。各种仿真开发软件的程序调试基本方法和技巧大同小异,掌握正确的程序调试基本技巧。对于排查这些程序错误问题可以起到举一反三、事半功倍的效果。软件调试是单片机技术人员必须掌握的重要基本技能。

下面以单片机常用开发软件Keil为例,通过一个项目任务实例来介绍单片机软件仿真与调试的方法。

二、Keil仿真与调试

点击运行软件Keil uVision2.其调试操作步骤大体可以分为5步:

1、创建工程

在项目开发中,并不是仅有一个用户源程序就够了,还要为这个项目选择CPU型号、设置编译和调试参数。有一些项目还会有多个文件组成。因此将这些参数设置和所需要的所有文件统称为一个工程,存放于专门的工程文件夹下。这里先建立一个工程文件夹如F:\exam.

① 创建新工程。鼠标左键单击主菜单Project一>New Project.弹出。Create New Project"对话框,用鼠标选择你要保存工程的文件夹(如FAexam),输入新工程名(如"exam")。单击"保存"按键。

② 在随后弹出的CPU型号设置对话框中选择单片机的型号(如"AT89C51"),单击"确定"完成。

2、建立源程序文件并加入工程

① 鼠标左键单击菜单。File一>New新建文件。

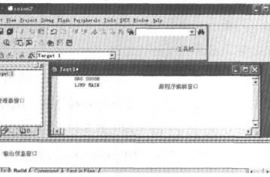

弹出图1窗口。自动进入编辑工作模式。

② 在文本窗口中输入和编辑用户的源程序。

【项目任务】设计一种花样彩灯程序,实现单片机P1口驱动相连的8个发光二极管依次循环点亮。

③ 单击菜单。File一>Save as.弹出文件保存对话框,选择工程文件夹("F:\exam")。输入源程序文件名(如"exam.asm"),点击"保存"按钮。

注意汇编源程序的扩展名必须为asrn,C51源程序扩展名必须为*.C.

④ 将源程序加入工程。用鼠标点击图标"Target1"前的"+"号,展开后右键单击Source Group弹出快捷菜单,点击"Add File to Group'SourceGroup 1"项弹出源程序加入工程对话框。选择刚保存的用户源程序exam.asm,点击ADD按钮加入工程,点击Close关闭对话框。

3、工程参数设置

用鼠标左键单击主菜单Project一>Options forTarget'Targetl弹出工程参数设置对话框。关于工程参数设置的内容很多,篇幅所限,这里仅介绍通常需要设置的三个参数:

① 设置CPU型号。前面已经进行了设置。

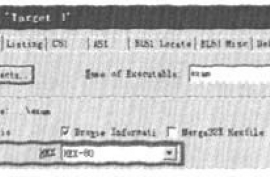

② 在设置对话框的"Target"标签下"Xtal(Mhz)"处输入单片机的晶振(如"12")如图2.

③ 在设置对话框的"Output"标签下,选中"Create HEX file"项。用以编译生成可执行的机器码hex文件。如图3所示。该hex文件可以通过编程器写入或下载到单片机中运行。

4、编译源文件

鼠标左键单击主菜单Project一>Built target或快捷按钮编译文件。

若有语法错误,输出窗口将有相应提示信息。

双击提示信息行,光标会停留在源程序出错处。如图4所示。经检查发现:本程序第3条DJNZ指令被错误输入成了DJNA.用户可根据提示修改源程序,然后再次编译。注意。Keil具有语法检查功能,源程序中正确的指令关键词将变颜色,没变色的为输入错误,方便用户查找语法错误。

若编译后输出信息窗13显示"0 Errors(s),0Warning(s)",则说明源程序的语法错误已经全部排除。注意:有Errors不能Debug,也不产生HEX码,有Warning是允许的,可以运行。

5、调试程序

源程序编译通过,表明语法正确,却并不能保证该程序能够正确运行。还需要对其逻辑功能进行调试。Keil软件具有很强的软件仿真功能。

鼠标左击主菜单Debug一>Sta/Stop Debug Session子菜单或调试/编辑模式切换按钮。进入调试程序工作模式,软件窗口如图5所示。重复点击该按钮可以实现在编辑模式和调试模式之间进行切换。

调试程序时的程序运行控制按钮从左到右依次为复位、连续运行,暂停、单步、过程单步、执行完当前子程序、运行到光标当前行。复位按钮模拟芯片的复位,它将使程序回到最开头处执行。当程序处于停止状态时复位才有效,程序处于运行状态时停止按钮才有效。

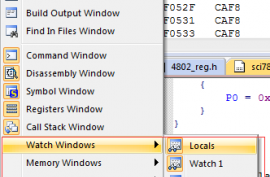

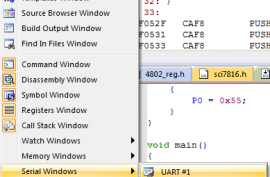

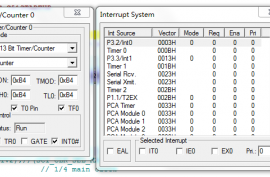

① 为了方便观察程序调试过程中各变量和RAM单元的中间结果。点击主菜单View一>Watch&Call Stack Window和View一>Memory Window打开观察变量窗13和存储器窗1:3进行显示。由于本例还要观察P1 13的输出变化,可以点击主菜单Peripherals一>I/O-Ports一>Port 1打开I/O 13 P1的观察窗13.

② 程序调试。

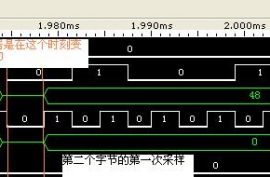

程序可以单步执行或连续执行。连续执行是指一条指令执行完后接着连续立即执行下一条,中间不停止。这样程序执行的速度很快。可以看到程序执行的总体效果。即最终结果是正确或错误。但如果程序有错,则难以确认具体出错地方。例如本例中点击连续运行按钮后。P1口输出01H后便始终保持不变。这显然与花样彩灯程序的循环显示要求不符。程序运行出错,如图6所示。

单步执行指每执行完一条指令后即停止。等待命令执行下一行程序,此时可以观察该条指令执行后得到的实际结果。对比分析是否与预期结果一致。

借此可以找到程序中的错误原因所在。这种方式的缺点是需要时间长,排查错误效率很低。尤其当程序很大时。

因此,对于用户确认没有错误的程序段可以采用连续运行。对怀疑出错或容易出错的地方则单步执行。对比排查错误。这样调试的效率将会高一些。

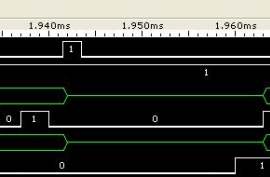

本例通过单步执行。发现程序运行过程中循环变量R3的值总在250和249之间变化,而且R1、R2、R7均始终无变化,如图7所示。对比程序分析,发现出现了死循环。原因在于第1条"DJNZR3,DEL2"的转移目的地址为DEL2,应该改为DEL3.

回到编辑状态,修改为"DJNZ R3,DEL3",编译后再次进入调试工作模式时,发现故障已经排除。

此时P1 1:3的输出仅1位高电平。且依次向左循环移位。R1、R2、R3、R7正常递减变化。如图8所示。

③ 断点设置。

程序调试时。一些程序行必须满足一定的条件才能被执行到(如程序中某变量达到一定的值、按键被按下、有中断产生等),这些条件往往是异步发生或难以预先设定的。这类问题采用单步执行的方法是很难调试的。这时可使用另一种重要的调试方法一断点设置。可以使用Debug一>lnsert/RemoveBreakPoint设置或移除断点。

断点设置的方法有多种,常用的是在某一程序行设置断点,设置好断点后可以连续运行程序。一旦执行到该程序即停止,可在此观察有关变量值,对比分析程序预期理想值,以确定问题所在。

三、结束语

程序开发过程中通常情况下需要综合运用单步执行、连续执行、设置断点、观察变量等各种程序调试方法。并不断积累总结调试经验。这种程序调试能力也是衡量软件开发者水平高低的标志之一。

文章来源 :博客园

学习与应用单片机的高潮正在工厂、学校及企事业单位大规模地兴起。过去习惯于传统电子领域的工程师、技术员正面临着全新的挑战,如不能在较短时间内学会单片机,势必会被时代所遗弃,只有勇敢地面对现实,挑战自我,加强学习,争取在较短的时间内将单片机技术融会贯通,才能跟上时代的步伐。

但是,许多的学习者(包括在校学生),他们总不得要领,从一开始学习时的热情高涨,到最后的沮丧放弃,使得大家对单片机产生了既爱又怕的感觉。

学习单片机并不象学习传统数字电路或模拟电路那样比较直观,原因是除了“硬件”之外还存在一个“软件”的因素。正是这个“软件”因素的存在,使得许多初学者怎么也弄不懂单片机的工作过程,他们怎么也不明白为什么将几个数送来送去,就能控制一盏灯亮/灭?能控制一个电机变速?由此对单片机产生一种“神奇”、“敬畏”甚至“恐惧”感,阻碍了学习单片机的热情与兴趣,这就有社会上“单片机难学”一说。

笔者多年来与众多的电子爱好者、在校学生打过交道,深知他们学习单片机中碰到的难处,况且作者本人也是从一位电子爱好者成长为工程师的,此过程自然少不了学习、探索、实践、进步这样一条规律,因此深切地知道,学单片机难,主要是不得要领,难以入门。一旦找到学习的捷径,入了门,能初步掌握编程技术并产生实际效果,那么必然信心大增。接下来,再向新的深度、广度进军时,心里也不那么焦虑,比较坦然了,能够一步一个脚印下去扩展自己的知识面。这里根据笔者的经验谈谈学习方法、技巧及如何在较短时间内学会单片机。

学习单片机的最有效方法是理论与实践并重

对一个初学单片机的人来说,如果按教科书式的学法,上来就是一大堆指令、名词,学了半天还搞不清这些指令起什么作用,能够产生什么实际效果,那么也许用不了几天就会觉得枯燥乏味而半途而废。所以学习与实践结合是一个好方法,边学习、边演练,循序渐进,这样用不了几次就能将用到的指令理解、吃透、扎根于脑海,甚至“根深蒂固”。也就是说,当你此次学习完某几条指令后(一次数量不求多,只求懂),接下去就该做实验了,通过实验,使你感受刚才的指令产生了控制效果,眼睛看得见(灯光)、耳朵听得到(声音),更能深刻理解指令是怎样转化成信号去控制电子产品的。说句过分的话,单片机与其说是学出来的,还不如说是做实验练出来的,何况做实验本身也是一种学习过程。因此边学边练的学习方法,效果特别好,许多读者经3~6个月的学习已能开发简单的产品了(如霓红灯广告牌控制、累加计数器等)。

学习单片机要合理安排学习时间持之以恒

学习单片机可不能“三天打鱼、二天晒网”,要有持之以恒的毅力与决心,学习完几条指令后,就应及时做实验,融会贯通,而不要等几天或几个星期有时间后再做实验,这样效果不好甚至前学后忘。另外要有打“持久战”的心理准备,不要兴趣来时学上几天,无兴趣时凉上几星期。学习单片机很重要的一点就是持之以恒。

学习单片机要使用循环学习法使之根深蒂固

笔者曾在其它刊物举办过《手把手教你学单片机》讲座,该讲座入门起点低,很多朋友觉得好学、易学,很快就能将讲座从头至尾学完、学懂,但过了几个月,在开发产品时对指令的具体作用就有些淡忘了。根据现代科学的研究,对只短暂学过一遍的知识,充其量只比浮光掠影稍好。因此,较好的方法是,过一段时间后(1~2个月)再重新做一遍,这样反复循环几次就能彻底弄懂消化,永不忘却。有道是:若人生能细看《水浒传》10遍,那么里面的故事内容、人物场情将永生不忘。

学习单片机要进行适当投资购买实验器材及书籍资料

单片机技术是一门含金量高的技术,一旦学会后,它给你带来的效益回报当然也高,无论是应聘求职还是自起炉灶开厂办公司,其前景是光明无限。因此在学习时要舍得适当投资购买必要的学习、实验器材,另外还要经常去科技图书店看看,购买一些适合自己学习、提高的书籍。总之,春天不播种哪来秋天的收获?考虑到学习成本,对初学者可采用“程序完成后软件仿真→单片机烧录程序→试验板通电实验”的方法(现在的快闪型单片机其程序可烧写1000次以上),这样整套实验器材(不包括PC机)只有几百元,对大部分已工作的爱好者来说都有这个能力承受。而经济条件较好的读者可考虑使用在线仿真器(ICE)进行实验,这样学习时直观性更好。

总之这里所谈的就是作者的亲身体验。我们希望以最实用的方法,最易入门的手法,将初学者领进单片机世界的大门里,使这些仅稍懂硬件原理的人通过实践能理解软件的作用,让他们知道在单片机组成的系统中硬件与软件的区分并不绝对,硬件能做的工作一般情况下软件也能完成,软件的功能也可用硬件替代。等初步学会了单片机软件设计后,可将通常由硬件完成的工作交由软件实现,这样,系统的体积、功耗、成本将大大降低,而功能得到提升与增强,使习惯于传统电路设计的人对单片机产生一种妙不可言的相见恨晚之感,感觉到真正找到了一种理想化的器件,真正感受、体会到现代单片微型计算机的强大作用,从而投身于单片机的领域中。只要你肯努力、下功夫、多实践,一定会成功的。

文章来源: 玩转单片机