RX72M是瑞萨电子适用于工业网络解决方案的高性能32位微控制器,高达240MHz主频和1396CoreMark的性能,带双精度浮点运算,专门针对马达控制的三角函数加速器,可实现sin、cos、反三角函数以及开方函数运算,支持6通道的Delta-sigma调制器接口,支持电流环反馈信号。RX72M除了常用的外设接口外,还集成了专用于EtherCAT的ESC接口,可以用于开发EtherCAT IO模组、EtherCAT网关、EtherCAT步进、伺服驱动器,是一款性价比高的EtherCAT从站硬件,本文将为您介绍瑞萨MCU RX72M在开发EtherCAT应用中的Q&A。

有关RX72M产品的更多介绍,您可识别下方二维码或复制链接到浏览器中打开查看:

RX72M

什么是EtherCAT jitter?为什么EtherCAT是low Jitter communication?

EtherCAT jitter分主站jitter和从站网络jitter;

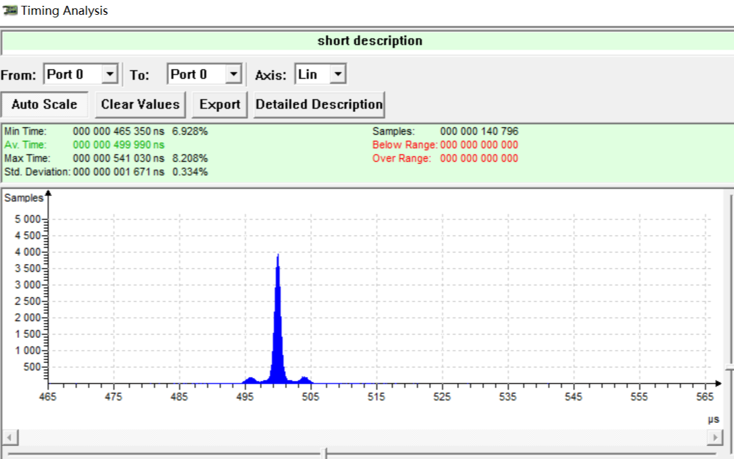

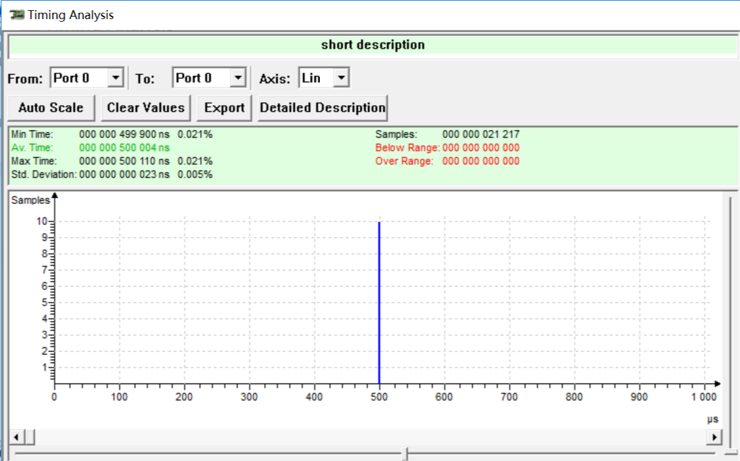

主站jitter指的是master cycle time jitter,主站EtherCAT通讯周期抖动,同时该参数也是反映了主站发送EtherCAT报文帧抖动情况,主站发送报文帧的抖动情况通常可以通过特殊工具数据抓包来测试,反映的是主站的性能/稳定性,如下图是两个主站在master cycle time为500us时的抖动情况,图1有正负几十us抖动,图2是1个us抖动以内,明显抖动小于图1。

图1

图2

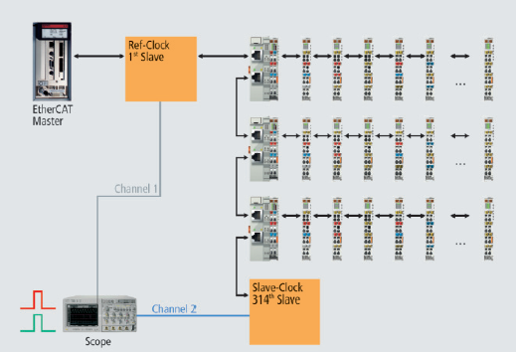

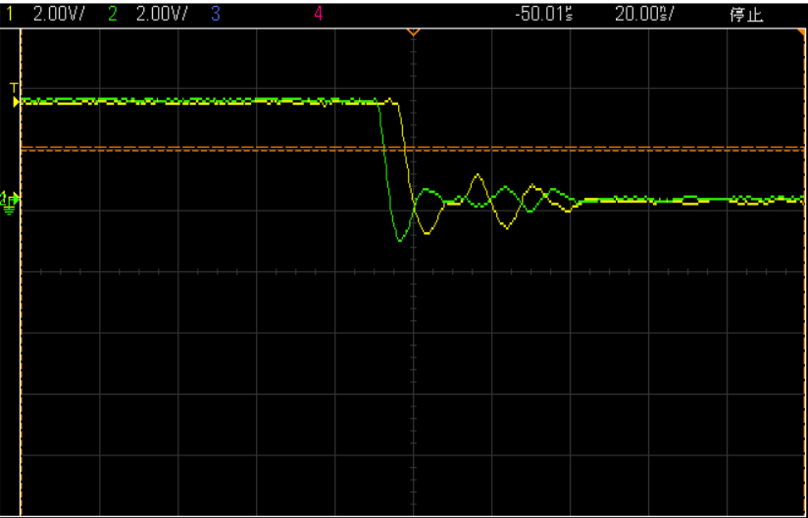

从站网络jitter,指的是从站网络的同步抖动,指的是从站网络中第一个DC从站和最后一个DC从站的SYNC信号的时间偏差,反映的是从站网络的同步性能(如图4两个SYNC信号时间偏差小于10ns)。

图3

图4

Master如何映射各个slaves?

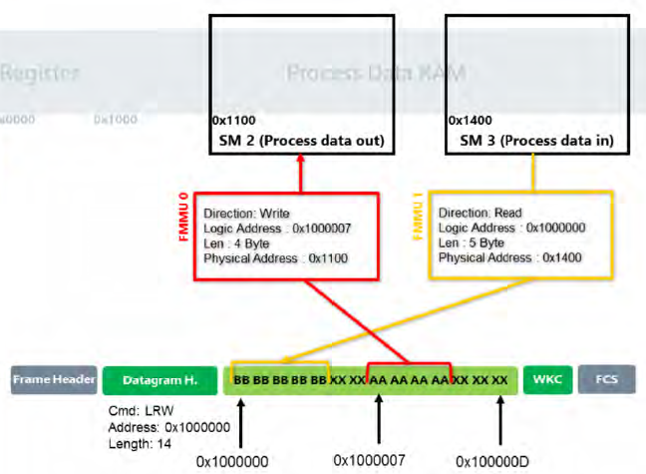

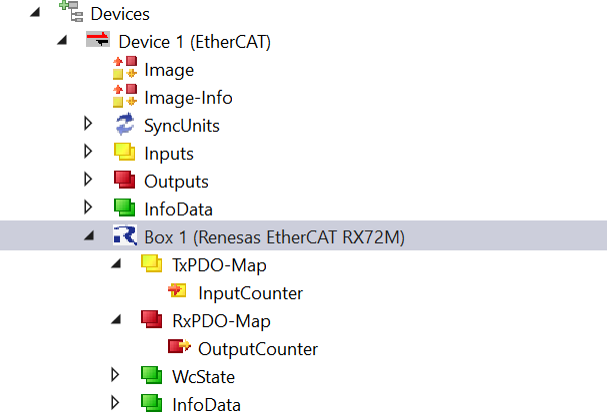

从站网络中每个站点由于ESC的存在,物理地址和逻辑地址是对应的,当主站扫描后,所有的TxPDO数据和RxPDO数据就已经在整个报文帧中分配好了位置,报文帧会遍历所有站点去做数据交换(类似高铁到站上下车)。

图5

图6

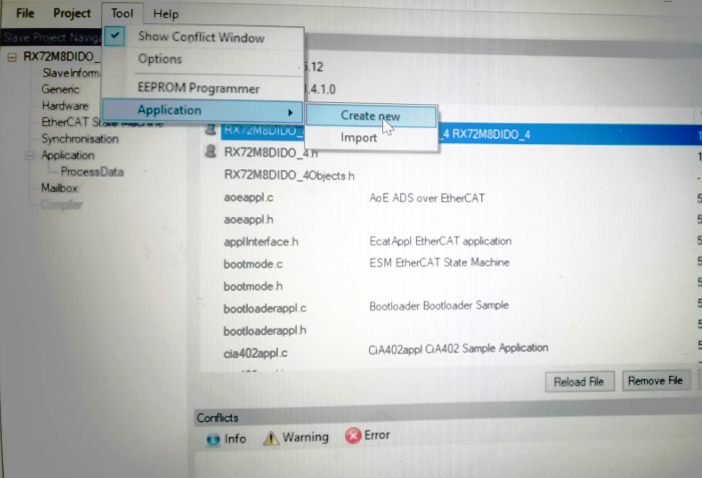

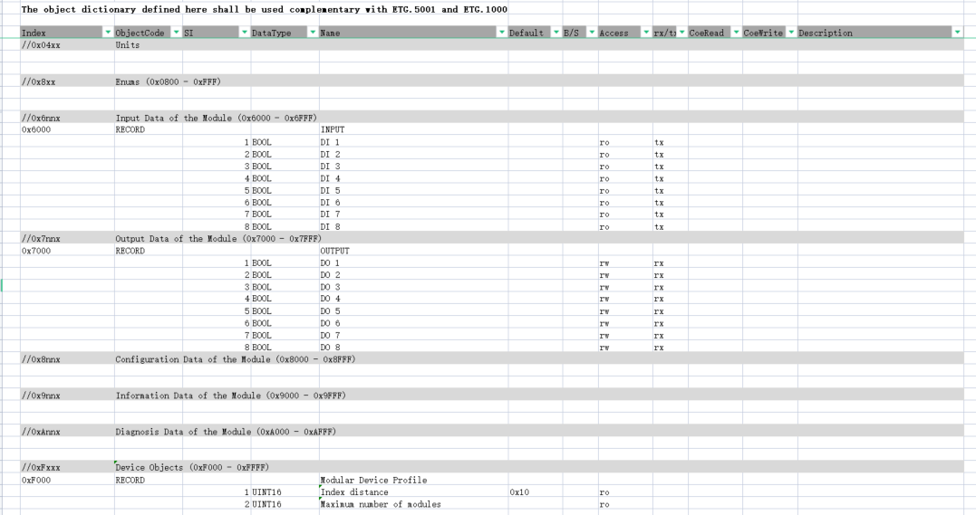

SSC工具创建的代码后,如何修改PDO-Map,增加新的变量?

可以通过手动方式修改代码以及ESI文件,或者SSC工具创建新应用,编辑excel表格自动生成新文件。

图7

图8

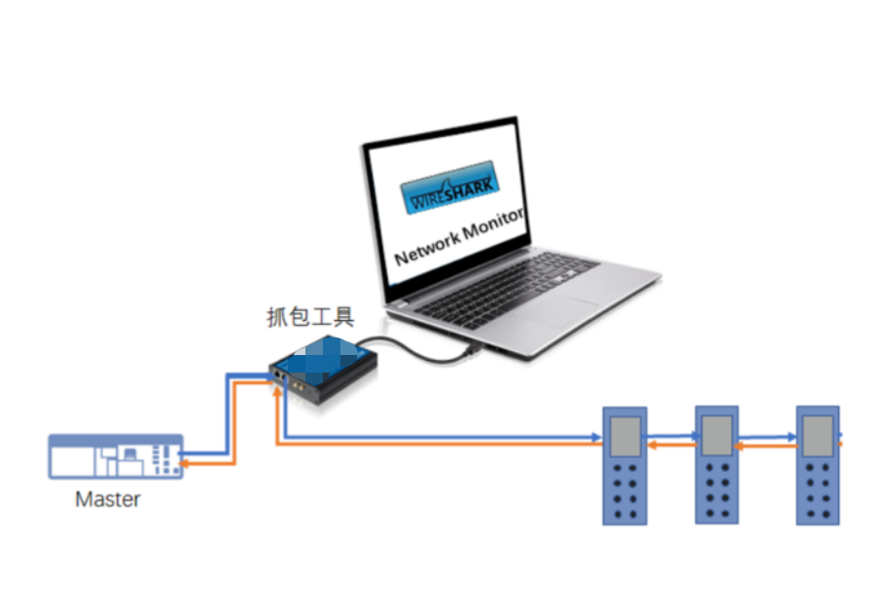

Wireshark捕获ECAT数据正确方法?

通过专用的抓包工具接入网络中作为一个侦听器(硬件延时ns级别,可忽略不计),获取到的报文在PC端的wireshark上处理,参考:

https://www.ethercat.org.cn/memberarea/en/knowledge_base_E3DFFB9A73A146D...

图9

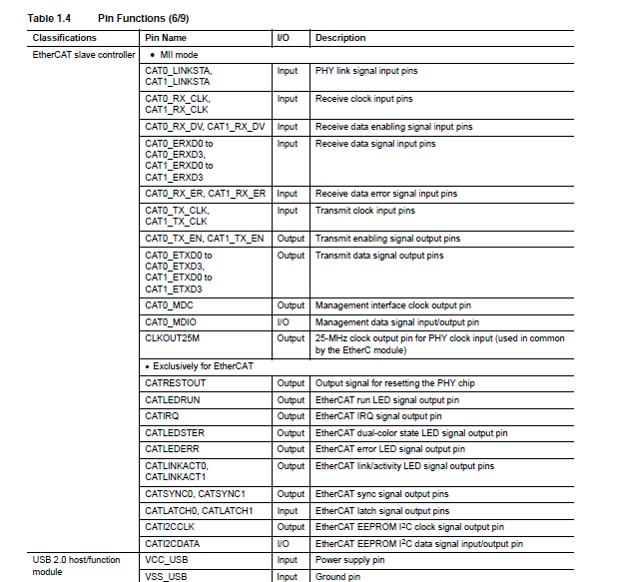

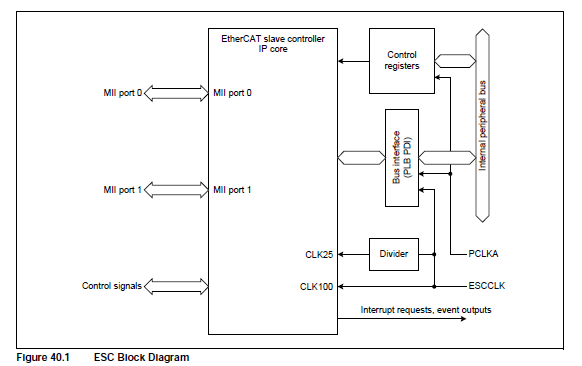

RX72M的ESC接口与PHY连接模式是MII还是RMII?

RX72M的ESC只支持MII模式(部分其他厂商的ESC也仅支持MII)。

图10

图11

RX72M EtherCAT同步功能如何使用,如何测试这个功能确实开启了,以及一些指标?

同步功能的使用,需要在主站端配置选择同步模式如图12,可以通过抓取数据包分析,如有周期性的ARMW的指令,就说明DC功能已经使能上了。

关于同步的指标,通常是测试从站网络的抖动,即使用示波器测试每个从站产生的同步信号SYNC,比较时间差,网络中第一个从站的SYNC和最后一个从站的SYNC的时间差及为最大的同步抖动。

图12

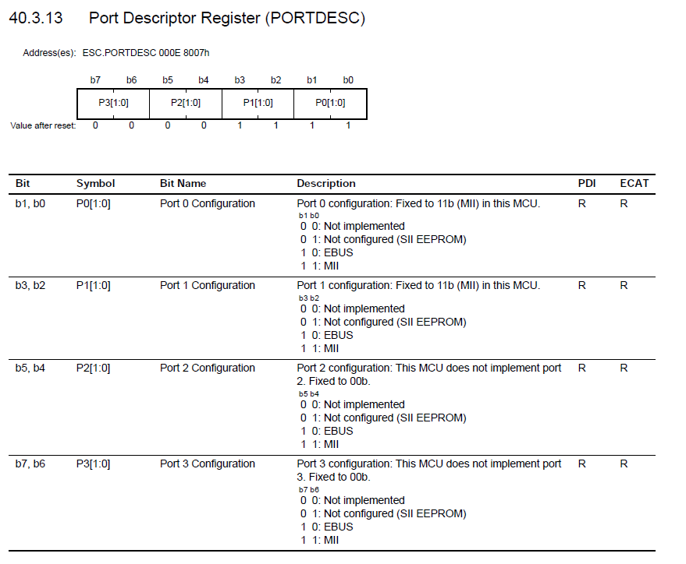

卡片式IO应用时,RX72M是否支持EBUS背板总线技术?

不支持,EBUS是德国倍福定义的数据传输标准,是基于LVDS(Low Voltage Differential Signal,低压差分信号)技术,属于倍福的专利技术,不过基于RX72M的卡片式IO之间也可以是EtherCAT的连接方式,通过PHY直连(不需要变压器)的方式连接。

图13

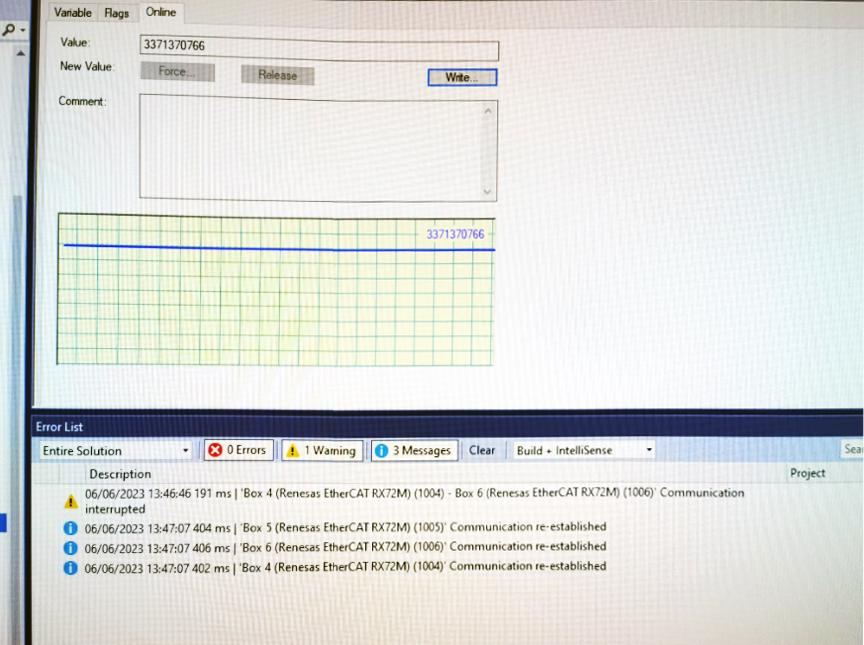

RX72M作为EtherCAT从站在通讯时,当断开线缆后重新连线,是否能重新进入op,自动恢复通讯?

具体取决于主站的功能和从站应用逻辑,下图是twincat主站和RX72M硬件板子数据收发测试,是可以恢复建立通讯。

图14

RX72M支持的最快的Master EtherCAT cycle time是多少?

EtherCAT数据帧经过RX72M的ESC接口是小于300ns,所以理论上评估值65us是ok的,但实际测试也取决于主站的性能,要求主站在极限测试条件下能够保持master cycle time稳定,如果主站周期抖动大,会影响实际测试效果。

RX72M上EtherCAT的DC同步机制是如何实现的?首先在硬件接口上是否能实现,是否需要Sync0/Sync1接口?目前我们的方案都没有接这两个管脚。其次在软件上我们现有的协议上是否已经能实现了?还需要增加什么内容吗?

RX72M硬件板子以及配套的开源的ECAT软件代码是支持DC功能的,DC功能的使用需要在主站端去使能DC配置;RX72M是MCU+ESC集成于一体的单芯片方案,不是MCU+单独ESC芯片方式,因此SYNC信号引脚不需要单独引出接MCU作为外部中断;软件中已支持sync0和sync0中断服务函数,只需要在主站中做DC配置,然后在sync中断服务函数中去做应用处理,比如数据更新发送等即可。

RX72M上DC同步应用中,不同厂商的应用算法不同导致时间开销也不同,比如不同厂商不同的电机算法时间,如何保证多轴同步运动?

EtherCAT同步机制可以使得从站网络不同节点产生SYNC信号时间偏差是ns级别,该SYNC信号作为MCU的中断信号,保证中断信号的同步,同时EtherCAT也支持通过设置调整SM中断和SYNC信号的间隔时间(the time between SM and the starting of SYNC)来保证留有足够时间,在SYNC信号产生之前,已处理完应用算法。

RX72M开发板上对EEPROM芯片大小和型号要求是什么?

EEPROM size和XML文件的大小密切相关,取决于ESI文件的内容多少。对于RX72M来说,仅关系到寄存器ESCMR的PROMSIZE位设定为0还是1(0:最大到16-Kbit,1:32-Kbit到4-Mbit)。在Smart Configurator中对应了r_ecat_rx Property > Configurations > EEPROM size的值,跟硬件匹配即可。

EEPROM推荐型号包括:R1EX24016 (16Kbit),R1EX24032 (32Kbit),M24C32 (32Kbit),没有任何限定,因EEPROM IIC通信都是通用协议,size符合应用需求即可。

RX72M硬件板上,PHY晶振选用独立的,还是用RX72M输出的25M信号?

选用独立的晶振或者RX72M输出25M都可以,瑞萨PHY型号为KSZ8081的硬件板开发板,使用的是RX72M输出的25MHz的时钟。

您可点击下方链接进入瑞萨技术论坛:

https://community-ja.renesas.com/zh/forums-groups/mcu-mpu/

来源:瑞萨嵌入式小百科

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。