01、RESET系统

复位MCU可使MCU从已知的初始条件下开始运行。系统复位开始时,片上稳压器处于完全工作状态,系统时钟由内部参考时钟产生。

外部引脚RESET

对于所有的复位源,RESET_B引脚都会被MCU驱动为低电平,时长至少维持128个总线时钟周期,直到闪存初始化完成。在闪存初始化完成后,RESET_B引脚被释放,芯片内部复位信号失效。外部保持RESET_B引脚被拉低,会延迟芯片内部复位信号的失效时间。如果发生外部引脚复位,复位模块的状态寄存器中相应的标志位会被置位。因此,应用软件可以通过读取该寄存器来检测外部引脚的复位。

复位引脚,与其他一些GPIO类似,有一个弱的内部上拉。如果环境和客户的应用存在噪声影响,就必须在复位引脚上直接加一个外部上拉电阻到VDD,以避免发生随机的或意外的复位。关于该引脚允许的电压和电流水平,请参考器件的数据手册。

尽管复位线中的电容对MCU来说不是必须项,但在某些情况下,为了进一步增加ESD保护,会在RESET引脚和地之间添加一个外部电容。上拉电阻和电容的值须根据应用的设计要求选择。关于MCU可检测到的最小RESET脉冲值,请参考器件的数据手册。

02、RJTAG和TRACE接口

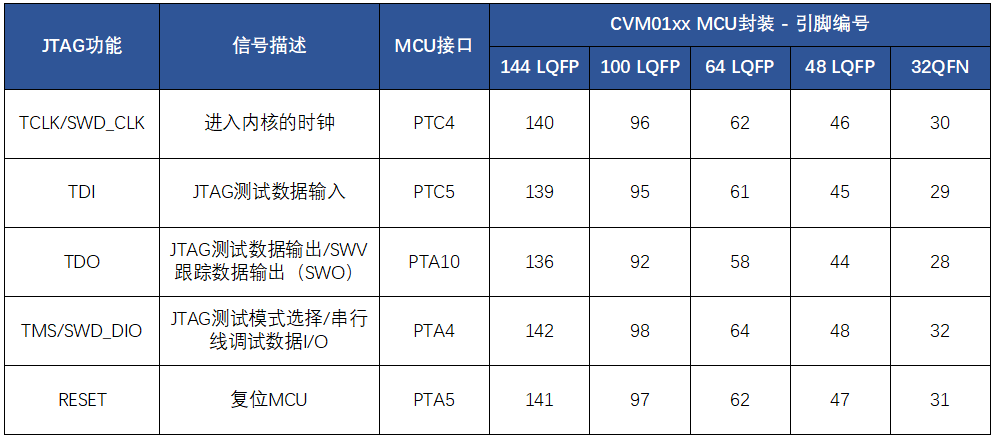

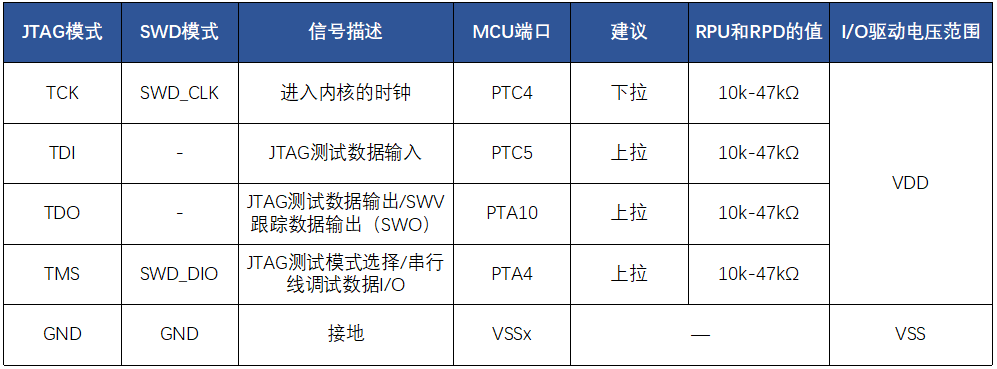

本章节列举了一些常用的调试连接器,大多数ARM开发工具都会使用这些引脚。当开发ARM电路板时,建议使用标准的调试信号排列,以使与调试器的连接更容易。SWD/SWV引脚叠加在JTAG引脚之上,如下所示。

△表1 CVM01xx – JTAG和SWD信号描述

△表2 CVM01xx – JTAG和SWD接口

注意:可以为JTAG信号添加外部上拉/下拉电阻,以增加调试器连接的稳定性。

△图1 JTAG/SWD信号连接

03、调试连接器引脚布局

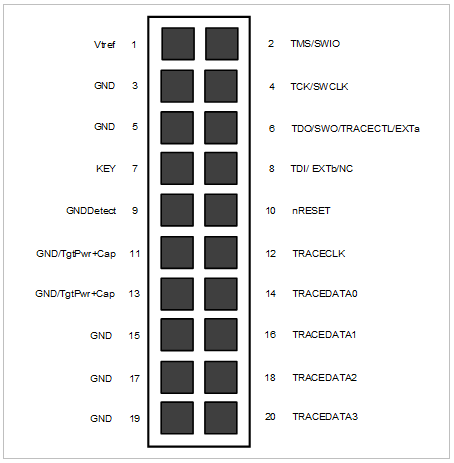

3.1 20针 Cortex Debug D ETM 连接器

部分较新的ARM微控制器板使用一个1.27mm间距的20针头(Samtec FTSH-110),用于调试和跟踪,20针Cortex Debug D ETM连接器支持JTAG和Serial-Wire调试协议。当使用Serial-Wire调试协议时,TDO信号可用于Serial-Wire观测器的输出,用于跟踪捕获。该连接器还提供了一个4位宽的跟踪端口,用于捕获有更高带宽需求的跟踪调试(例如,当ETM跟踪被启用时)。

△图2 20针Cortex Debug D ETM连接器引脚布局

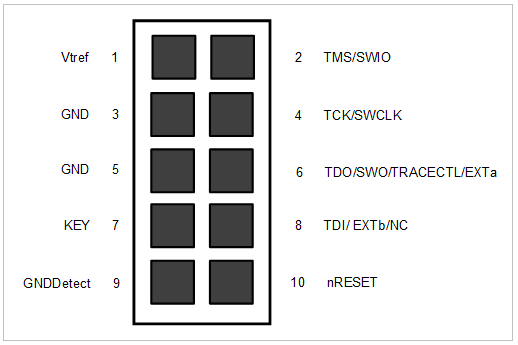

3.2 10针 Cortex 调试连接器

对于没有ETM的设备,可使用更小的1.27毫米间距的10针连接器(Samtec FTSH-105)进行调试。与20针的Cortex Debug D ETM连接器类似,10针版本的连接器同样支持JTAG和Serial-Wire调试协议。

△图3 10针Cortex调试连接器引脚布局

3.3 传统的20针 IDC 连接器

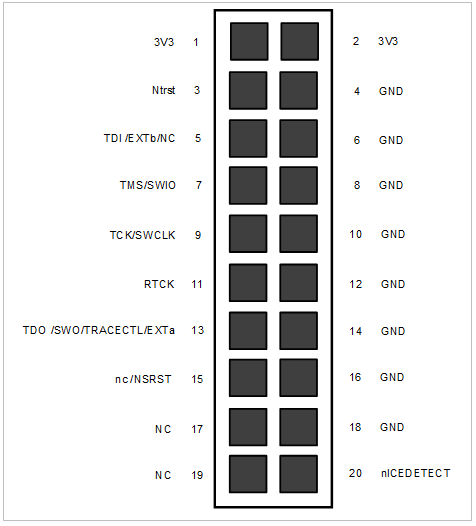

ARM开发板中常用的调试连接器是20针IDC连接器,20针IDC连接器支持JTAG调试、Serial-Wire调试(SWIO和SWCLK)、串行线输出(SWO)。

nICEDETECT引脚允许目标系统检测是否有调试器连接。当没有调试器连接时,该引脚被拉高,而调试器连接时将该引脚连接到地,常被使用在支持多种JTAG配置的开发板;nSRST连接是可选的,调试器可通过系统控制块(SCB)复位Cortex-M系统,所以此连接在做微控制器顶层设计时常被省略。

△图4 20针的IDC连接器

相关阅读:

来源:深圳曦华科技

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。