闩锁效应简介

可控管(SCR)是一种PNPN结构,是CMOS工艺的固有结构之一,它由NMOS的有源区、P衬底、N阱、PMOS的有源区构成SCR结构(PNPN结构),当其中一个三极管正偏时,就会构成正反馈形成闩锁。闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。避免闩锁的方法就是要减小衬底和N阱的寄生电阻,使寄生的三极管不会处于正偏状态。

静电是一种看不见的破坏力,会对电子元器件产生影响。静电放电(ESD)和相关的电压瞬变都会引起闩锁效应(latch-up),是半导体器件失效的主要原因之一。应该看到,如果有一个强电场施加在器件结构中的氧化物薄膜上,则该氧化物薄膜就会因介质击穿而损坏。很细的金属化迹线会由于大电流而损坏,并会由于浪涌电流造成的过热而形成开路。这就是所谓的“闩锁效应”。在闩锁情况下,器件在电源与地之间形成短路,造成大电流、EOS(电过载)和器件损坏。

由于MOS工艺含有许多内在的双极型晶体管,在CMOS工艺下,阱与衬底结合会导致寄生的n-p-n-p结构。这些结构会导致VDD和VSS线的短路,从而通常会破坏芯片,或者引起系统错误。

闩锁效应原理

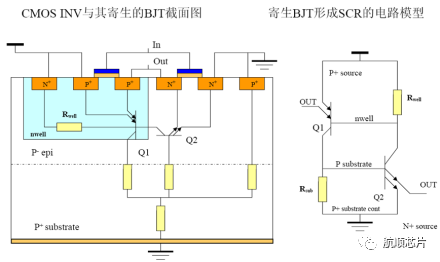

如下图所示,Q1为一垂直式PNP BJT(双极结型晶体管), 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一侧面式的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;其中,Rwell是nwell的寄生电阻;Rsub是substrate电阻。

闩锁效应的产生机理

①以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

②当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通(通常情况下是PNP比较容易触发起来),VDD至GND(VSS)间形成低抗通路。之后就算外界干扰消失,由于两三极管之间形成正反馈,还是会有电源和地之间的漏电,即锁定状态。闩锁效应(latch-up)由此而产生。

闩锁效应触发场景模拟

航顺HK32MCU的HK32F0系列和HK32F1系列之软硬件都兼容国外品牌MCU,已大批量应用于各种电子产品中。其工作电压支持2.0V~5.5V,为了方便模拟触发闩锁效应(latch-up),下面几个应用场景测试条件都是VCC=5.5V的工作电压。

场景一

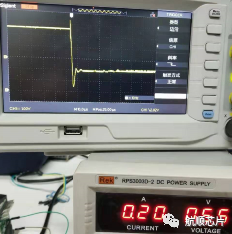

测试条件:VCC=5.5V,VCC脚没有去耦电容,所有GPIO悬空。

测试方法:给VCC快速上电

测试结果:触发闩锁效应(latch-up)

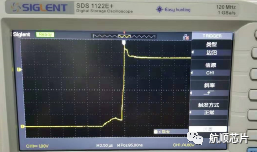

分析:如下图所示,VCC上电速度符合要求,理论不会触发Latch up,但从上电波形上看,上电后VCC有过冲至6V~7V,甚至更高,推测过冲触发闩锁效应(latch-up)。

场景二

测试条件:VCC=5.5V,VCC脚有0.1uF去耦电容,所有GPIO悬空。

测试方法:给VCC快速上电

测试结果:触发闩锁效应(latch-up)

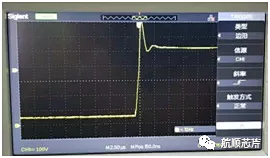

分析:VCC上电速度符合要求,但从上电波形上看,上电后VCC有过冲现象,甚至比场景一更严重,推测过冲触发闩锁效应(latch-up)。

场景三

测试条件:VCC=5.5V,VCC脚有0.1uF+1uF去耦电容,所有GPIO悬空。

测试方法:给VCC快速上电

测试结果:触发闩锁效应(latch-up)

分析:VCC上电速度符合要求,但从上电波形上看,上电后VCC仍有过冲至6V~7V现象,和接0.1uF去耦电容差别不大,推测过冲触发闩锁效应(latch-up)。

场景四

测试条件:VCC=5.5V,VCC脚有0.1uF+1uF去耦电容,所有GPIO悬空。

测试方法:给VCC快速下电(模拟外部强负载情形)

测试结果:触发闩锁效应(latch-up)

分析:VCC电压快速跌落,形成VCC下冲至过低现象,推测下冲触发闩锁效应(latch-up)。由于触发了闩锁效应(latch-up)以及设置了200mA限流, VCC无法重新恢复到5.5V。

场景五

测试条件:VCC=5.5V,VCC脚有0.1uF+1uF去耦电容,并串有1欧姆电阻,将某IO口直接接到电源。

测试方法:给VCC快速上电

测试结果:触发闩锁效应(latch-up)

分析:上电瞬间,IO口电压高于VCC,容易触发Latch up。

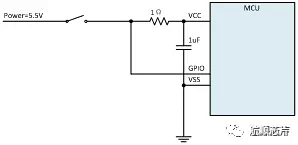

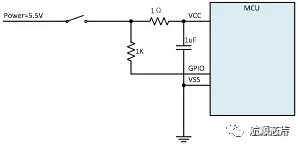

以上五种场景都是可能触发闩锁效应(latch-up)问题的场景,改善措施及参考原理图如下:

1. 抑制MCU端VCC在上电或下电瞬间产生过冲或下冲现象,在电源和芯片VCC之间串入1欧姆电阻,并在芯片VCC上加0.1uF和1uF去耦电容。

2.避免默认需要高电平的IO口直接接到电源现象,需要通过1K或以上的上拉电阻上拉至电源。

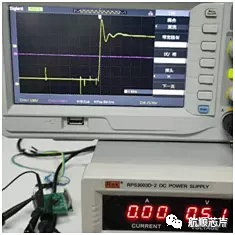

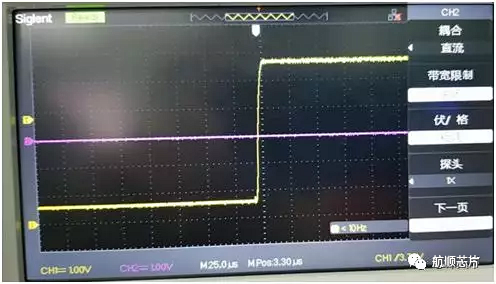

通过以上改善措施,测得VCC电源波形如下,由于有电阻和电容的抑制,VCC上没有出现过冲现象,测试结果完全不会触发触发闩锁效应(latch-up)。

闩锁效应预防措施总结

从上述闩锁效应的产生机理、触发场景模拟和改善措施的测试结果可以看到,触发闩锁效应(latch-up)问题的有很多的因素,要防止闩锁效应(latch-up),大致有两方面措施:一是从芯片的角度讲,可以通过芯片工艺的改进和设计的优化来消除闩锁的危险,二是从应用的角度讲,可以通过一些预防措施,降低触发闩锁效应(latch-up)的几率,具体如:

1)在输入端和输出端加钳位电路,使输入和输出不超过规定电压。

2)芯片的电源输入端加去耦电容,防止VCC端出现瞬间的高压。

3)在VCC和外电源之间加限流电阻,即使有大的电流也不让它进去。

4)当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启CMOS电路的电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭CMOS电路的电源。

相关阅读:

HK32MCU应用笔记(一)| HK32F030X系列在PH测量笔的应用

HK32MCU应用笔记(二)| 国外品牌采用航顺HK32F030R8T6代替出现串口不兼容解决方法

HK32MCU应用笔记(三)| 航顺芯片在5G光纤测试仪的应用

HK32MCU应用笔记(四)| 关于老版本HK32F103串口USART偶尔出现数据错误

HK32MCU应用笔记(五)| 关于应用HK32F030延时效率问题

HK32MCU应用笔记(六)| HK32MCU芯片调试心得

来源:航顺芯片

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。