一、NAND 闪存基本单元

NAND 单元结构

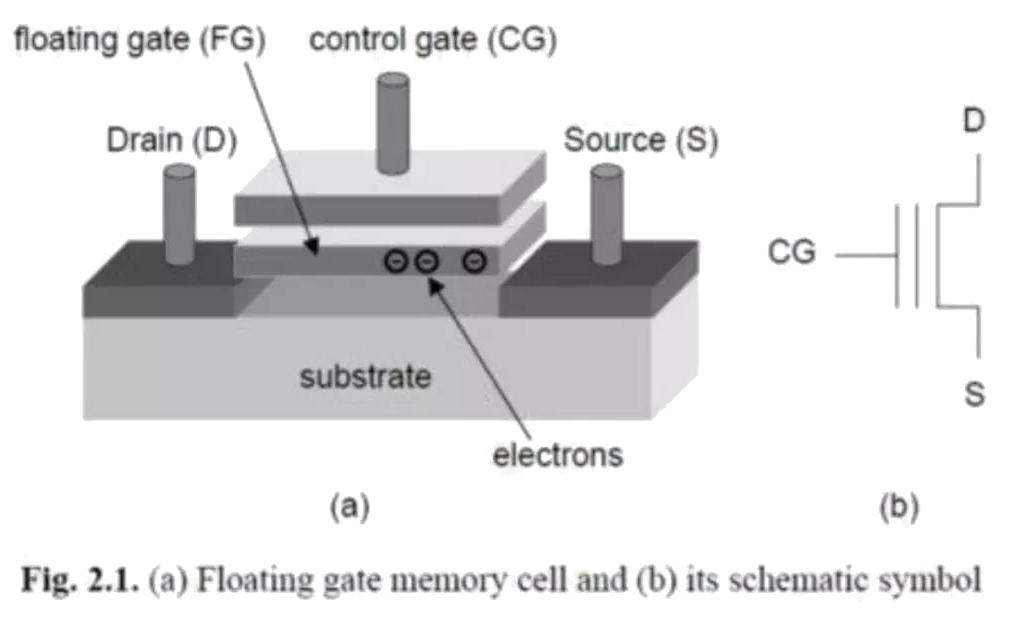

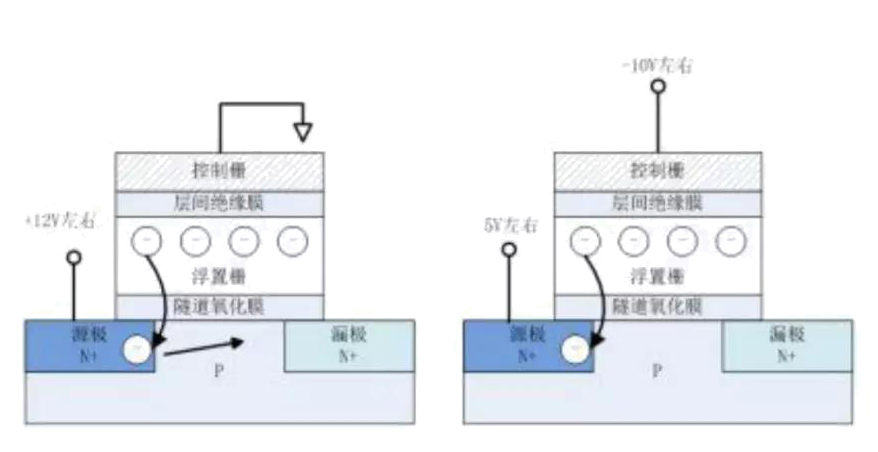

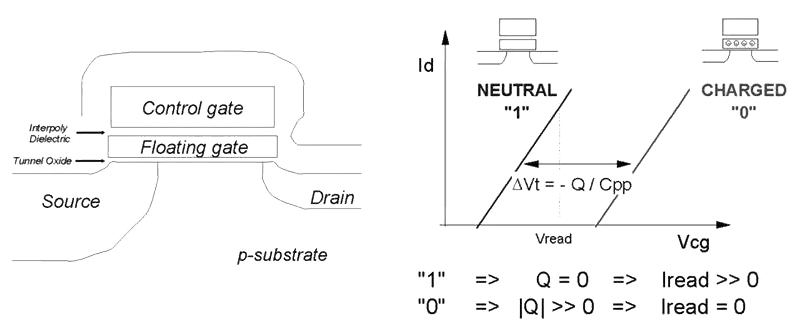

最流行的 Flash 存储器的存储方式是基于一种叫做: Floating Gate(FG)的技术,可以参考下面的横截图,一个 MOS 管是由两个重叠的门组成:第一个是完全被氧化物所包围; 而第二个则是被连接到外面。这个单独的门就相当于构成了一个电子隔离带,这样就保证存在里面的电子(数据)能够保留很多年。对这个被隔离起来的部分进行充电和放电的过程就叫做 program 和 erase。由于进行了充放电,所以这个隔离起来的部分内部的电势 Vth 就 会被改变;这就是一个典型的 MOS 管工作原理。当我们对一个存储单元施加上一个电压的 时候,我们就可以分别处两种情况:当我们施加的电压比 Vth 高的时候便被识别为“1”, 否则就被识别为“0”。

上面这么一段的描述,你一定还是没弄懂,这个图也是过于简略。

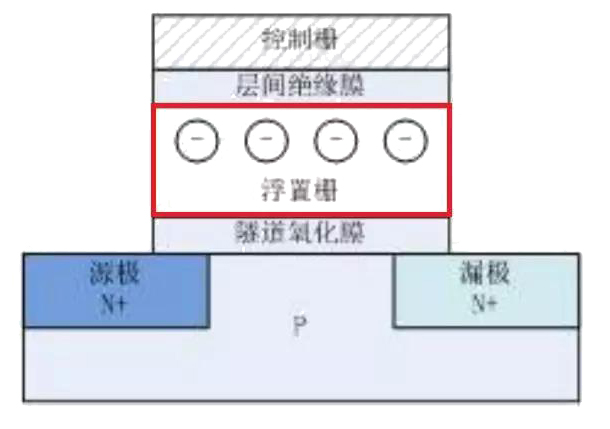

NAND 闪存内部存储结构单元是基于 MOSFET(金属-氧化层-半导体-场效应晶体管), 与普通场效应晶体管的不同之处在于,在栅极(控制栅)与漏极/源极之间存在浮置栅,利用该浮置栅存储数据。

数据在NAND Flash闪存中是以电荷的形式存储的,存储的电荷的多少,取决于控制栅极所施加的电压,栅极及主板利用氧化膜进行了绝缘处理,一次积累的电荷可以保持长时间,但是,如果氧化膜存在缺陷,或者由于某种原因是绝缘膜遭到破坏,那么闪存将失去记忆。

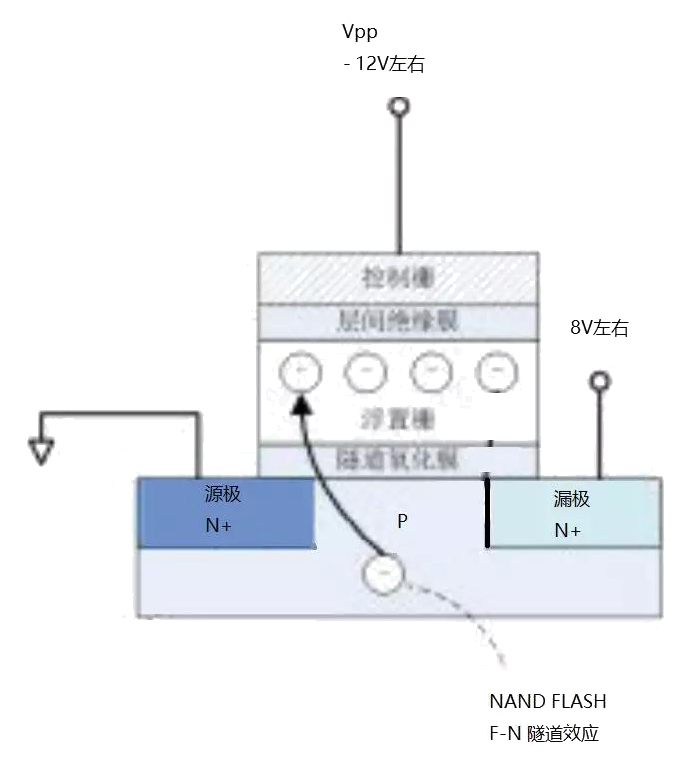

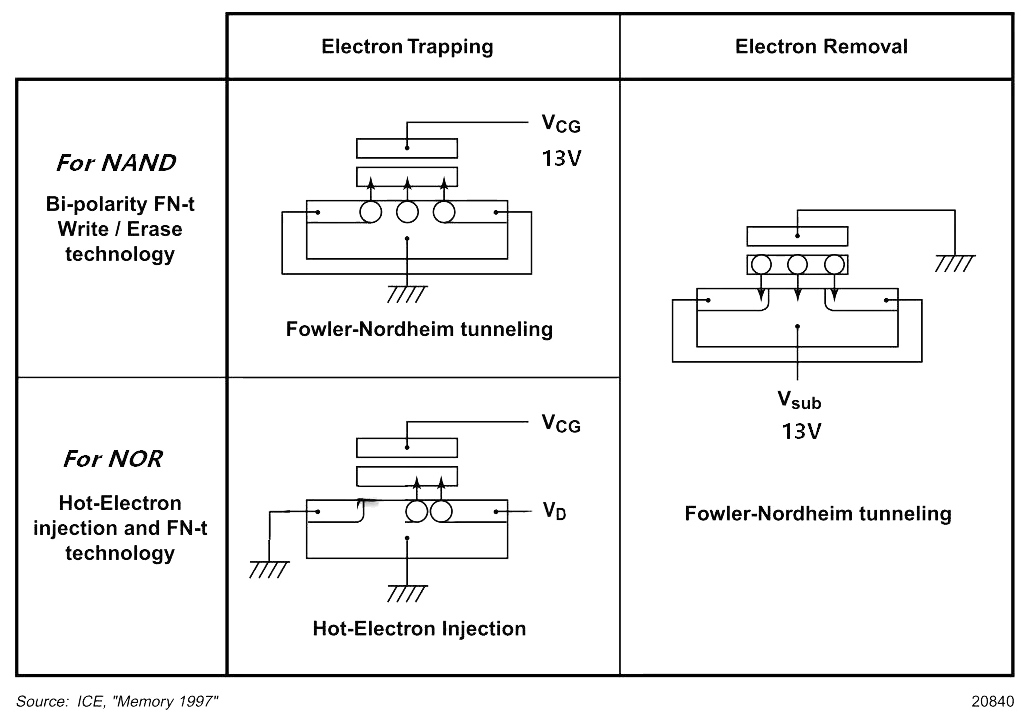

另外热能会使电荷以某种概率发生消减,因此数据保存的时间还受到温度(辐射等)的影响。 闪存数据的写入和擦除是通过主板与控制栅之间电荷的诸如与释放来进行的。在写入方式上,NOR Flash采用的是热电子注入方式,通过在写入的时候提高控制栅的电压,通过源极向浮置栅注入电荷,电流从浮置栅极到源极;而 NAND Flash 闪存利用 F-N 隧道效应, 通过硅基层给浮置栅充电,电流从浮置栅极到硅基层。

隧道效应:

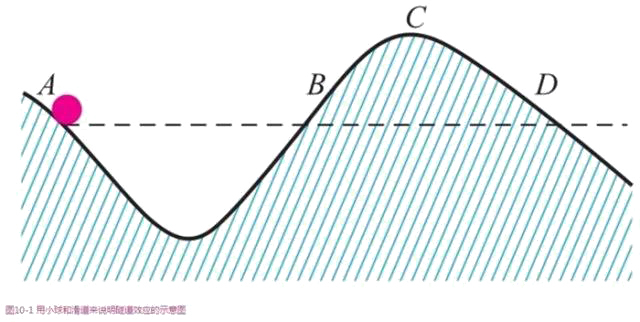

在讲隧道效应之前,我们先来看一个小实验。如图 10-1 所示,假设有一条像山坡一样高低起伏的滑道,滑道上有一个小球,二者之间没有任何摩擦力。如果我们让小球从 A 点出发滑落,而且出发时速度为零,那么小球最高能到达哪一点呢?

这太简单了,根据能量守恒定律,我们知道小球的势能会转化成动能,然后动能再转化成势能,最后会到达高度与 A 点相同的 B 点,如此往复运动。

如果我问你,这个小球会出现在 D 点吗?你一定会说,绝对不可能,因为 C 点是一座无法翻越的大山。或者说,C 点是一个能量很高的势垒,小球没有足够的能量来翻越它。

对于经典粒子来说,的确是这样的。但是,如果这条滑道缩小到原子尺度,而小球是一个电子的话,上述结论就不成立了。量子力学计算表明,从 A 点出发的电子有明显地出现在 D 点的概率,就像是从一条隧道中穿越过去的一样,这就是量子隧道效应,它是微观粒子波粒二象性的体现。

总结一下,如果微观粒子遇到一个能量势垒,即使粒子的能量小于势垒高度,它也有一定的概率穿越势垒,这种现象就叫隧道效应。隧道效应又称势垒贯穿,是一种很常见的量子效应。也就是说,崂山道士的故事在量子世界里是很平常的,一点都不稀奇。

当然,对于不同的情况,粒子在势垒外出现的概率大小是需要通过薛定谔方程仔细计算的。在一般情况下,只有当势垒宽度与微观粒子的德布罗意波长可比拟时,势垒贯穿的现象才能被显著观察到。如果势垒太高或太宽,隧穿的可能性就会变得很小。

所以在NAND FLASH的单元内部:

在没有外部的电压和温度变化的时候,势垒高且宽。电子是很难实现隧穿。

当外部电压变化时,或者温度变化时,此时隧穿就成为了大概率事件。

而数据的擦除都是利用 F-N 隧道效应放电,具体可以通过两种方法进行。一 种方法是通过给源极加上+12V 左右的高电压,释放浮置栅中的电荷;另一种方法是负极门擦除法,通过给控制栅-10V 左右的负电压,挤出浮置栅中的电荷。

读取数据的时候给控制栅加读取电压,对于浮置栅中有电荷的单元来讲,浮置栅中的电荷可抵消提供给控制栅的电压,造成阈值电压增高。与浮置栅中没有电荷时的情况相比,如果不给控制栅提供高电压,则漏极-源极之间不会处于导通的状态。因此,通过判断,通过向控制栅加读出电压,判断漏极-源极之间是否处于导通状态,可以判断浮置栅有没有存储 电荷,进而判断该存储单元是“1”还是“0”。

二、SLC 和 MLC

1、概述

NAND Flash 分为 SLC-单层存储(Single-Level Cell)和 MLC-多层存储(Multi-Level Cell)。

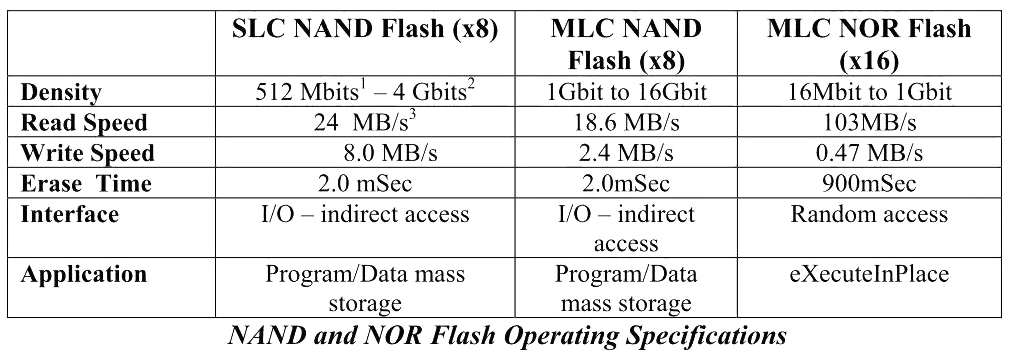

1、SLC = Single-Level Cell ,即1bit/cell,速度快寿命长,价格贵(约MLC的3倍以上的价格),约10万次擦写寿命。

2、MLC = Multi-Level Cell,即2bit/cell,速度一般寿命一般,价格一般,约3000—10000次擦写寿命。

3、TLC = Trinary-Level Cell,即3bit/cell,也有Flash厂家叫8LC,速度慢寿命短,价格便宜,约500次擦写寿命,目前还没有厂家能做到1000次。

由于TLC的1个存储器储存单元可存放3 bit的数据,为了区分,必须使用不同电压来实现。除了能够实现和SLC一样的000(TLC)=0(SLC)和111(TLC)=1(SLC)外、还有另外六种数据格式必须采用其他不同的电压来区分,让不同数量的电子进入到存储单元,实现不同的数据表达。这样,才能让TLC实现单位存储单元存放比SLC、MLC更多数据的目的。

SLC 就 是在 NAND Flash 闪存的每个存储单元里存储 1 比特的数据,而 MLC 则是每个存储单元 里存储 2 比特甚至更多的数据。SLC 与 MLC 的区别是由单个存储单元的电压范围所能够表示的不同数据的个数来区分的,如下图所示。

SLC 闪存中存储的数据代表”0”还是”1”是由基于 Vth 电压阈值来判定,对于 NAND 闪存的写入(编程),就是对其充电,使得它的电压超过上图的电压判定点 A,存储单元就 表示 0 已编程,如果没有充电或者电压阈值低于那个 A 点,就表示 1-已擦除。

MLC 闪存存储的数据是”00”,”01”,”10”,”11”也是基于电压阈值的判定,当电 压没到判定点 B 时,就代表”11”,当电压在 B 和 C 之间,则代表“10”,电压在 C 和 D 之间,则表示”01”,而电压达到 D 以上,则表示”00”。 相比 SLC,MLC 电压之间的阈值被分成了 4 份,这样一来就会直接影响 MLC 闪存的 性能和稳定性,对于 MLC 闪存来说,相邻的存储单元间会互相干扰,造成电压不稳定而出 现比特错误,MLC 由于阈值相比 SLC 更接近,所以出错几率会更大;MLC 读写性能降低, 写入更达到 50%的差距以上,因为需要更精确的充电处理。

SLC 只有”0”和”1”,,而 MLC 会有“00”,“01“,”10”,”11” 4 个状态,在充电后还要去判断处于哪个状态, 速度自然就慢了;因为有额外的读写压力,所以在功耗方面,MLC 相比 SLC 明显增大,并 且造成闪存的写入耐久度和数据保存期都受到影响。

三、FLASH基本存储单元的操作---写/擦除/读

FLASH中,常用的向浮栅注入电荷的技术有两种---NOR FLASH :热电子注入(hot electron injection)和NAND FLASH :F-N隧道效应(Fowler Nordheim tunneling);从浮栅中挪走电荷的技术通常使用F-N隧道效应(Fowler Nordheim tunneling)。第一章节,我们已经对原理进行了讲解。

写操作就是向浮栅注入电荷的过程,NOR FLASH通过热电子注入方式向浮栅注入电荷(这种方法的电荷注入效率较低,因此NOR FLASH的写速率较低),NAND FLASH则通过F-N隧道效应向浮栅注入电荷。FLASH在写操作之前,必须先将原来的数据擦除(即将浮栅中的电荷挪走),也即FLASH擦除后读出的都是‘1’。

擦除操作就是从浮栅中挪走电荷的过程,NOR FLASH和NAND FLASH都是通过F-N隧道效应将浮栅中的电荷挪走的。

读出操作时,控制栅极上施加的电压很小,不会改变浮栅中的电荷量,即读出操作不会改变FLASH中原有的数据,也即浮栅有电荷时,D和S间存在导电沟道,从D极读到‘0’;当浮栅中没有电荷时,D和S间没有导电沟道,从D极读到‘1’。

四、NOR FLASH 和NAND FLASH的结构和特性

1、 NOR FLASH的结构和特性

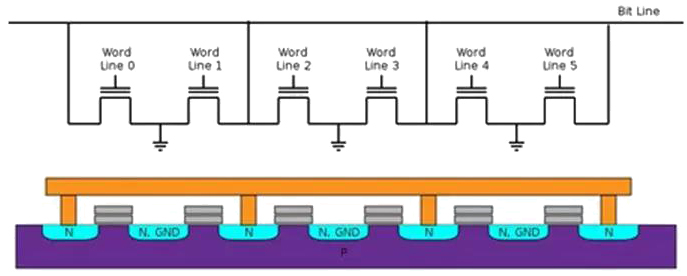

NOR FLASH的结构原理图见下图,可见每个Bit Line下的基本存储单元是并联的,当某个Word Line被选中后,就可以实现对该Word的读取,也就是可以实现位读取(即Random Access),且具有较高的读取速率,图3.1是一个3*8bit的NOR FLASH的原理结构图,图3.2是沿Bit Line切面的剖面图,展示了NOR FLASH的硅切面示意图,这种并联结构决定了NOR FLASH的很多特性。

(1)基本存储单元的并联结构决定了金属导线占用很大的面积,因此NOR FLASH的存储密度较低,无法适用于需要大容量存储的应用场合,即适用于code-storage,不适用于data-storage,见下图。

(2)基本存储单元的并联结构决定了NOR FLASH具有存储单元可独立寻址且读取效率高的特性,因此适用于code-storage,且程序可以直接在NOR 中运行(即具有RAM的特性)。

(3)NOR FLASH写入采用了热电子注入方式,效率较低,因此NOR写入速率较低,不适用于频繁擦除/写入场合。

NOR FLASH的中的N是NOT,含义是Floating Gate中有电荷时,读出‘0’,无电荷时读出‘1’,是一种‘非’的逻辑;OR的含义是同一个Bit Line下的各个基本存储单元是并联的,是一种‘或’的逻辑,这就是NOR 的由来。

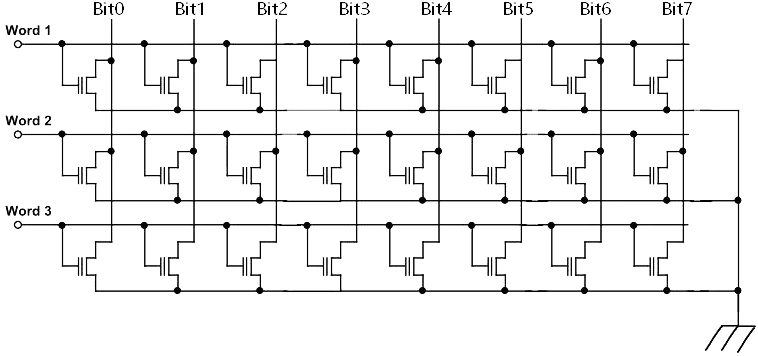

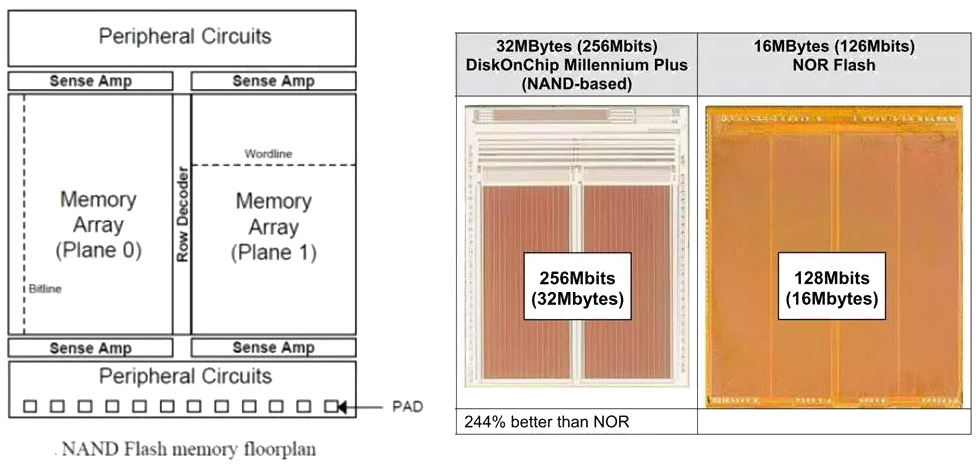

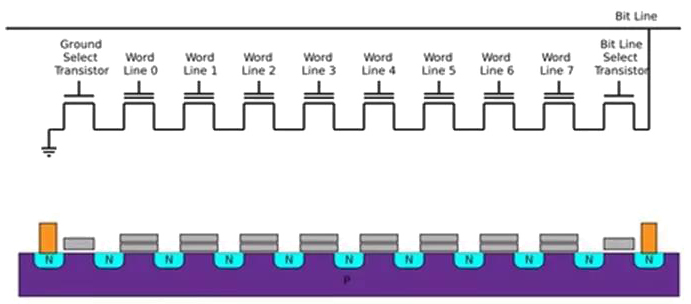

2、NAND FLASH的结构和特性

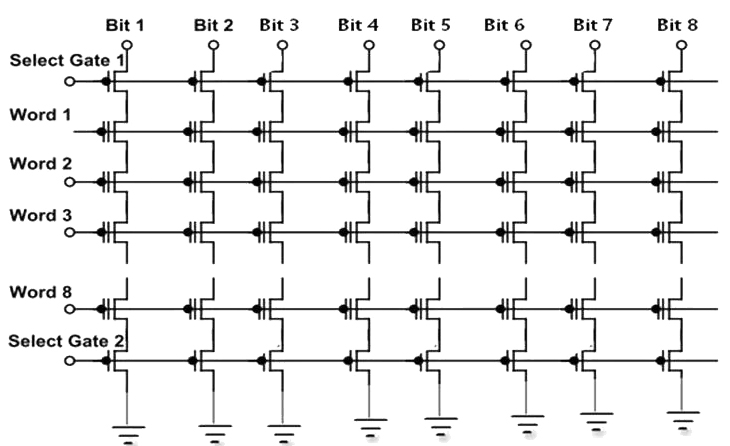

NAND FLASH的结构原理图见下图,可见每个Bit Line下的基本存储单元是串联的,NAND读取数据的单位是Page,当需要读取某个Page时,FLASH 控制器就不在这个Page的Word Line施加电压,而对其他所有Page的Word Line施加电压(电压值不能改变Floating Gate中电荷数量),让这些Page的所有基本存储单元的D和S导通,而我们要读取的Page的基本存储单元的D和S的导通/关断状态则取决于Floating Gate是否有电荷,有电荷时,Bit Line读出‘0’,无电荷Bit Line读出‘1’,实现了Page数据的读出,可见NAND无法实现位读取(即Random Access),程序代码也就无法在NAND上运行。

下图是一个8*8bit的NAND FLASH的原理结构图。

下图是沿Bit Line切面的剖面图,展示了NAND FLASH的硅切面示意图,NAND FLASH的串联结构决定了其很多特点。

(1)基本存储单元的串联结构减少了金属导线占用的面积,Die的利用率很高,因此NAND FLASH存储密度高,适用于需要大容量存储的应用场合,即适用于data-storage,见图3.3[3]。

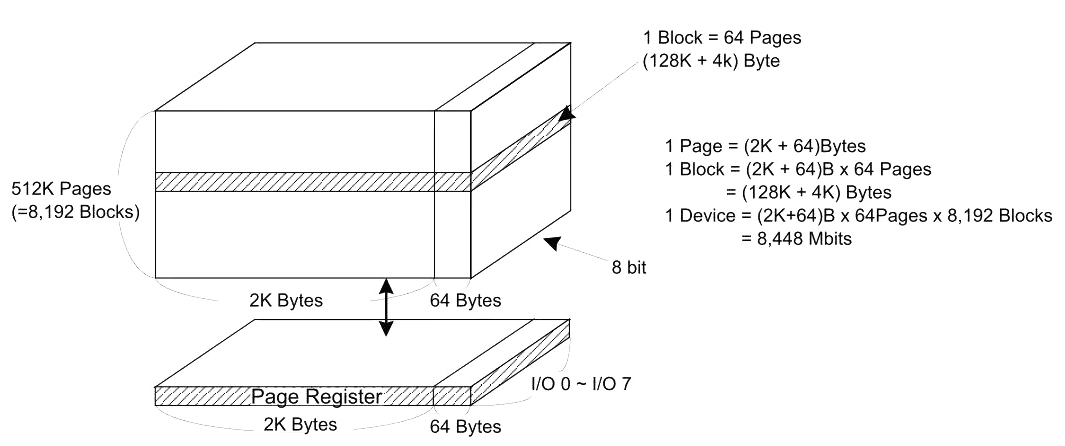

(2)基本存储单元的串联结构决定了NAND FLASH无法进行位读取,也就无法实现存储单元的独立寻址,因此程序不可以直接在NAND 中运行,因此NAND是以Page为读取单位和写入单位,以Block为擦除单位,见图3.6。

(3)NAND FLASH写入采用F-N隧道效应方式,效率较高,因此NAND擦除/写入速率很高,适用于频繁擦除/写入场合。同时NAND是以Page为单位进行读取的,因此读取速率也不算低(稍低于NOR)。

NAND FLASH的中的N是NOT,含义是Floating Gate中有电荷时,读出‘0’,无电荷时读出‘1’,是一种‘非’的逻辑;AND的含义是同一个Bit Line下的各个基本存储单元是串联的,是一种‘与’的逻辑,这就是NAND 的由来。

3、通过对NOR和NAND结构和特点的解析,我们可以得出

五、NAND FLASH应用

1、oob / Redundant Area / Spare Area

每一个页,对应还有一块区域,叫做空闲区域(spare area)/冗余区域(redundant area),而Linux系统中,一般叫做OOB(Out Of Band),这个区域,是最初基于Nand Flash的硬件特性:数据在读写时候相对容易错误,所以为了保证数据的正确性,必须要有对应的检测和纠错机制,此机制被叫做EDC(Error Detection Code)/ECC(Error Code Correction, 或者 Error Checking and Correcting),所以设计了多余的区域,用于放置数据的校验值。

Oob的读写操作,一般是随着页的操作一起完成的,即读写页的时候,对应地就读写了oob。

关于oob具体用途,总结起来有:

- 标记是否是坏快

- 存储ECC数据

- 存储一些和文件系统相关的数据。如jffs2就会用到这些空间存储一些特定信息,而yaffs2文件系统,会在oob中,存放很多和自己文件系统相关的信息。

2、Bad Block Management坏块管理

Nand Flash由于其物理特性,只有有限的擦写次数,超过那个次数,基本上就是坏了。在使用过程中,有些Nand Flash的block会出现被用坏了,当发现了,要及时将此block标注为坏块,不再使用。于此相关的管理工作,属于Nand Flash的坏块管理的一部分工作。

3、Wear-Leveling负载平衡

Nand Flash的block管理,还包括负载平衡。

正是由于Nand Flash的block,都是有一定寿命限制的,所以如果你每次都往同一个block擦除然后写入数据,那么那个block就很容易被用坏了,所以我们要去管理一下,将这么多次的对同一个block的操作,平均分布到其他一些block上面,使得在block的使用上,相对较平均,这样相对来说,可以更能充分利用Nand Flash。

4、ECC错误校验码

Nand Flash物理特性上使得其数据读写过程中会发生一定几率的错误,所以要有个对应的错误检测和纠正的机制,于是才有此ECC,用于数据错误的检测与纠正。Nand Flash的ECC,常见的算法有海明码和BCH,这类算法的实现,可以是软件也可以是硬件。不同系统,根据自己的需求,采用对应的软件或者是硬件。

相对来说,硬件实现这类ECC算法,肯定要比软件速度要快,但是多加了对应的硬件部分,所以成本相对要高些。如果系统对于性能要求不是很高,那么可以采用软件实现这类ECC算法,但是由于增加了数据读取和写入前后要做的数据错误检测和纠错,所以性能相对要降低一些,即Nand Flash的读取和写入速度相对会有所影响。

其中,Linux中的软件实现ECC算法,即NAND_ECC_SOFT模式,就是用的对应的海明码。

而对于目前常见的MLC的Nand Flash来说,由于容量比较大,动辄2GB,4GB,8GB等,常用BCH算法。BCH算法,相对来说,算法比较复杂。

BCH算法,通常是由对应的Nand Flash的Controller中,包含对应的硬件BCH ECC模块,实现了BCH算法,而作为软件方面,需要在读取数据后,写入数据之前,分别操作对应BCH相关的寄存器,设置成BCH模式,然后读取对应的BCH状态寄存器,得知是否有错误,和生成的BCH校验码,用于写入。

其具体代码是如何操作这些寄存器的,由于是和具体的硬件,具体的nand flash的controller不同而不同,无法用同一的代码。如果你是nand flash驱动开发者,自然会得到对应的起nand flash的controller部分的datasheet,按照手册说明,去操作即可。

不过,额外说明一下的是,关于BCH算法,往往是要从专门的做软件算法的厂家购买的,但是Micron之前在网上放出一个免费版本的BCH算法。

5、位反转

Nand Flash的位反转现象,主要是由以下一些原因/效应所导致:

漂移效应(Drifting Effects)

漂移效应指的是,Nand Flash中cell的电压值,慢慢地变了,变的和原始值不一样了。

编程干扰所产生的错误(Program-Disturb Errors)

此现象有时候也叫做,过度编程效应(over-program effect)。

对于某个页面的编程操作,即写操作,引起非相关的其他的页面的某个位跳变了。

读操作干扰产生的错误(Read-Disturb Errors)

此效应是,对一个页进行数据读取操作,却使得对应的某个位的数据,产生了永久性的变化,即Nand Flash上的该位的值变了。

对应位反转的类型,Nand Flash位反转的类型和解决办法,有两种:

一种是nand flash物理上的数据存储的单元上的数据,是正确的,只是在读取此数据出来的数据中的某位,发生变化,出现了位反转,即读取出来的数据中,某位错了,本来是0变成1,或者本来是1变成0了。此处可以成为软件上位反转。此数据位的错误,当然可以通过一定的校验算法检测并纠正。

另外一种,就是nand flash中的物理存储单元中,对应的某个位,物理上发生了变化,原来是1的,变成了0,或原来是0的,变成了1,发生了物理上的位的数据变化。此处可以成为硬件上的位反转。此错误,由于是物理上发生的,虽然读取出来的数据的错误,可以通过软件或硬件去检测并纠正过来,但是物理上真正发生的位的变化,则没办法改变了。不过个人理解,好像也是可以通过擦除Erase整个数据块Block的方式去擦除此错误,不过在之后的Nand Flash的使用过程中,估计此位还是很可能继续发生同样的硬件的位反转的错误。

以上两种类型的位反转,其实对于从Nand Flash读取出来的数据来说,解决其中的错误的位的方法,都是一样的,即通过一定的校验算法,常称为ECC,去检测出来,或检测并纠正错误。

如果只是单独检测错误,那么如果发现数据有误,那么再重新读取一次即可。

实际中更多的做法是,ECC校验发现有错误,会有对应的算法去找出哪位错误并且纠正过来。

其中对错误的检测和纠正,具体的实现方式,有软件算法,也有硬件实现,即硬件Nand Flash的控制器controller本身包含对应的硬件模块以实现数据的校验和纠错的。

Nand Flash引脚功能的中文说明

在数据手册中,你常会看到,对于一个引脚定义,有些字母上面带一横杠的,那是说明此引脚/信号是低电平有效,比如你上面看到的RE头上有个横线,就是说明,此RE是低电平有效,此外,为了书写方便,在字母后面加“#”,也是表示低电平有效,比如我上面写的CE#;如果字母头上啥都没有,就是默认的高电平有效,比如上面的CLE,就是高电平有效。

本文参考和引用文档如下:

《NAND FLASH1》百度文库 作者不详

《NAND Flash 和 NOR Flash原理和差异对比》CSDN xzengwei1313

《Nand flash 三种类型SLC,MLC,TLC》CSDN fc34235

《隧道效应:穿墙而过不是梦》书问

来源: 硬件十万个为什么