随着电子技术的发展,电磁兼容性问题成为电路设计工程师极为关注和棘手的问题。 根据多年的工程经验,大家普遍认为电磁兼容性标准中最重要的也是最难解决的两个项目就是传导发射和辐射发射。为了满足传导发射限制的要求,通常使用电磁干扰(EMI)滤波器来抑制电子产品产生的传导噪声。但是怎么选择一个现有的滤波器或者设计一个能满足需要的滤波器?工程师表现得很盲目,只有凭借经验作尝试。首先根据经验使用一个滤波器,如果不能满足要求再重新修改设计或者换另一个新的滤波器。因此,要找到一个合适的EMI滤波器就成为一个费时且高成本的任务。

电子系统产生的干扰特性

解决问题首先要了解电子系统产生的总干扰情况,需要抑制多少干扰电压才能满足标准要求?共模干扰是多少,差模干扰是多少?只有明确了这些干扰特性我们才能根据实际的需要提出要求。

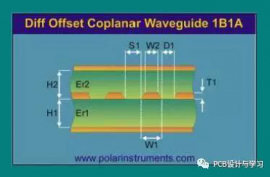

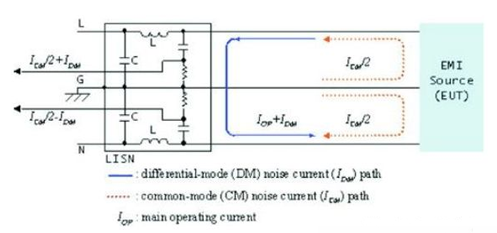

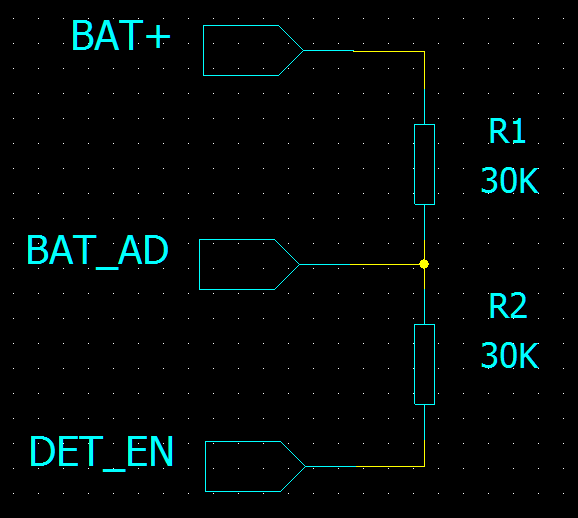

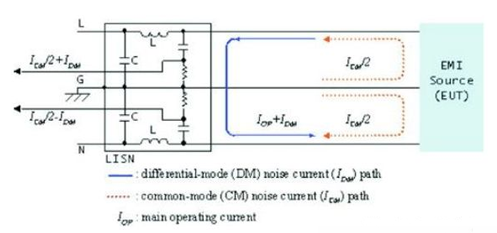

从被测物体的电流路径来看,干扰信号回流路径可能通过地线,或者通过其它电网,如图1所示。通过地线的干扰电流在电源网上产生同相位的共模干扰电压。通过其它线在两根电源线上产生反相的差模干扰电压。干扰电流的路径如图2所示。

图1 干扰信号的回流路径

图1 干扰信号的回流路径

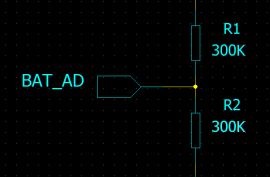

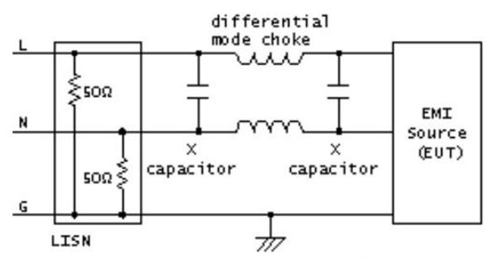

图2 a)差模干扰滤波和b)共模干扰滤波

图2 a)差模干扰滤波和b)共模干扰滤波

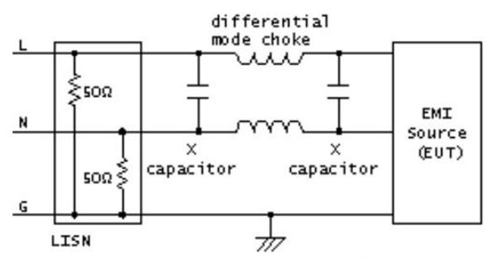

通常有四种技术可进行电源滤波,以便抑制干扰噪声。在实际使用中,经常是混合使用其中的两种,甚至多种技术。它们是:

• 正负极电源线之间添加电容,即X电容;

• 每根电源线和地线之间添加电容,即Y电容;

• 共模抑制(两根电源线上的抑制线圈同向绕线);

• 差模抑制(每根电源线有它自己的抑制线圈)。

电容的作用是将高频干扰电压“短路”,另外,当干扰信号频率很高时,抑制线圈将产生很大的交流阻抗。图2显示了两种滤波类型的结构,其中,LISN是用于测量目的的线性阻抗稳定网络。如果是共模问题引起的干扰,X类型电容基本上没有作用,因为两线上的干扰电压是一样的。因此,了解干扰类型对于选择合理的电路结构将起重要作用,并为解决问题提供技术依据。

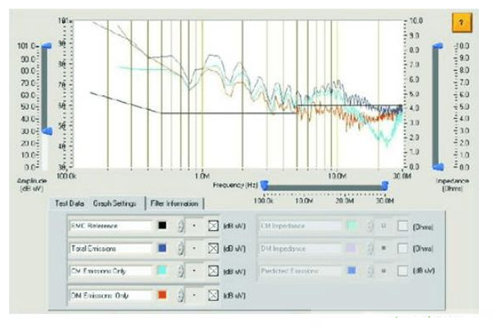

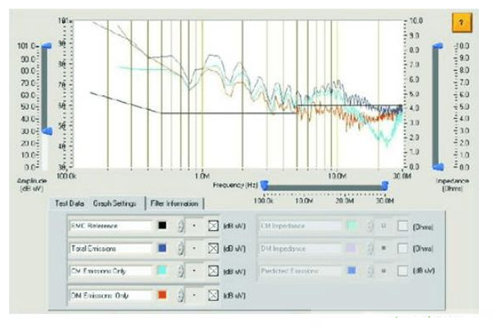

在标准电磁兼容性测试实验室可得到设备的总干扰情况,但无法了解设备的共模干扰和差模干扰特性。为了在测量中分辨共模或者差模干扰信号,通用的仪器是很难实现的。使用专用的传导测试仪,可获得设备的总干扰、共模干扰和差模干扰。测试结果如图3所示。

图3 传统测试仪获得的总干扰、共模干扰和差模干扰

图3 传统测试仪获得的总干扰、共模干扰和差模干扰

电源输入阻抗特性

滤波器的制造商给出的滤波器插损是在50W标准阻抗系统中的性能。众所周知,电源的输入阻抗随着频率的变化具有不连续性。阻抗的改变导致滤波器的插损特性产生很大的变化。

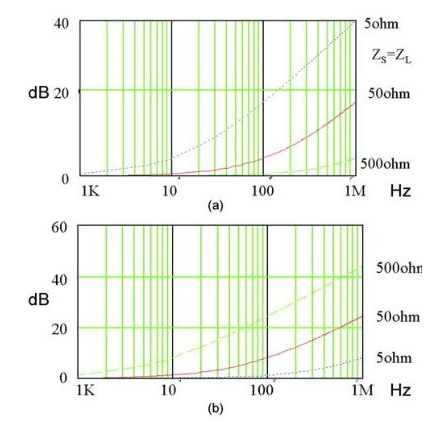

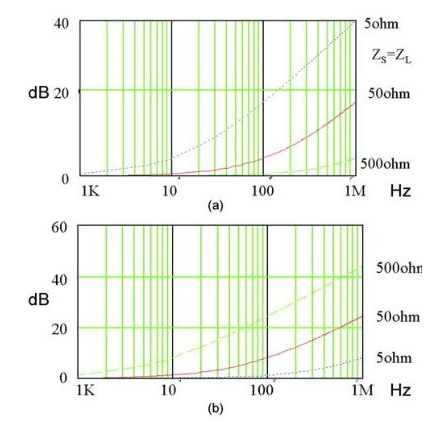

由图4可见,在一个50W的系统中,100mH的滤波器提供约18dB的衰减,但是在一个500W系统中只提供约4dB的衰减。 同样对于100nF电容器;在50W系统中,1MHz时大约23dB的衰减在5W系统中降至7dB。

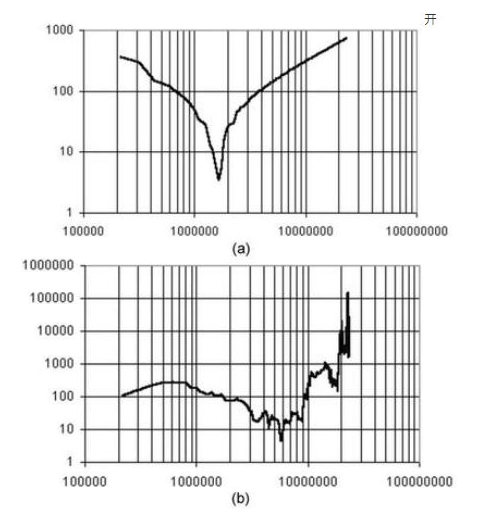

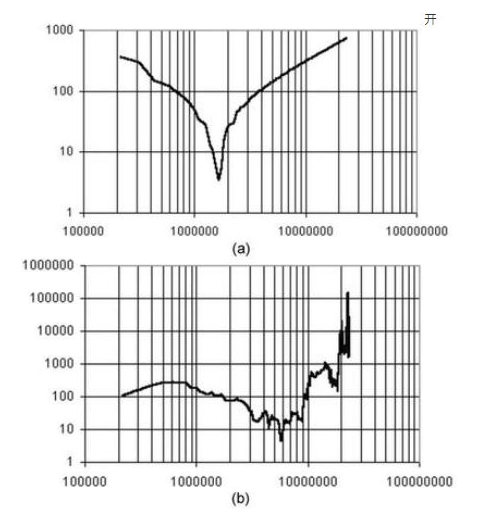

上面的例子说明,选择一个具有很高插损的滤波器也不能很好抑制传导噪声的原因是,电源输入端阻抗的影响。因此,设计者除了选择一个合适的滤波器之外,还需要了解电源的阻抗特性、共模阻抗和差模阻抗。阻抗测试可以借助专用的阻抗测试仪或者传导分析仪。一种滤波器的共模阻抗(a)和差模阻抗(b)的变化如图5所示。

图4 a)100uh电感的衰减 b)100nF电容器的衰减

图4 a)100uh电感的衰减 b)100nF电容器的衰减

图5 a)共模阻抗和b)差模阻抗的变化

图5 a)共模阻抗和b)差模阻抗的变化

滤波器的设计

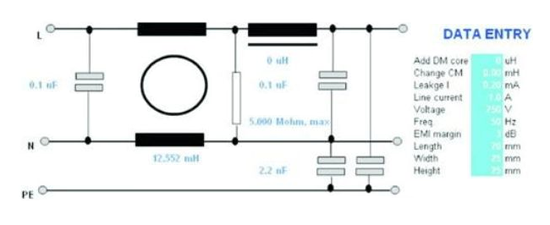

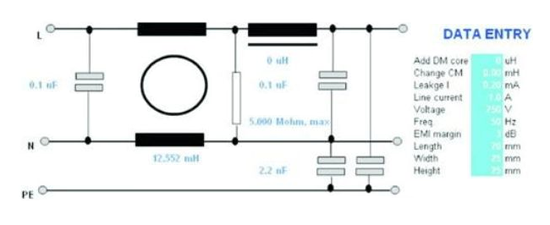

知道设备的干扰特性和输入阻抗特性后,设计或者选择一个滤波器就变得简单了。如果使用一个现成的滤波器,可以调用过去积累的滤波器数据库,比对滤波器参数,找到一个合适的滤波器。如果没有合适的或者想专门设计一个专用滤波器,可以借助专用的滤波器设计软件。在确定一个滤波器模式后输入滤波器一些简单的约束条件,设计软件根据阻抗特性自动计算出最合适的组件值,以及提供最合适的衰减。(如图6所示)

图6 一种由软件设计的最佳滤波器

图6 一种由软件设计的最佳滤波器

设计结果

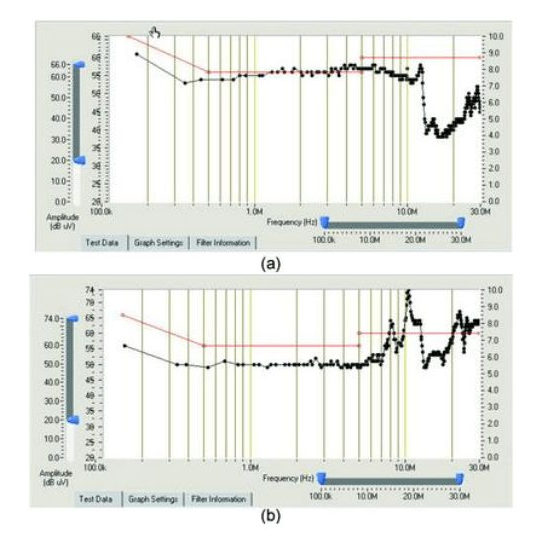

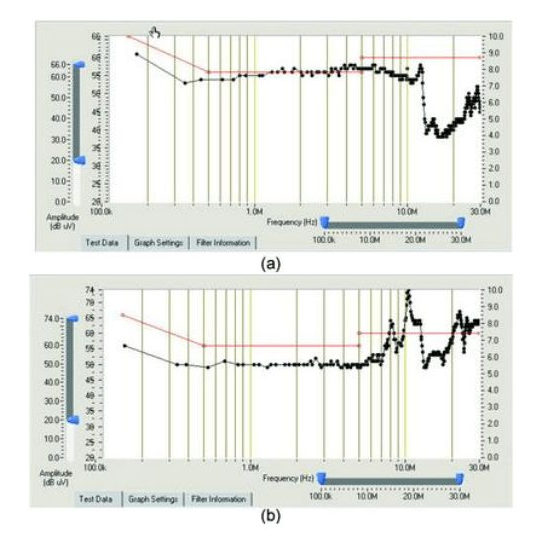

在对某产品进行了干扰特性和阻抗特性测试后,需要解决一个低于5MHz的低频干扰问题。专用滤波器设计软件结合前面得到的测试数据给出了滤波器的元件参数:包括470nF的X电容器,2.2nF的Y电容器和15.1mH的共模电感。但是有经验的滤波器设计人员认为采用一个13.5mH共模电感的滤波器是足够了。使用一个13.5mH包括额外高频组件的滤波器的发射情况如图7所示。

图7 最小15mH的系统使用和18mH时的测试结果

图7 最小15mH的系统使用和18mH时的测试结果

为了验证软件的设计数据,将470nF、2.2nF和18mH的非定制的滤波器迅速连接到系统中,获得中心频率小于5MHz,并且无需高频滤波器。结果清楚地表明,最小15mH的限制是合适的。

结语

EMI滤波器的设计应该充分考虑干扰特性和阻抗特性,在阻抗测试和干扰特性测试数据基础上进行设计是精确滤波设计的唯一方法。

来源:网络