Microchip推出容量更大、速度更快的串行SRAM产品线

为满足客户对更大更快的 SRAM 的普遍需求,Microchip Technology(微芯科技公司)扩展了旗下串行SRAM产品线,容量最高可达4 Mb,并将串行外设接口/串行四通道输入/输出接口(SPI/SQI™)的速度提高到143 MHz。

为满足客户对更大更快的 SRAM 的普遍需求,Microchip Technology(微芯科技公司)扩展了旗下串行SRAM产品线,容量最高可达4 Mb,并将串行外设接口/串行四通道输入/输出接口(SPI/SQI™)的速度提高到143 MHz。

01、问题的描述

某客户使用 STM32G071 芯片从 standby 模式下唤醒,想要 SRAM 的数据在退出 standby模式后得以保持。根据手册的描述,配置了相应的比特位,但是发现数据仍然保持不了。

本期开发笔记由费神编写主要会为大家介绍HPM6000系列的各类片上SRAM并结合Segger Embedded Studio的linker文件介绍,提供了如何使用这些SRAM的建议,赶快来了解吧~

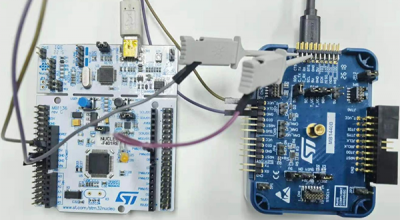

本文档主要介绍利用 STLINK-V3SET 调试/编程工具的 I2C 接口将程序下载到 SDRAM 中并执行的方法。

常见存储器概念:RAM、SRAM、SDRAM、ROM、EPROM、EEPROM、Flash。存储器可以分为很多种类,其中根据掉电数据是否丢失可以分为RAM(随机存取存储器)和ROM(只读存储器),其中RAM的访问速度比较快,但掉电后数据会丢失,而ROM掉电后数据不会丢失。

作者: Avi Avanindra,Devardhi Mandya,Cypress