OTGFS介绍

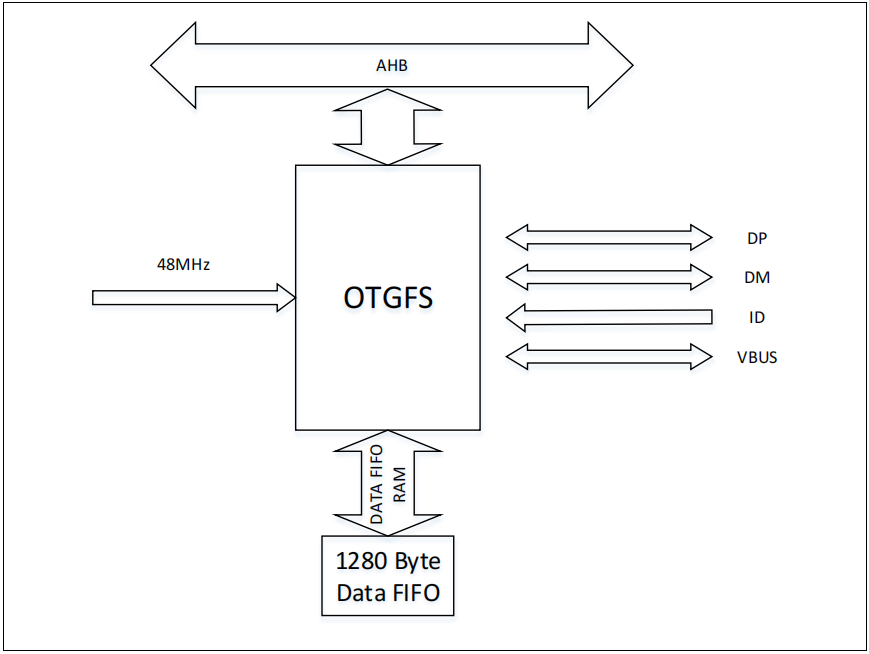

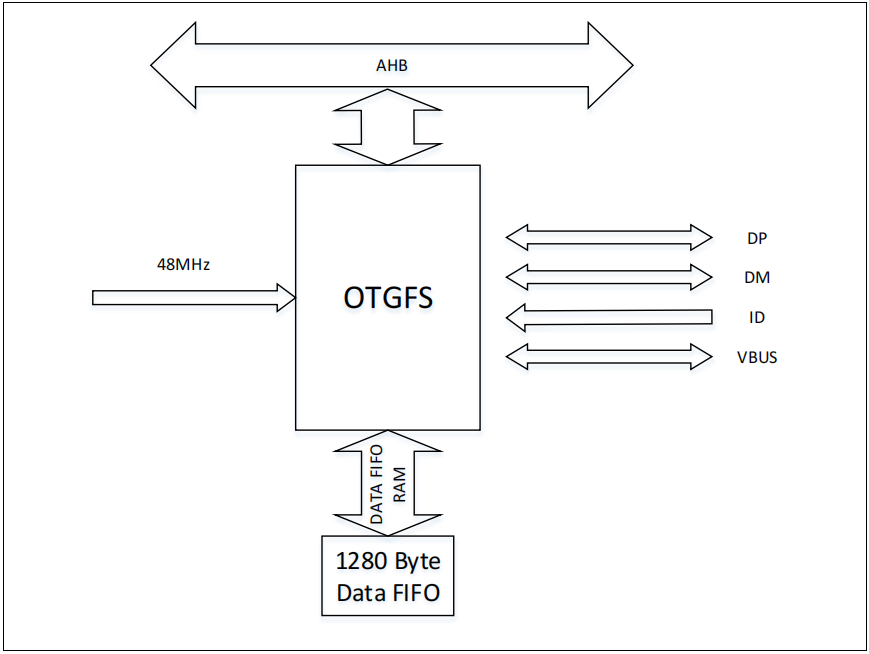

AT32F435/437包含2个独立的OTGFS,编号OTGFS1和OTGFS2,本章将描述OTGFS支持的一些基本功能。OTGFS1和OTGFS2特性完全相同。

图1 OTGFS框图

OTGFS特性

OTGFS通用特性:

OTGFS设备模式特性:

仅支持全速设备

支持内部1.5KΩ上拉

支持软件断开连接

支持1个双向控制端点0

支持7个IN端点,端点号1-7

支持7个OUT端点,端点号1-7

支持控制传输,大容量传输,中断传输,同步传输

端点接收FIFO共享

端点发送FIFO专用

支持无晶振(crystal-less)

OTGFS主机模式特性:

支持全速和低速

支持内部15KΩ下拉

支持16个主机通道

支持控制传输,大容量传输,中断传输,同步传输

通道接收FIFO共享

通道发送FIFO专用

OTGFS全速PHY

OTGFS内置支持全速/低速的PHY,为主机和设备模式提供通信支持。

1、DP和DM内置上下拉电阻,由OTGFS根据模式自动使能上下拉电阻

当OTGFS处于设备模式时,DP 1.5KΩ上拉自动使能

当OTGFS处于主机模式时,DP和DM 15KΩ下拉自动使能

2、ID线内置上拉

ID线为高电平,默认为设备模式

ID线为低电平,为主机模式

3、设备模式下的VBUS检测(可忽略VBUS检测)

设备模式下,仅支持VBUS高低电平检测,当VBUS为高电平,OTGFS认为是有效电平,将使能DP的上拉电阻,让主机识别到设备插入。当VBUS为低电平,OTGFS认为是无效电平,此时不使能DP上拉,处于断开模式。

在设备模式下,如果想不检测VBUS,可通过设置寄存器OTGFS_GCCFG.VBUSIG=1来实现,此时可将检测VBUS的引脚释放出来给其它外设使用。

4、PHY的低功耗模式

OTGFS全速PHY支持低功耗模式,可以通过设置寄存器OTGFS_GCCFG.LP_MODE=1让PHY处于低功耗模式。

OTGFS GPIO引脚

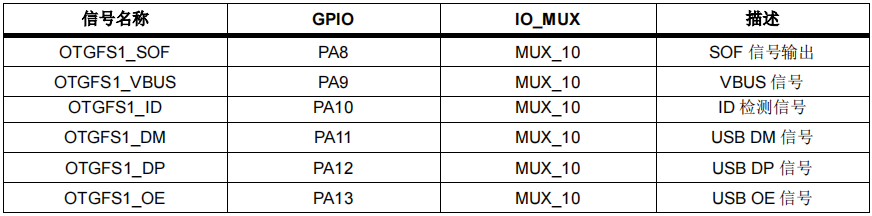

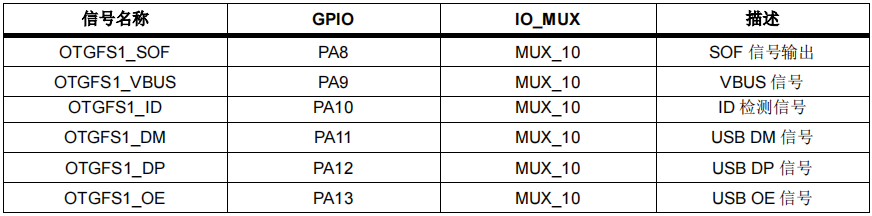

435/437 OTGFS1/2使用GPIO引脚如下表所示:

表1 OTGFS1 GPIO引脚

表2 OTGFS2 GPIO引脚

注:USB_OE信号当USB在传输数据时,会翻转此信号

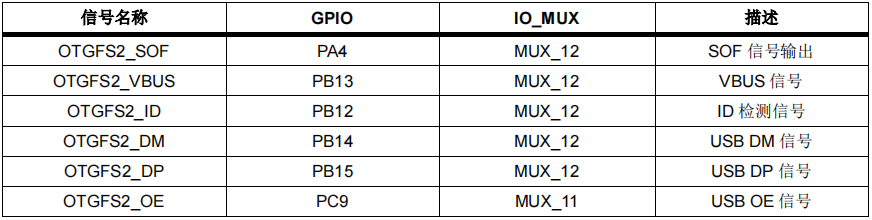

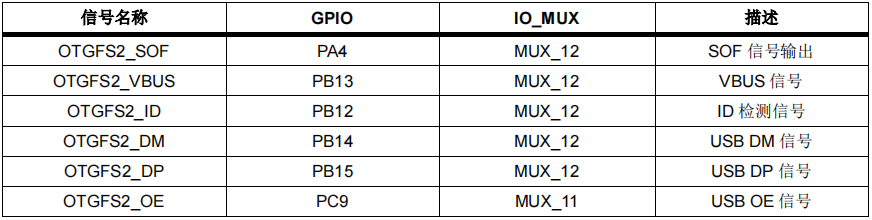

OTGFS 48MHz时钟

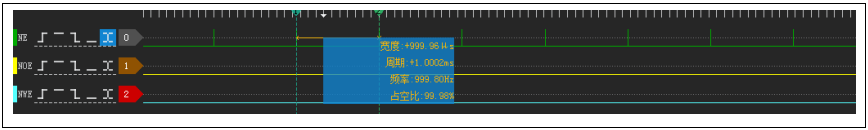

需要给OTGFS提供48MHz±0.25%的时钟来用于USB总线采样。48MHz时钟可以直接来源HICK,也可以通过PLLCLK分频得到。

图2 USB 48MHz时钟来源

注意:当OTGFS作为HOST时,必须使用外部晶振通过PLL分频作为USB 48MHz时钟。

USB时钟选择HICK

通过设置如下寄存器选择HICK:

1、CRM_MISC1. HICKDIV=1;

HICK是否分频,1表示不分频,0表示6分频

2、CRM_MISC1. HICK_TO_USB=1;

1 表示USB 48MHz时钟来源是HICK,0表示来源为PLL分频。

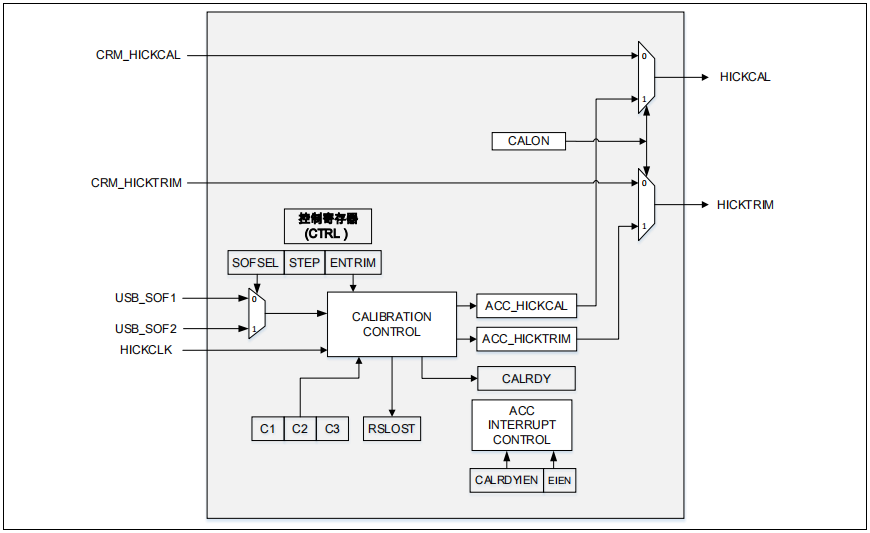

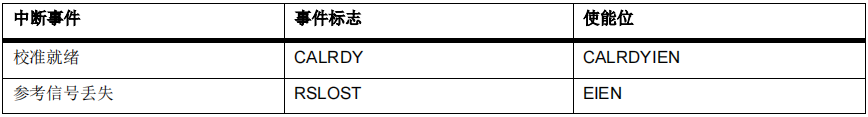

如果USB 48MHz时钟来源选择HICK时,在设备模式下需要开启ACC(HICK自动校准)功能,ACC功能利用USB产生的SOF信号来作为参考信号,实现对HICK时钟的采样和校准。详细功能可参考RM HICK自动时钟校准(ACC)章节。

注意:当OTGFS作为HOST时,必须使用外部晶振通过PLL分频作为USB 48MHz时钟,因为在HOST模式下不能通过ACC校准HICK。

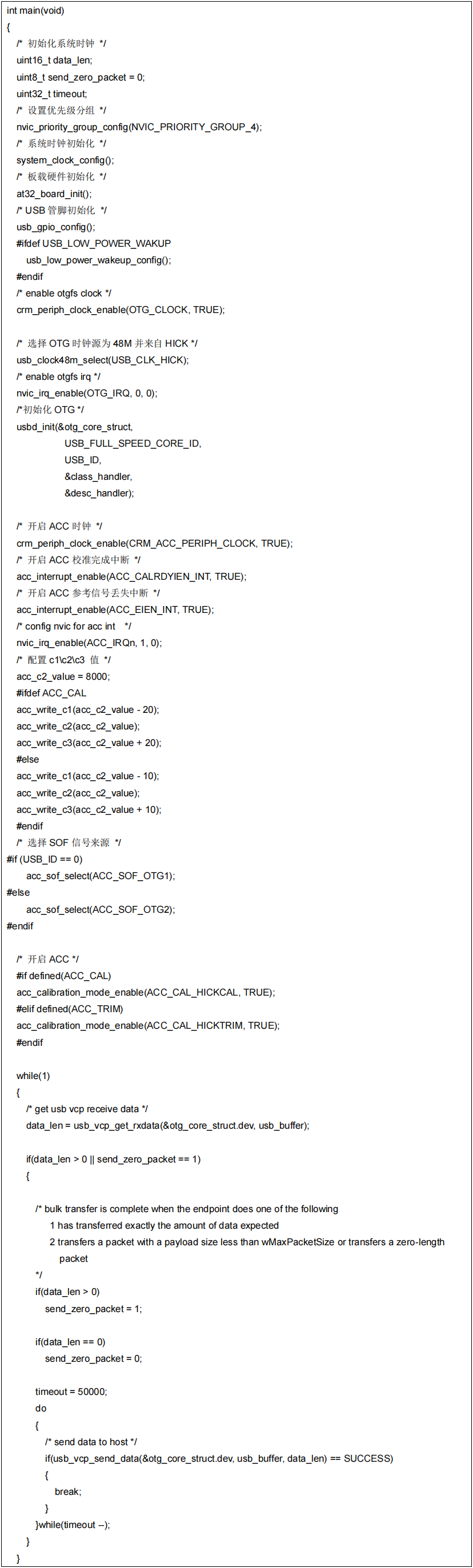

使用HICK作为USB 48MHz时钟代码示例:

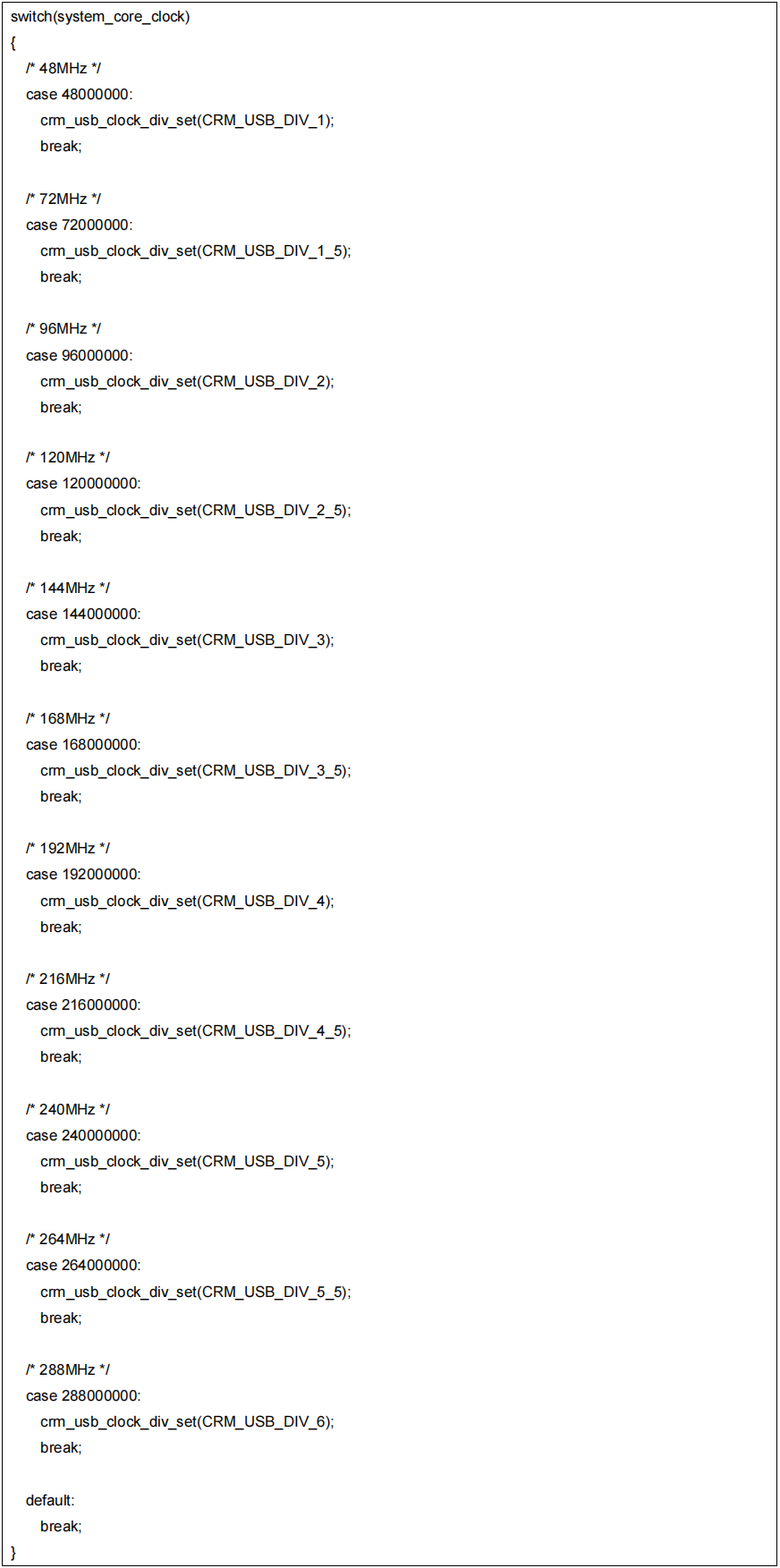

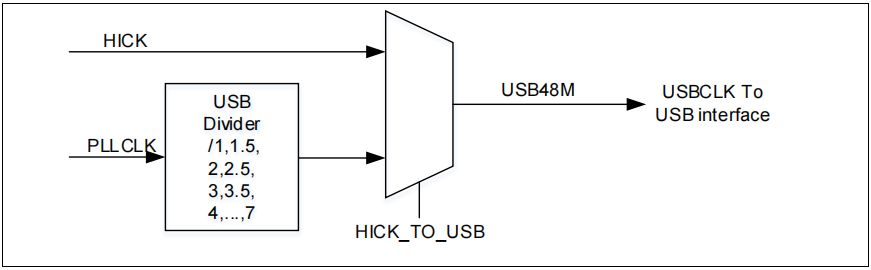

USB时钟选择PLLCK分频

USB 48MHz时钟默认是由PLL通过分频得到,435/437系统时钟最高可达到288Mhz,通过配置USB分频因子,达到为USB提供48MHz时钟。

通过配置已下寄存器进行PLL分频:

USB分频因子支持:1.5分频,不分频,2.5分频,2分频,3.5分频,3分频,4.5分频,4分频,5.5分频,5分频,6.5分频,6分频,7分频。

使用PLL分频作为USB 48MHz时钟代码示例:

OTGFS数据FIFO管理

OTGFS分配专用的1280 Byte SRAM作为数据FIFO,在主机或设备模式下,可通过软件配置寄存器给端点/通道分配FIFO。

注意:分配的FIFO总大小不要超过1280 Byte

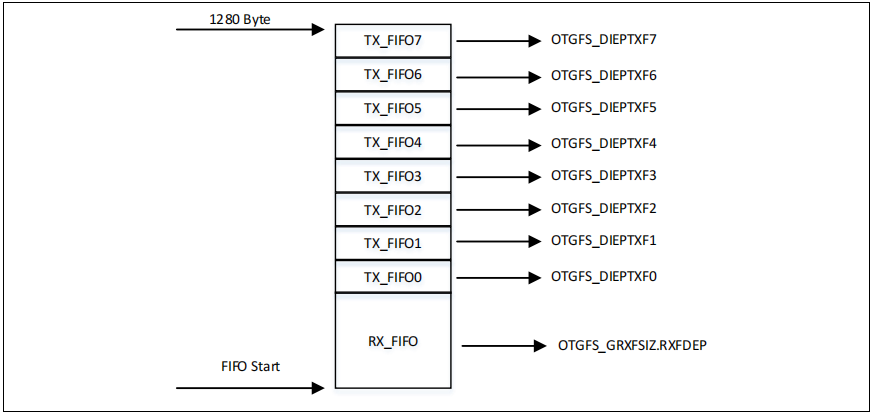

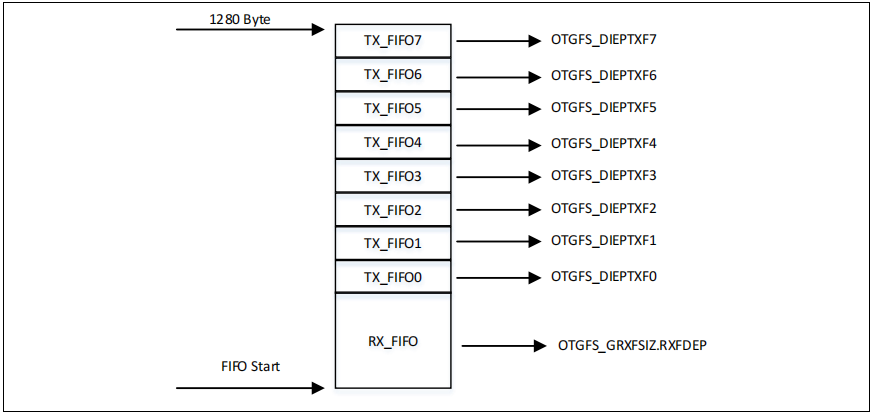

设备模式下的FIFO分配

设备模式下所有端点的接收共享一个接收FIFO,每个端点的发送对应一个专有的发送FIFO。

图3 设备模式FIFO分配

1、RX_FIFO

所有端点的接收共享这一块FIFO,配置寄存器OTGFS_GRXFSIZ.RXFDEP,此寄存器值表示接收FIFO大小,注意单位为word(4Byte)。

2、TX_FIFO0

端点0的发送FIFO,配置寄存器OTGFS_DIEPTXF0,需要配置起始地址和FIFO大小。OTGFS_DIEPTXF0. INEPT0TXSTADDR=OTGFS_GRXFSIZ.RXFDEP

OTGFS_DIEPTXF0. INEPT0TXDEP=端点0发送FIFO大小

3、TX_FIFO1

端点1的发送FIFO,配置寄存器OTGFS_DIEPTXF1,需要配置起始地址和FIFO大小。

OTGFS_DIEPTXF1.INEPTXFSTADDR=OTGFS_GRXFSIZ.RXFDEP+端点0发送FIFO大小OTGFS_DIEPTXF1.INEPTXFDEP=端点1发送FIFO大小

...

注意:对应端点FIFO配置寄存器中FIFO大小值的单位都是word(4Byte)。

注意:发送端点的起始地址一般配置为前面所有端点已占用的FIFO大小,例程如端点2的发送FIFO起始地址为RX_FIFO大小+TX_FIFO0大小+TX_FIFO1大小。

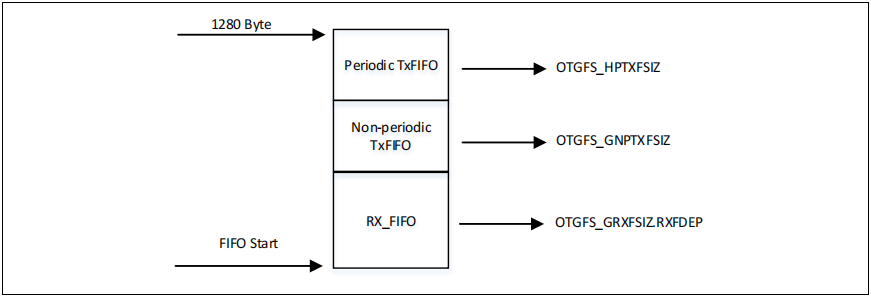

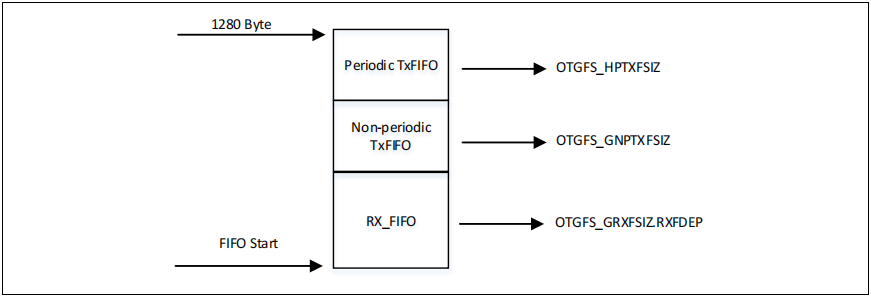

主机模式下的FIFO分配

主机模式下,所有通道共享一个接收FIFO,通道发送FIFO分为非周期性发送FIFO和周期性发送FIFO。

非周期性和周期性通过传输类型来区分,每个主机通道寄存器都有配置传输类型,包含4种传输类型:控制传输(Control),同步传输(ISO),批量传输(Bulk),中断传输(Interrupt)

非周期性:控制传输(Control),批量传输(Bulk)

周期性传输:同步传输(ISO),中断传输(Interrupt)

图4 主机模式下FIFO分配

1、RX_FIFO

所有主机通道的接收共享这一块FIFO,配置寄存器OTGFS_GRXFSIZ.RXFDEP,此寄存器值表示接收FIFO大小,注意单位为word(4Byte)。

2、Non-periodic TxFIFO

非周期性的主机通道发送FIFO,配置寄存器OTGFS_GNPTXFSIZ,需要配置起始地址和FIFO大小。

OTGFS_GNPTXFSIZ. NPTXFSTADDR=OTGFS_GRXFSIZ.RXFDEP

OTGFS_GNPTXFSIZ. NPTXFDEP=非周期性发送FIFO大小

3、Periodic_TxFIFO

周期性的主机通道发送FIFO,配置寄存器OTGFS_HPTXFSIZ,需要配置起始地址和FIFO大小。

OTGFS_HPTXFSIZ.PTXFSTADDR=OTGFS_GRXFSIZ.RXFDEP+OTGFS_GNPTXFSIZ.NPTXFDEP

OTGFS_HPTXFSIZ. PTXFSIZE=周期性发送FIFO大小

注意:对应FIFO配置寄存器中FIFO大小值的单位都是word(4Byte)

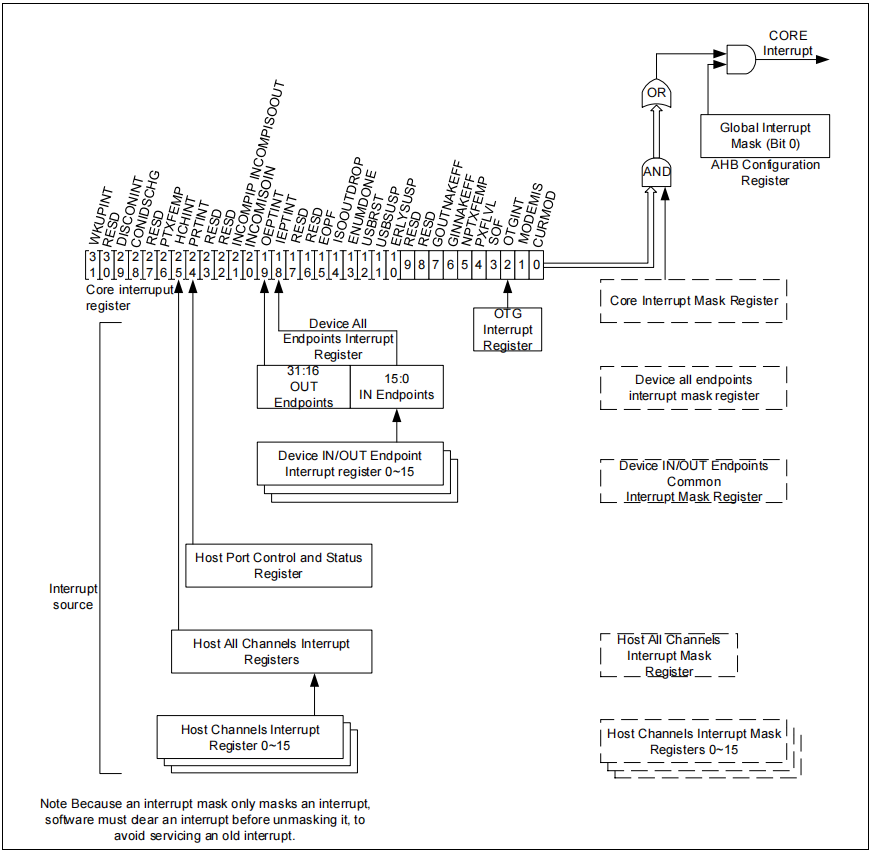

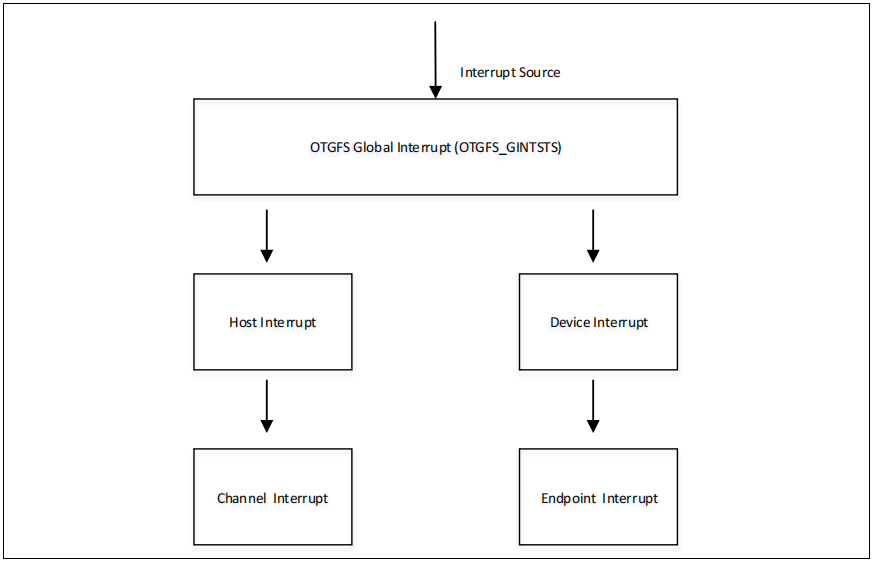

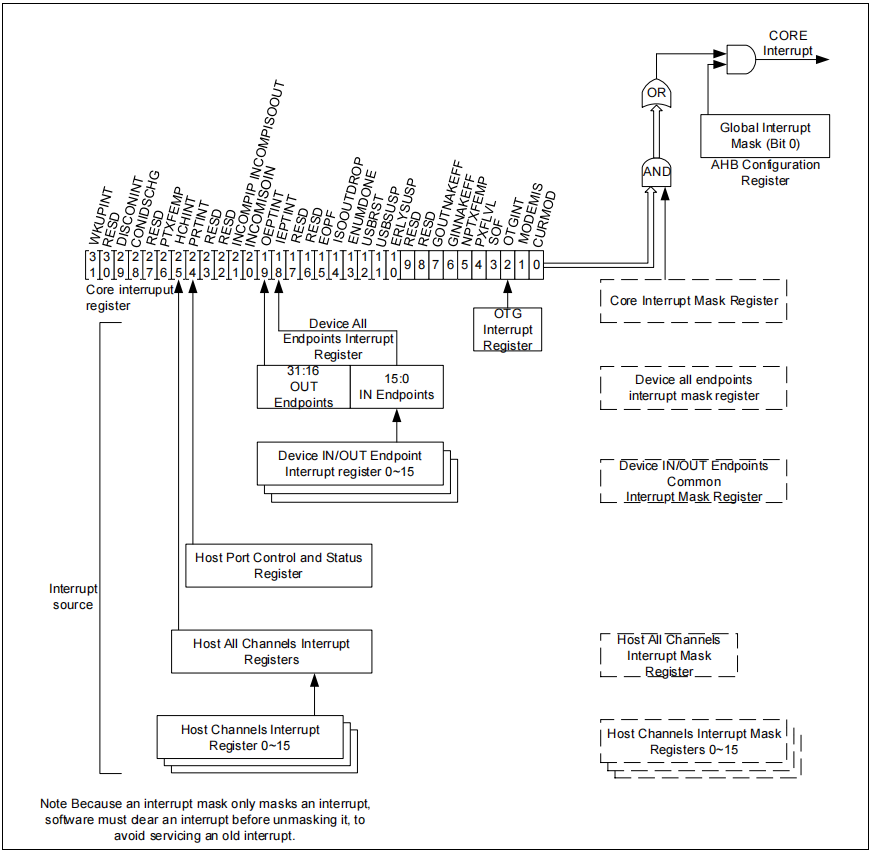

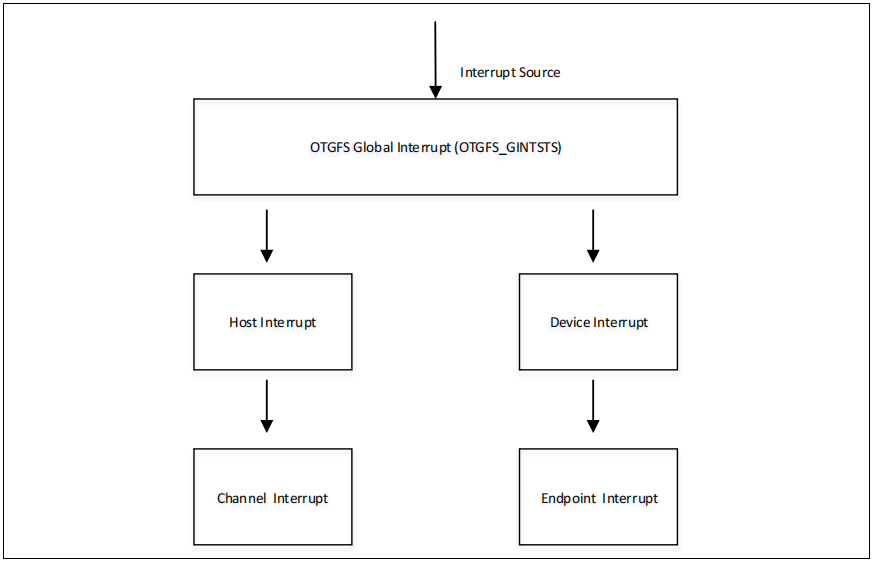

OTGFS中断结构

图5 OTGFS中断结构

全局常用中断OTGFS_GINTSTS,此寄存器中包含了主机和设备的中断标志,部分中断标志只在设备模式或者主机模式下有效。

1、设备和主机模式都有效中断标志

OTGFS_GINTSTS. MODEMIS:模式不匹配(主机和设备都适用)

OTGFS_GINTSTS. SOF:SOF中断(主机和设备都适用)

OTGFS_GINTSTS. RXFLVL:接收FIFO非空(主机和设备都适用)

OTGFS_GINTSTS. CONIDSCHG:ID线状态变化(主机和设备都适用)

OTGFS_GINTSTS. WKUPINT:唤醒信号中断(主机和设备都适用)

2、仅主机模式下有效中断标志

OTGFS_GINTSTS. NPTXFEMP:非周期发送FIFO为空(主机适用)

OTGFS_GINTSTS. PRTINT:主机端口中断(主机适用)

OTGFS_GINTSTS. HCHINT:主机通道中断(主机适用)

OTGFS_GINTSTS. PTXFEMP:周期性发送FIFO为空(主机适用)

OTGFS_GINTSTS. DISCONINT:设备断开(主机适用)

3、仅设备模式下有效中断标志

OTGFS_GINTSTS. USBSUSP:设备挂起(设备适用)

OTGFS_GINTSTS. USBRST:USB复位(设备适用)

OTGFS_GINTSTS. ENUMDONE:枚举速度完成(设备适用)

OTGFS_GINTSTS. ISOOUTDROP:同步OUT包丢失(设备适用)

OTGFS_GINTSTS. IEPTINT:IN端点中断(设备适用)

OTGFS_GINTSTS. OEPTINT:OUT端点中断(设备适用)

OTGFS_GINTSTS. INCOMPISOIN:未完成的同步IN传输(设备适用)

图6 中断处理流程

OTGFS模式

通过配置如下寄存器让OTGFS处于OTG模式:

435/437 OTGFS可以通过检测ID线上的状态来确定当前处于设备模式还是主机模式。当ID状态为高电平时为设备模式,当ID状态为低电平时为主机模式。

寄存器GINTSTS.CURMOD=0,表示当前为设备模式

寄存器GINTSTS.CURMOD=1,表示当前为主机模式

另外可以根据GINTSTS. CONIDSCHG中断来检测当前ID线的状态是否有变化,当检测到ID线有变化时,根据当前的模式位(GINTSTS.CURMOD),应用程序选择初始化主机程序还是设备程序。

图7 OTG模式连接示意图

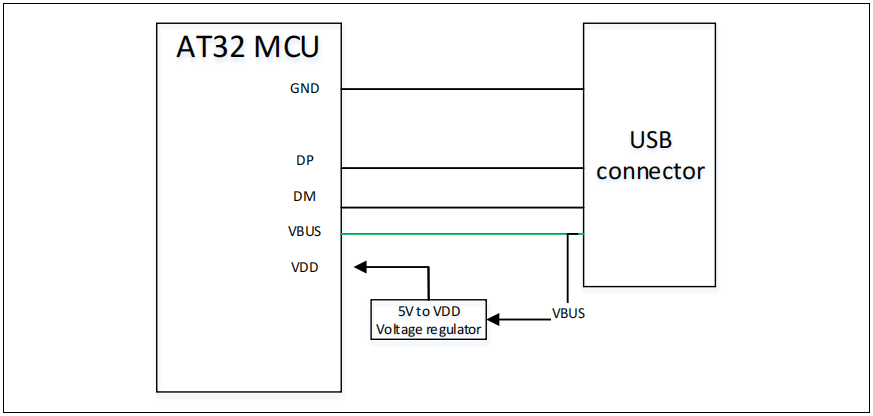

设备模式

435/437 OTGFS作为设备时仅支持全速设备,不支持低速和高速设备。支持8个IN端点(包括端点0),8个OUT端点(包括端点0)。

OTGFS强制作为设备

通过设定如下寄存器将OTGFS强制作为设备:

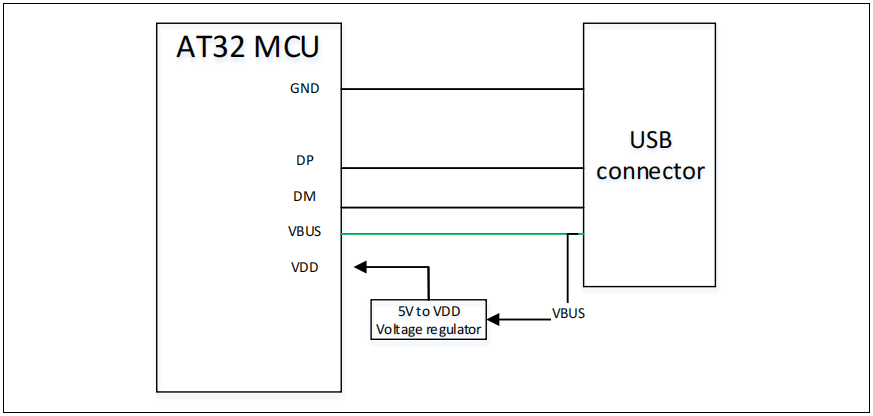

图8 设备模式连接示意图

注意:绿色线表示可选连接,当使能VBUSIG信号时,VBUS引脚可作为普通I/O。

OTGFS设备常用功能

本节介绍OTGFS作为设备模式时的一些功能。

1、软件断开

可以通过配置设备模式下的寄存器,达到让设备断开与主机的连接。原理是通过控制DP的上拉使能来控制连接状态。

配置OTGFS_DCTL.SFTDISCON=1,DP上拉不使能,断开连接。

配置OTGFS_DCTL.SFTDISCON=0,DP上拉使能,开始连接。

2、Remote wakeup唤醒

当设备进入挂起状态之后,可以通过Remote wakeup功能唤醒主机。

唤醒流程:

设置OTGFS_DCTL.RWKUPSIG=1;

延迟1-15ms

设置OTGFS_DCTL.RWKUPSIG=0;

3、忽略VBUS信号

在设备模式下,可以忽略VBUS信号,此模式可以释放VBUS引脚给其它外设使用。通过配置OTGFS_GCCFG.VBUSIG=1来忽略VBUS信号。

OTGFS设备端点配置

本节简单介绍OTGFS端点寄存器的配置。

IN端点配置

IN端点寄存器OTGFS_DIEPCTLx(x为0~7),端点寄存器存放端点的基本信息。

如下是一个IN端点的基本配置选项:

OTGFS_DIEPCTLx.MPS(最大包长度)

OTGFS_DIEPCTLx.EPTYPE(端点类型:控制传输,同步传输,块传输,中断传输)OTGFS_DIEPCTLxTXFNUM(发送FIFO编号,正常跟端点号相同)

OTGFS_DIEPCTLx.USBACEPT(激活端点)

OTGFS_DIEPCTLx.SNAK(设置端点为NAK状态)

OTGFS_DIEPCTLx.CNAK(清除端点NAK状态)

OTGFS_DIEPCTLx.STALL(设置端点为STALL状态)

OTGFS_DIEPCTLx.EPTENA(开始传输数据)

OUT端点配置

OUT端点寄存器OTGFS_DOEPCTLx(x为0~7),端点寄存器存放端点的基本信息。

如下是一个OUT端点的基本配置选项:

OTGFS_DOEPCTLx.MPS(最大包长度)

OTGFS_DOEPCTLx.EPTYPE(端点类型:控制传输,同步传输,块传输,中断传输)OTGFS_DOEPCTLx.USBACEPT(激活端点)

OTGFS_DOEPCTLx.SNAK(设置端点为NAK状态)

OTGFS_DOEPCTLx.CNAK(清除端点NAK状态)

OTGFS_DOEPCTLx.STALL(设置端点为STALL状态)

OTGFS_DOEPCTLx.EPTENA(开始传输数据)

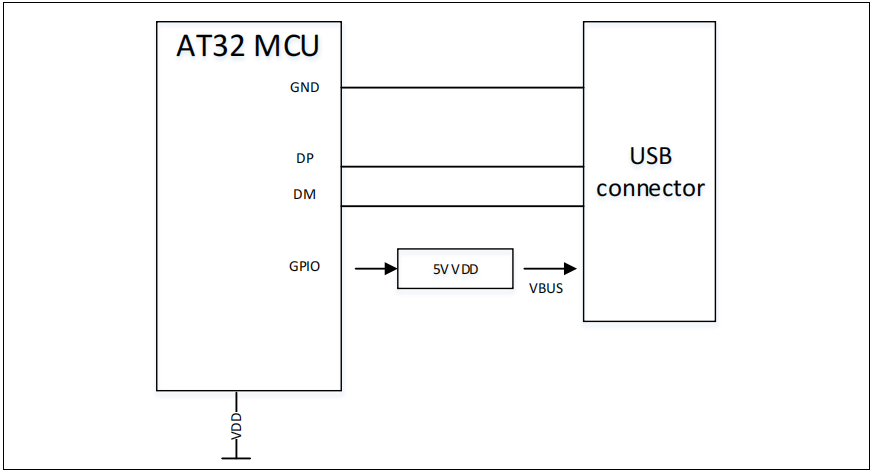

主机模式

435/437 OTGFS作为主机模式时支持全速/低速设备,同时支持16个主机通道。

OTGFS强制作为主机

通过设定如下寄存器将OTGFS强制作为主机,此时DP/DM下拉自动使能:

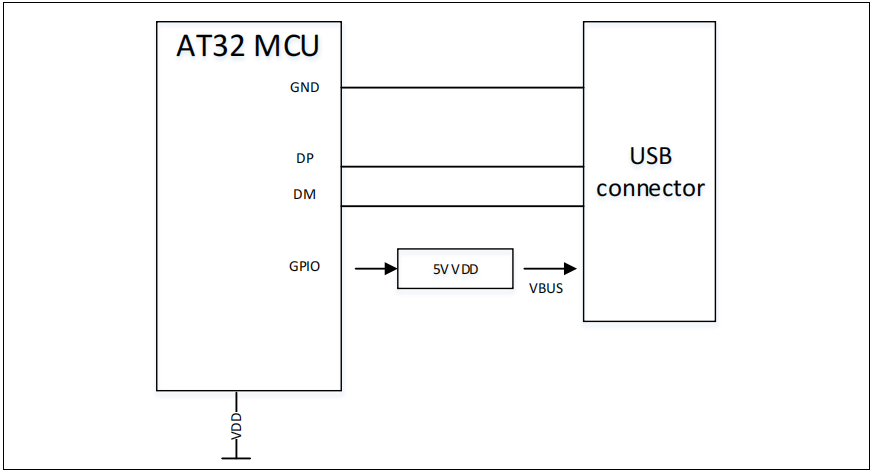

图9 主机模式连接示意图

OTGFS主机常用功能

1、支持全速和低速设备

通过OTGFS_HPRT.PRTSDP判断当前连接的设备是全速设备还是低速设备;OTGFS_HPRT.PRTSDP=1表示全速OTGFS_HPRT.PRTSDP=2表示低速

2、复位

通过设置OTGFS_HPRT.PRTRST来设置端口复位;OTGFS_HPRT.PRTRST=1;延时10msOTGFS_HPRT.PRTRST=0;

3、挂起

通过设置OTGFS_HPRT.PRTSUP=1来设置端口挂起,此时主机停止发送SOF;

OTGFS主机通道配置

主机通道配置寄存器

OTGFS_HCCHARx(x为0~15),通道寄存器存放通道的基本信息。

如下是一个通道的基本配置选项:

OTGFS_HCCHARx.MPS(最大包长度)

OTGFS_HCCHARx.EPTNUM(指示设备端点号)

OTGFS_HCCHARx.EPTDIR(指示设备端点方向 OUT/IN)

OTGFS_HCCHARx.LSPDDEV(低速设备)

OTGFS_HCCHARx.EPTYPE(端点类型:控制传输,同步传输,块传输,中断传输)

OTGFS_HCCHARx.MC(周期性传输在每帧内传输的事务个数)

OTGFS_HCCHARx.DEVADDR(设备地址)

OTGFS_HCCHARx.ODDFRM(周期性传输奇数帧/偶数帧)

OTGFS_HCCHARx.CHDIS(通道禁止)

OTGFS_HCCHARx.CHENA(通道使能)

来源:AT32 MCU 雅特力科技

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。

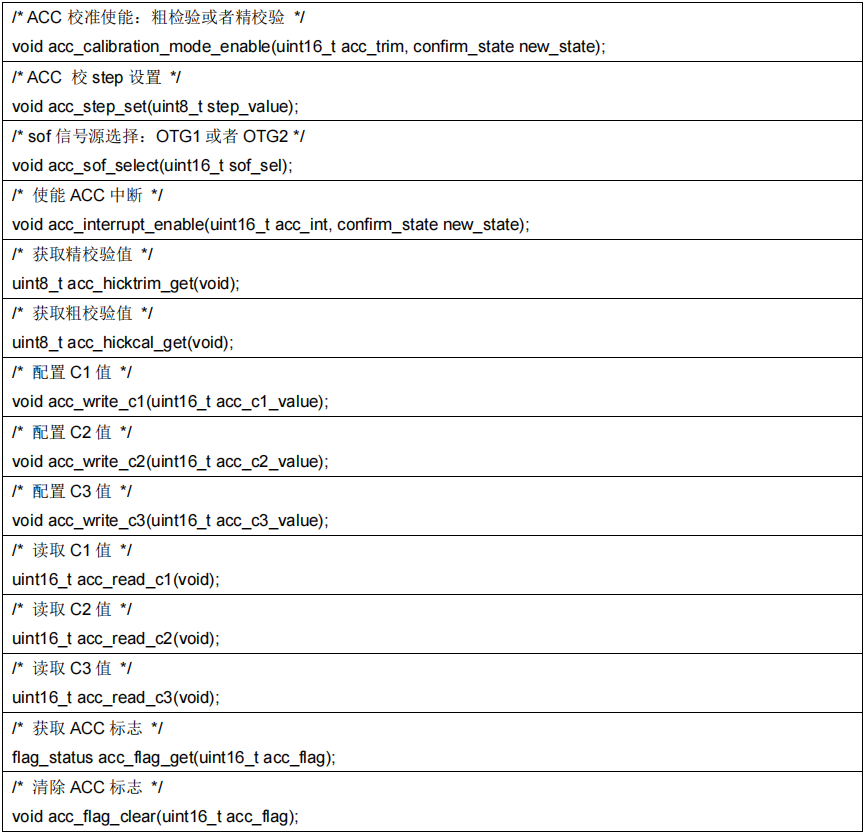

表2. 配置函数列表

表2. 配置函数列表