1. 干簧管是感元件,当磁铁近时,常开触点闭合而接通 感电路 触点负荷仅为 十毫安

2. 通常玩具直流电动机工作电压低,虽然在1.5~3V就可以启动,但起动电流较大(1~2安培),电动机空载时运转电流约为500mA

3. 小功率硅管8050,其集电极最大允许电流ICM可达1.5A,以满足电动机起动电流的要求

4. 双金属复片开关,当 热时闭合

5. 通常光敏电阻器,例如MG45有光照射时的亮阻2~10kΩ光敏电阻器是一种受光照射导电能力急剧增 的电子元件。常用的型号为MG45-1 工作电压在5V时,通过的电流不应超过2mA

6. 水的电阻约50kΩ

7. 一般情况下,8-10毫安以下的工频电流,50毫安以下的直流电流可以年作人体允许的安全电流 一般情况下,人体电阻可按1000-2000欧考虑

8. 低电压(5V)蜂鸣器,其工作电流仅需十 个毫安

9. 继电器线圈(JRC—21F)工作电流大约60mA,比玩具电动机工作电流小,比蜂鸣器、发光二极管工作电流大常用的超小型小功率继电器,型号为 JRC-21F,线圈电源电压为3V或6V 触点工作直流24V、1A继电器线圈电阻从 十欧(3~6v)~ 十千欧(220v) 24V大约1K多 线圈电流不一般不超过100m

10. 发光二极管和普通二极管不同的地方是在导通时的正向压降比较大,一般为1.5~2.V(普通硅二极管约为0.7V)。发光二极管的工作电流一般为10~40mA

11. 万用表二极管档测出来的是压降 二极管的导通电阻在 百欧或 千欧之间

12. 如果数 管共阳极形式,那么它的驱动级应为集电极开路(OC)结构, 如果数 管为共阴极形式,它的驱动级应为射极输出或源极输出电路

13. 稳压管在电路中要反向连接。稳压管的反向击穿电压称为稳定电压

14. 220V的灯泡电阻大约在 千欧 (25瓦灯泡电阻大约2000欧姆,工作电压220伏特)电流 百毫安 小灯泡(3v-5v)电阻 十欧 电流 百毫 安

15. 汽车起动机的启动电流为200~600A

16. 电动机线圈电阻不超过2欧 电流 安到 百安 对于380V电机 1千瓦对应2安

17. 点火线圈初级线圈电阻不超过1欧 次级大约 千欧

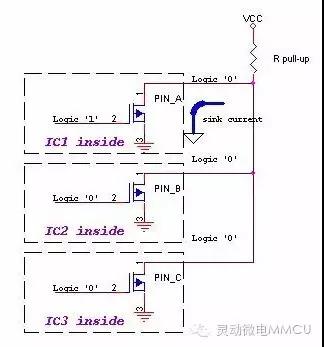

18. IC输出能力 输出高电平时电流

19. 74LS:400uA(驱动不了发光二极管)(输出阻抗(内阻)50~250欧( 据短路电流计算出来),能带负载的能力要求负载输入电阻大于12K( 据输出高电平电流计算400uA) LS的输入电阻为250K( 据输入高电平输入电流计算20uA)))

74HC:4mA(输出阻抗(内阻) 十欧?( 据短路电流计算出来),能带负载的能力要求负载输入电阻大于1.25K( 据输出高电平电流计算 4mA) HC的输入电阻为50M欧( 据输入高电平输入电流计算0.1uA)))

输出低电平时电流 74LS:8mA 74HC:4mA

IC输出时相当于一个电源,电源的内阻越小,相对的驱动能力越强 一般电源的内阻不到1欧 一般电路中间级输入电阻比较大,输出驱动级电阻有大(灯泡,继电器)有小(喇叭,喷嘴)

对于共射接法的三极管来说,输入电阻大约为Rb,输出电阻为Rc

射极输出输入阻抗大Rb+(1+B)Re 输出阻抗小< 20. 驻极体话筒 电阻约500~800欧 输出为3端 为里面集成了场效应管(阻抗匹配) 扬声器的电阻2欧,4欧,8欧,16欧 耳机电阻20~600欧 21. 示波器的输入电阻为1M欧 数字万用表电压档输入电阻1M欧 测量电阻时输出电压0.65V 二极管档输出恒流源1mA 22. 对于扬声器 通道是指不同频率的通道 有源音箱是放大器与扬声器结合在一起 耳机的接头是3芯的 左声道 右声道 和地 23. 感器有产生电信号的(需放大整形)和不产生电信号的 24. 集成运放放大倍数从 万到 十万 所以有虚短 输入阻抗很大 所以输入电流为0 25. 稳压二极管的驱动能力不超过1A 26. 计数器可以实现两种功能,计数 和分频。 异步计数器:逐个翻转速度慢。 同步计数器:同时翻转 速度快。 BCD(十进制)计数器:(0~9)。 二进制计数器(0~15)。 纹波计数器:计数比较大 7级 14级 21级 27. 三极管=晶体管逻辑阵列=OC门 9013(NPN) 9012(PNP) 最大Ic 500mA Ib 是微安级的 最大Vceo 20V 8050(NPN) 8550(PNP) 最大Ic 1.5A Ib 是毫安级的 最大Vceo 25v 2003(晶体管阵列)(NPN) 最大Ic 500mA 最大Vceo 50v(只是用作开关不用作放大) 7407(6个门电路 缓冲器 驱动器 OC门) 最大输出 40mA 最大Vceo 30v(驱动能力小些) 284007 正向电流1A (额定值) 最大正向电流30A 最大反相电压700V 正向压降0.9v 用于整流钳位 保护 4148 正向电流300mA(额定值) 最大正向电流2A 最大反相电压75V 正向压降0.7v 用于小信号场合 发光二极管的压降在1.5~2.5V之间 发光二极管的工作电流一般为10~40mA 29. 7805 最大输入电压35V 能提供1.5A的电流(典型是500mA) 30. 光耦4N32输入额定电流60mA 最大正向电流3A 反向电压6v Vceo 30V Ic 150mA 31. 晶体管分为双极性晶体管和场效应晶体管。场效应晶体管分为结型场效应管JFET 和绝缘栅场效应管。 场效应管输入电阻大,输出电阻小 32. 负反馈:从后级放大器的集电极采样的是电压反馈 从后级放大器的发射极采样的是电流反馈 反馈信号接于晶体管基极的是并联反馈 反馈信号接于晶体管发射极是串联反馈 并联负反馈使输入电阻减小 串联负反馈式输入电阻增大 电压负反馈使输出电阻减小 电流负反馈使输出电阻增大 33. 差动放大器与直接级连放大器相比的优点:抑制温漂。Re越大抑制温漂越好 恒流源相当于一个很大的电阻 34. 集成运放放大倍数太大,为了增加输入范围,必须接成反馈形式。 35. 射级输出 输出效率低 只有20%左右 推挽输出 输出效率高 达到80%左右 双电源供电:输出不加电容 单电源供电:输出加电容。 集成功放LM384,8欧负载上可得5W功率 输出要接500微法电容。 36. 反相比例运算:电压并联负反馈 放大倍数 -R2/R1 输入阻抗 R1 输出阻抗小 同向比例运算:电压串连负反馈 放大倍数 1+R2/R1 输出阻抗大 输出阻抗小 电压跟随器:和射级跟随器一样 输入阻抗大 输出阻抗小。Uo=Ui 37. 用放大器可以构成有源滤波器,电压源,电流源。 38. 运放有负反馈,则运放工作在线性区 有源滤波器,电压源,电流源 运放有正反馈,则运放工作在非线性区 限幅器 电压比较器(无反馈) 过零比较器 迟滞比较器(正反馈) 精密整形电路(反馈回路加二极管)波形发生电路。 39. 电源 整流-滤波-稳压 78系列:输入与输出的电压差不得低于3V 40. 8051一般是指intel公司生产的 89c51是指Atmel公司生产的 都是51系列产品 41. 单片机复位电路:用一个10u电容和10K的电阻来完成 在加一个1N448。复位时间不少于5ms 或者22u电容 1K电阻 高电平复位:电容靠近电源。低电平复位:电容靠近地。 42. 51单片机寻址方式:立即数,直接,寄存器(寄存器比直接快,直接和寄存器都相当于把数据放到一个ram变量中),间接寻址(变量中放的是地址,相当于c++中的指针,在间址寻址中,只能用R0或R1存放等寻找的数据,(R寄存器可用来作为控制循环次数的寄存器)),变址寻址(用于查表MOVC A,@A+DPTR)MOV DPTR,#TABLE(标号前面加# 标号的含义:标号就是一个地址!!比如TABLE就是100H #TABLE就是立即数#100) 43. 51中DPTR是一个16位的寄存器,存放的是地址.。访问外部ram必须用A累加器 44. SP使用前要对它初始化 指明堆栈段从哪里开始 比如MOV SP,#5FH ORG 指明程序段从哪里开始。 45. 移位命令可用于做走马灯试验。 46. LJMP>AJMP>SJMP AJMP是双字节指令 LJMP是三字节指令, 47. CJNE:比较两个数是不相等后转移 (先判断是否相等,之后还可以判断是否大或者小 用JC跳转) DJNZ:减1后不等于零转移,用于控制循环次数 位操作常用的转移指令:JB (位是1的时候转移) JBC(位是1转移 并清0 用于查询方式清除中断标志,用中断方式时不需要手动清0) 48. 在进行位处理时,CY(就是的进位位)称“位累加器” 相当于字节处理中的A。 49. 计数器/定时器要运行有很多限制条件: 有4种工作方式: 用于T的寄存器:TCON 控制定时器和中断 TMOD主要用来控制T的运行方式。 定时器用于中断方式的时候中断中完成的工作:1。中断到了后要实现的动作2。对计数器重新预置(相当于方式2自动完成的工作)3。设置一个软计数循环操作,完成多次定时后输出,这样增加了定时时间。 50用于中断的寄存器: IE:中断总开关 中断程序时间不能大于中断间隔时间 未完待续...... 本文转自:张飞实战电子,转载此文目的在于传递更多信息,版权归原作者所有。

1。C/T开关

2。Tr开关

3。Gate开关(Gate=1的时候,还要受Int1的控制)。

用SETB TR0 启动T。

0。13位

1。16位

2。有预置的(高8位做预置用,低8位做计数用,所以范围小),一般用于波特率发生器

3。定时器 0分为两个独立的定时/计数器,一般T1工作于方式2时,T0才工作在方式3。

IP:中断优先级 ECON SCON