低功耗、高速度、高集成度的LSI电路是成众多电子产品的首要考虑,这也就导致装置比以往任何时候更容易受到电磁干扰的威胁。此外,大功率家电及办公自动化设备的增多,以及移动通信、无线网络的广泛应用等,又大大增加了电磁骚扰源。这些变化迫使人们把电磁兼容作为重要的技术问题加以关注。

电磁兼容

采用一定的技术手段,使同一电磁环境中的各种电子、电气设备都能正常工作,并且不干扰其他设备的正常工作,这就是电磁兼容(ElectromagneticCompatibility,缩写为EMC)。

在国家标准GB/T4365-1995中对电磁兼容严格的定义是:设备或系统在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁骚扰的能力。

电磁兼容性包括两方面:电磁干扰(electromagnetic interference ;EMI)、电磁耐受(electromagnetic susceptibility; EMS)。

EMI指的是电气产品本身通电后,因电磁感应效应所产生的电磁波对周围电子设备所造成的干扰影响;

EMS则是指电气产品本身对外来电磁波的干扰防御能力。

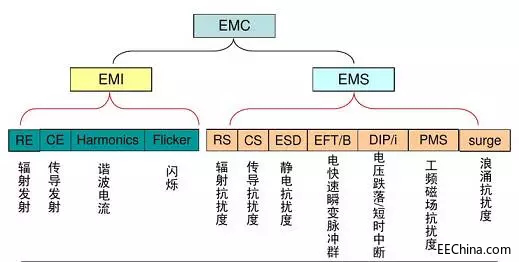

其中EMI包括:CE(传导干扰),RE(辐射干扰),PT(干扰功率测试)等等。

EMS包括:ESD(静电放电),RS(辐射耐受),EFT/B(快速脉冲耐受),surge(雷击),CS(传导耐受)等。

显然,EMC 设计的目的就是使所设计的电子设备或系统在预期的电磁环境中能够实现电磁兼容。换而言之,就是说设计的电子设备或系统必须能够满足EMC 标准规定的两方面的能力。

常见EMC测试项目

电磁干扰(EMI)的原理

EMI的产生原因

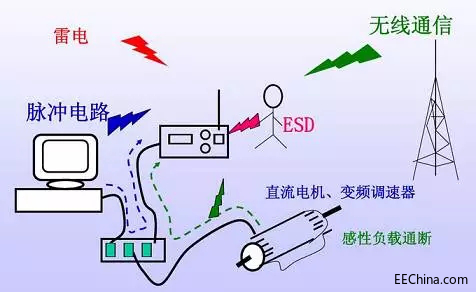

各种形式的电磁干扰是影响电子设备兼容性的主要原因。因此,了解电磁干扰的产生原因是抑制电磁干扰,提高电子产品电磁兼容性的重要前提。电磁干扰的产生可以分为:

1.内部干扰内部电子元件之间的相互干扰

(1)工作电源通过线路的分布电源和绝缘电阻产生漏电造成的干扰。

(2)信号通过地线、电源和传输导线的阻抗互相耦合,或导线之间的互感造成的影响。

(3)设备或系统内部某些元件发热,影响元件本身及其他元件的稳定性造成的干扰。

(4)大功率和高点压部件产生的磁场、电场通过耦合影响其他部件造成的干扰。

2.外部干扰——电子设备或系统以外的因素对线路、设备或系统的影响。

(1)外部高电压、电源通过绝缘漏电而干扰电子线路、设备或系统。

(2)外部大功率的设备在空间产生很强的磁场,通过互感耦合干扰电子线路、设备或系统。

(3)空间电磁对电子线路或系统产生的干扰。

(4)工作环境温度不稳定,引起电子线路、设备或系统内部元器件参数改变造成的干扰。

电磁干扰的传播途径

1.当干扰源频率较高,且干扰信号波长比被干扰对象结构尺寸小,则干扰信号可认为是辐射场,以平面电磁波形式向外辐射电磁场能量,并进入被干扰对象的通路。

2.干扰信号以漏电和耦合的形式,通过绝缘电介质,经公共阻抗的耦合进入被干扰系统。

3.干扰信号可通过直接传导方式进入系统。

改善电磁兼容性的措施

要改善电子产品的电磁兼容性,接地、屏蔽和滤波是抑制EMI的基本方法。

1.接地

接地就是一个系统内电气与电子元件至地参考点之间的电传导路径。接地除了提供设备的安全保护地以外,还提供设备运行所必需的信号参考地。理想的接地平面是一个零电位、零阻抗的物理体,它可作为电路中所有信号点评的参考点,并且任何干扰信号通过它,都不会产生电压降。但是,理想的接地平面是不存在的,这就需要我们考虑和分析地电位分布,进行接地设计与研究,找出合适的接地电位。

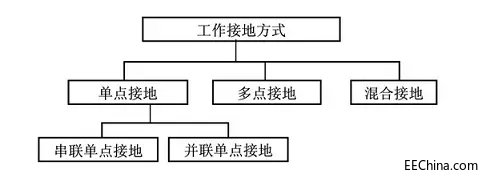

接地的方式可分为:浮地、单点接地、多点接地、混合接地。对于电路系统来说可选择:电路接地、电源接地和信号接地等方法。

2.屏蔽

屏蔽就是用导电或电磁体的封闭面将其内外两侧空间进行电磁性隔离。主要抑制过空间的辐射干扰。分为电磁屏蔽、电场屏蔽和磁场屏蔽。

屏蔽的设计既可以针对干扰源,也可以针对被干扰体。对于干扰源,设计屏蔽部分可以使其减小对周边其他设备的影响

对于被干扰体,则可减小外界干扰电磁波对本设备的影响。

主动屏蔽:把干扰源置于屏蔽体之内,防止电磁能量和干扰信号泄漏到外部空间。

被动屏蔽:把敏感设备置于屏蔽体内,使其不受外部干扰的影响。

3.滤波

滤波的含义是指从混有噪声或干扰的原信号中,提取到有用信号的一门技术,滤波器是实现滤波的元器件。

事实上,器件在工作时,也会产生各种各样的噪声。开关电源就是一种很强的干扰源,它产生的EMI信号即占有很宽的频率范围,又具有较大的振幅。这些噪声随着信号的传播,对下一级的元器件产生了干扰,这样的干扰一级级的累积,最终可能导致整个电路的不正常工作。假设在产生噪声大,对下级器件干扰明显的器件输出信号之后做一次滤波,将噪声信号滤掉,它对下级产生的干扰便会降低,系统便能稳定的工作。

EMC滤波器的分类

① 反射式滤波器

由电感器和电容器组成,利用反射或旁路,使干扰信号不能通过。

② 损耗滤波器

选用具有高损耗系数或高损耗角正切的材料,把高频电磁能量通过涡流转换成热能。

例如:铁氧体管,铁氧体磁环,磁环扼流圈等。

③ 有源滤波器

使用晶体管等有源器件,以较小的体积和重量可以提供较大值的等效L和C。

有源电感滤波器:用晶体管模拟电感线圈的频率特性(f越高,阻抗越大)。

有源电容滤波器:用晶体管模拟电容器的频率特性(f越高,阻抗越小)。

对消滤波器(陷波器):能产生与干扰信号幅度相同,相位相反(差180°)的电流,把干扰信号抵消。

电磁兼容认证

产品的EMC认证是依据产品的电磁兼容标准和相应的技术要求,经过认证机构测试确认,并通过颁发认证证书和认证标志来证明某一产品符合相应标准和相应技术的要求。

在我国EMC认证已纳入3C认证范围(中国强制认证,英文名称为“China Compulsory Certification”,英文缩写为“CCC”,也可简称为“3C”),国家对有强制性电磁兼容国家标准或强制性电磁兼容行业标准以及标准中有电磁兼容强制条款的产品实行安全认证制度,对这些实施电磁兼容安全认证的产品在进入流通领域实施强制性监督管理(没有进行电磁兼容安全认证就不能进入流通领域)。

对有推荐性电磁兼容国家标准或推荐性电磁兼容行业标准的产品实行合格认证制度,企业可以根据自愿的原则向认证机构申请认证。

EMC认证机构:中国电磁兼容认证委员会 (CEMC)

认证测试必须在国家技术监督局认可的EMC测试机构进行。

电磁兼容技术包括了对电磁学、电子学、材料学、等多方面知识的综合。随着电子产品的日益普及以及对电磁危害的逐渐认识,减小电磁干扰已经成为了目前电子科学界的重要课题,如今的电路都已集成化、模块化,所以现在的电路分析和设计也可以说成是系统的分析和设计,相信对这门技术的深入研究会对今后的电子产品性能的提高有显著影响。

来源: eechina.com