摩尔定律(Moore's Law)是由英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)于1965年提出的一项观察和预测,它描述了集成电路中晶体管数量的增长速度。

然而,随着摩尔定律的持续发展,面临了一些挑战。集成电路的物理限制、功耗问题以及制造成本的增加等因素已经导致了一些讨论摩尔定律是否会继续成立的问题。摩尔定律虽然不再是绝对准确的规则,但仍然在一定程度上影响着半导体和计算领域的发展。

摩尔定律(Moore's Law)是由英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)于1965年提出的一项观察和预测,它描述了集成电路中晶体管数量的增长速度。

然而,随着摩尔定律的持续发展,面临了一些挑战。集成电路的物理限制、功耗问题以及制造成本的增加等因素已经导致了一些讨论摩尔定律是否会继续成立的问题。摩尔定律虽然不再是绝对准确的规则,但仍然在一定程度上影响着半导体和计算领域的发展。

2017年9月19日,“英特尔精尖制造日”活动在北京举行。英特尔公司执行副总裁兼制造、运营与销售集团总裁Stacy Smith全球首次展示“Cannon Lake”10纳米晶圆,它拥有世界上最密集的晶体管和最小的金属间距,从而实现了业内最高的晶体管密度,领先其他“10纳米”整整一代,以时间来算,则领先3年时间。

晶圆是制造半导体芯片的基本材料,由于其形状为圆形,故称为晶圆。

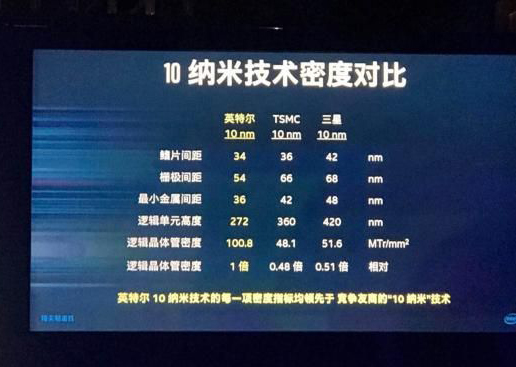

对于竞争对手三星、台积电等公司,英特尔直言不讳地称自身技术上具有领先性。英特尔将10纳米技术密度进行了对比,英特尔称在栅极间距、最小金属间距间技术指标上都处于领先地位。

近几年,“摩尔定律失效”是近两年来业界讨论的热门话题。随着硬件制程工艺在物理层面越来越接近极限,摩尔定律所诠释的“当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍”的规律逐渐被打破,使得人们对摩尔定律在未来所产生的指导意义产生强烈怀疑。

9月19日面对媒体的发布会上,英特尔称所掌握的超微缩技术将为摩尔定律正名,可以继续提升晶体管密度和降低单位成本,从而继续把摩尔定律向前推进。

来源: 21ic.com

如题,先从大厂说起。目前芯片厂商有三类:IDM、Fabless、Foundry。

IDM(集成器件制造商)指 Intel、IBM、三星这种拥有自己的晶圆厂,集芯片设计、制造、封装、测试、投向消费者市场五个环节的厂商,一般还拥有下游整机生产。

Fabless(无厂半导体公司)则是指有能力设计芯片架构,但本身无厂,需要找代工厂代为生产的厂商。

Foundry(代工厂)则指台积电和 GlobalFoundries,拥有工艺技术代工生产别家设计的芯片的厂商。我们常见到三星有自己研发的猎户座芯片,同时也会代工苹果 A 系列和高通骁龙的芯片系列,而台积电无自家芯片,主要接单替苹果和华为代工生产。

制程

在描述手机芯片性能的时候,消费者常听到的就是 22nm、14nm、10nm 这些数值,这是什么?

这是芯片市场上,一款芯片制程工艺的具体数值是手机性能关键的指标。制程工艺的每一次提升,带来的都是性能的增强和功耗的降低,而每一款旗舰手机的发布,常常与芯片性能的突破离不开关系。

据悉,骁龙 835 用上了更先进的 10nm 制程, 在集成了超过 30 亿个晶体管的情况下,体积比骁龙 820 还要小了 35%,整体功耗降低了 40%,性能却大涨 27%。

深入来说,这几十纳米怎么计算出来的?我们从芯片的组成单位晶体管说起。

得益于摩尔定律的预测,走到今天,比拇指还小的芯片里集成了上亿个晶体管。苹果 A10 Fusion 芯片上,用的是台积电 16nm 的制造工艺,集成了大约 33 亿个晶体管。

而一个晶体管结构大致如下:

图中的晶体管结构中,电流从 Source(源极)流入 Drain(漏级),Gate(栅极)相当于闸门,主要负责控制两端源极和漏级的通断。电流会损耗,而栅极的宽度则决定了电流通过时的损耗,表现出来就是手机常见的发热和功耗,宽度越窄,功耗越低。而栅极的最小宽度(栅长),就是 XX nm工艺中的数值。

对于芯片制造商而言,主要就要不断升级技术,力求栅极宽度越窄越好。不过当宽度逼近 20nm 时,栅极对电流控制能力急剧下降,会出现“电流泄露”问题。为了在 CPU 上集成更多的晶体管,二氧化硅绝缘层会变得更薄,容易导致电流泄漏。

一方面,电流泄露将直接增加芯片的功耗,为晶体管带来额外的发热量;另一方面,电流泄露导致电路错误,信号模糊。为了解决信号模糊问题,芯片又不得不提高核心电压,功耗增加,陷入死循环。

因而,漏电率如果不能降低,CPU 整体性能和功耗控制将十分不理想。这段时间台积电产能跟不上很大原因就是用上更高制程时遭遇了漏电问题。

还有一个难题,同样是目前 10nm 工艺芯片在量产遇到的。

当晶体管的尺寸缩小到一定程度(业内认为小于 10nm)时会产生量子效应,这时晶体管的特性将很难控制,芯片的生产难度就会成倍增长。骁龙 835 出货时间推迟,X30 遥遥无期主要原因可能是要攻克良品率的难关。

另外,骁龙 835 用上了 10nm 的制程工艺,设计制造成本相比 14nm 工艺增加接近 5 成。大厂需要持续而巨大的资金投入到 10nm 芯片量产的必经之路。

就目前阶段,三星已经尝试向当前的工艺路线图中添加 8nm 和 6nm 工艺技术,台积电方面则继续提供 16nm FinFET 技术的芯片,开始着力 10nm 工艺的同时,预计今年能够样产 7nm 工艺制程的芯片。

FinFET

除了制程,还有工艺技术。

在这一代骁龙 835 上,高通选择了和三星合作,使用三星最新的 10nm FinFET 工艺制造。同样,三星自家的下一代旗舰猎户座 8895 用的也是用此工艺。

FinFET 是什么?

业界主流芯片还停留在 20/22nm 工艺节点上的时候,Intel 就率先引入了 3D FinFET 这种技术。后来三星和台积电在 14/16nm 节点上也大范围用上了类似的 FinFET 技术。下面我们统称为 FinFET。

FinFET(Fin Field-Effect Transistor)称为鳍式场效应晶体管,是一种新的晶体管,称为 CMOS。具体一点就是把芯片内部平面的结构变成了3D,把栅极形状改制,增大接触面积,减少栅极宽度的同时降低漏电率,而晶体管空间利用率大大增加。

因为优势明显,目前已经被大规模应用到手机芯片上。

经历了 14/16nm 工艺节点后,FinFET 也历经升级,但这种升级是存在瓶颈的。目前,大厂们正研究新的 FD-SOI(全耗尽绝缘体硅)工艺、硅光子技术、3D 堆叠技术等,斥资寻求技术突破,为日后 7nm、甚至 5nm 工艺领先布局。

LPE/LPP/LPC/LPU 又是什么?

在工艺分类上,芯片主要分两大类:

● HP(High Performance):主打高性能应用范畴;

● LP(Low Power):主打低功耗应用范畴。

满足不同客户需求,HP 内部再细分 HPL、HPC、HPC+、HP 和 HPM 五种。

HP 和 LP 之间最重要区别就在性能和漏电率上,HP 在主打性能,漏电率能够控制在很低水平,芯片成本高;LP 则更适合中低端处理器使用,因为成本低。

所以,芯片除了在制程上寻求突破,工艺上也会逐步升级。

2014 年底,三星宣布了世界首个 14nm FinFET 3D 晶体管进入量产,标志着半导体晶体管进入 3D 时代。发展到今天,三星拥有了四代 14nm 工艺,第一代是苹果 A9 上面的 FinFET LPE(Low Power Early),第二代则是用在猎户座 8890、骁龙 820 和骁龙 625 上面的 FinFET LPP(Low Power Plus)。第三代是 FinFET LPC,第四代则是目前的 FinFET LPU。至于 10nm 工艺,三星则更新到了第三代(LPE/LPP/LPC)。

目前为止,三星已经将 70000 多颗第一代 LPE(低功耗早期)硅晶片交付给客户。三星自家的猎户座 8895,以及高通的骁龙 835,都采用这种工艺制造,而 10nm 第二代 LPP 版和第三代 LPU 版将分别在年底和明年进入批量生产。

不知不觉,手机芯片市场上已经进入了 10nm、7nm 处理器的白热化竞争阶段,而 14/16nm 制程的争夺也不过是一两年前的事。

之前有人怀疑摩尔定律在今天是否还适用,就芯片的进化速度和技术储备来看,不是技术能力达不到,而是厂商们的竞争程度未必能逼迫它们全速前进。

来源:爱范儿

摩尔定律,在半导体业中人人皆知,然而它与中国半导体业的发展有什么关系?恐怕一时难以马上回答。

如何看待摩尔定律,站在不同立场可能有不同的解释。现阶段定律即将止步的讨论,可能会更加引发业界的深刻兴趣。

定律的光环

定律尤如一盏明灯,让企业义无反顾的去信奉它,追随它。因为定律孕育着一个十分强大的经济规律。在每两年内如果您的企业跟不上定律的步伐,不能前进至下一个工艺制程节点,就可能被淘汰出局。所以众多企业为了生存,争取前位,而不惜投资跟踪。

因此定律实际上是一种自我激励的机制。在较长一段时间内,众多fabless都愿意迅速采用下一代先进的工艺制程,推动产业的进步,这就是定律的魔法所在。比较典型的如在苹果手机中,己从A4进步到A10处理器,一颗16纳米制程采用FanOut封装的芯片,在台积电加工。

显然,市场经济是理性的,在工艺制程进入到28纳米之后,由于工艺研发与设计费用的高耸,逼迫许多顶级的IDM厂要作出决断,包括如NXP,Freescale,STMicron等公开声言,它们执行轻晶园厂策略(fab-lite),意即不再跟踪定律,而开始拥护代工,导致全球代工如日中天的火红增长。

摩尔定律是什么?有人理解它是”大者恒大”,这样的观点具有普遍性。因为近50年来的实践,产业内的分化日趋激烈,然而”大者恒大”,是不变的规律。如典型的存储器业中,从几十家到现在只剩下DRAM的三家及NAND的四个组合,未来中国欲加入,业界正密切关注最后的结局。又如半导体设备业中,之前全球也是几十个厂家经过残酷的竞争,如今每个设备类别中几乎只剩下约二家。

中国半导体业跟不上定律的节奏

众所周知,中国半导体业的发展与全球先进地区之间存在很大差距,是不同步的,据估计在芯片制造业中至少落后两个先进工艺节点制程。

近期见到台积电公布它的10纳米及7纳米先进制程进度,如10纳米于2016年上半年试产,开始量产时间为2016年第四季,地点为中科12英寸晶园厂Fab15的第5至第7期,主要客户及产品为苹果A11应用处理器,高通ARM架构的HPC处理器,联发科HelioX30手机处理器及海思Kirin手机处理器与网络处理器。而它的7纳米,试产时间2017年上半年,量产时间为2018年第1季。地点与10纳米相同,主要客户为Xilinx的FPGA及Nvidia的新一代Volta绘图芯片(GPU)。

分析其中的原因是复杂及多方面的,肯定有西方主导的瓦圣纳条约的技术封锁问题,也有产业发展处于不同的阶段。如中国半导体业的发展尚处在需要国家资金来推动的初级阶段,而不是完全市场化。因此当对手们在你追我赶的发展阶段,而中国半导体业尚需要国家资金的哺育。所以正如有些专家所言,中国的芯片制造企业是死不了,也不太可能赶上快的节奏。

定律转型中国尚有机会

未来摩尔定律实际上向三个方面发展,第一,继续走尺寸缩小道路,可以预计大约还有2-3个节点,至5纳米左右,定律接近物理极限。目前推动尺寸缩小主要是高性能计算市场的需求。第二,是异质集成,如人工智能与物联网等需求,它的目的是把不同工艺的产品,包括RF,MEMS,Sensor,image等,采用SiP,2.5D,3D封装工艺集成一体。因此主要是采用成熟制程工艺。由于定律刚开始转型,如英特尔,台积电,包括中芯国际等己经开始跨入后道封装工艺,似乎表明中国尚存机会。而第三方面主要寻求新的材料及晶体管架构,目前尚偏重于基础研究阶段。

让摩尔定律光环照亮中国半导体业

尽管集成电路尺寸缩小的道路己难深入下去,众多芯片制造厂商面临转型,实际上其中有一条道路要跨界进入封装业。可以相信前方的路也十分不易,成本下降是个永恒课题。看似此次中国半导体制造业几乎能站在同一起跑线上,然而由于众多原因的束缚,也未必一定能有胜算。

目前的态势依然十分严峻,首先悲观论调是无益的,但是盲目乐观也不可取。要相信中国半导体业一定能进步,然而依据产业发展的规律,科学的态度,试图在短时间内会发生突变的可能性也不会存在,一定是循序前进,对于中国半导体业的发展能够少些大的波动己是相当的不错。

摩尔定律是一个普适的发展规则,它在计算机业中有人认为每两年计算能力会增加一倍等。尽管中国半导体业的发展在现阶段尚无法跟上定律的节奏,暂时出现差距是完全正常。要改变此等被动的局面,可能非一日之功,其中关键在于迅速实现“两化”,向市场化加非国有化过渡,两者相辅相成,缺一不可。在现阶段要尽可能的减少非市场化因素的干扰,尤其是要让骨干企业的信心迅速提升。

显然,定律的光环对于中国半导体业发展仅仅是外部因素,要跟上定律的节奏,需要扎实的努力,相信“一份耕耘,会有一份收获”。

摩尔定律的光环一定会照亮中国半导体业的迅速进步。

文章来源:与非网