GPIO的功能,简单说就是可以根据自己的需要去配置为输入或输出。但是在配置GPIO管脚的时候,常会见到两种模式:开漏(open-drain,漏极开路)和推挽(push-pull)。

Push-Pull推挽输出

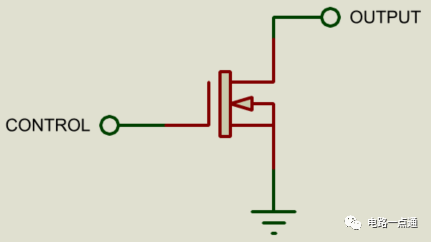

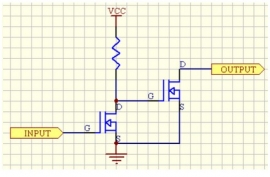

输出的器件是指输出脚内部集成有一对互补的MOSFET,当Q1导通、Q2截止时输出高电平;而当Q1截止导通、Q2导通时输出低电平

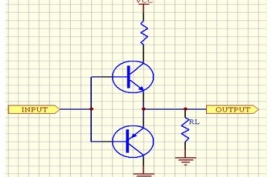

Push-pull输出,实际上内部是用了两个晶体管(transistor),此处分别称为top transistor和bottom transistor。通过开关对应的晶体管,输出对应的电平。top transistor打开(bottom transistor关闭),输出为高电平;bottom transistor打开(top transistor关闭),输出低电平。Push-pull即能够漏电流(sink current),又可以集电流(source current)。其也许有,也许没有另外一个状态:高阻抗(high impedance)状态。除非Push-pull需要支持额外的高阻抗状态,否则不需要额外的上拉电阻。

Open-Drain开漏输出

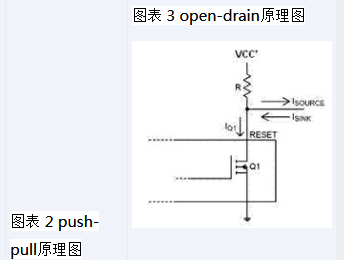

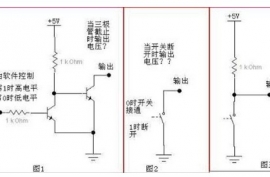

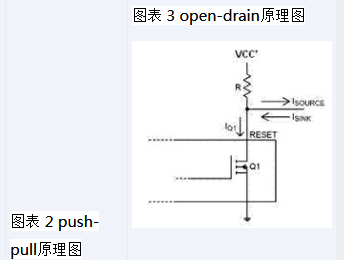

开漏电路就是指以MOSFET的漏极为输出的电路。指内部输出和地之间有个N沟道的MOSFET(Q1),这些器件可以用于电平转换的应用。输出电压由Vcc'决定。Vcc'可以大于输入高电平电压VCC(up-translate)也可以低于输入高电平电压VCC(down-translate)。

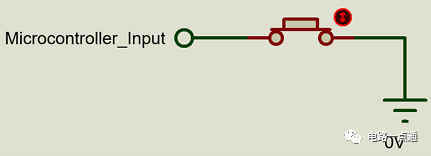

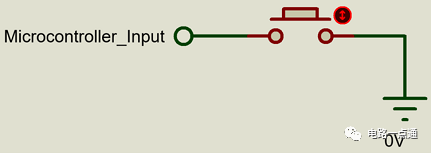

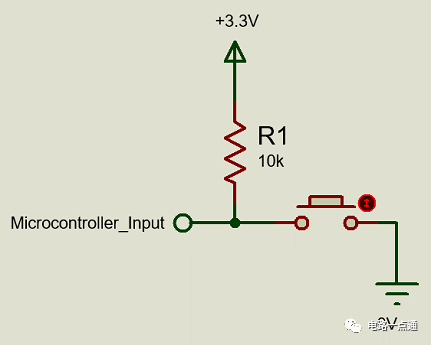

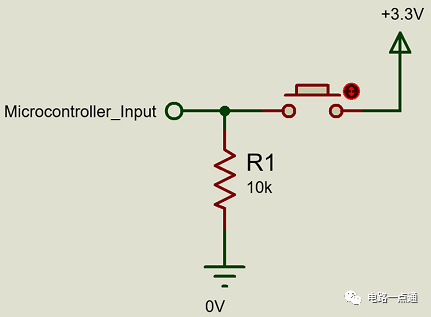

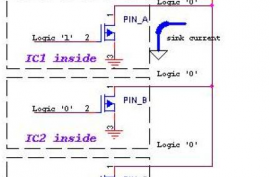

Open-drain输出,则是比push-pull少了个top transistor,只有那个bottom transistor。(就像push-pull中的那样)当bottom transistor关闭,则输出为高电平。此处没法输出高电平,想要输出高电平,必须外部再接一个上拉电阻(pull-up resistor)。Open-drain只能够漏电流(sink current),如果想要集电流(source current),则需要加一个上拉电阻。

老外的理解

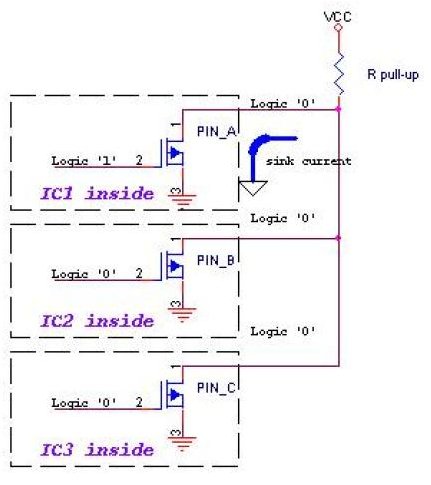

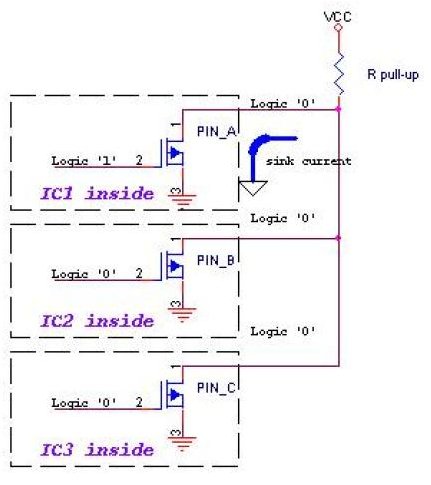

常见的GPIO的模式可以配置为open-drain或push-pull,具体实现上,常为通过配置对应的寄存器的某些位来配置为open-drain或是push-pull。当我们通过CPU去设置那些GPIO的配置寄存器的某位(bit)的时候,其GPIO硬件IC内部的实现是,会去打开或关闭对应的top transistor。相应地,如果设置为了open-d模式的话,是需要上拉电阻才能实现,也能够输出高电平的。因此,如果硬件内部(internal)本身包含了对应的上拉电阻的话,此时会去关闭或打开对应的上拉电阻。如果GPIO硬件IC内部没有对应的上拉电阻的话,那么你的硬件电路中,必须自己提供对应的外部(external)的上拉电阻。而push-pull输出的优势是速度快,因为线路(line)是以两种方式驱动的。而带了上拉电阻的线路,即使以最快的速度去提升电压,最快也要一个常量的R×C的时间。其中R是电阻,C是寄生电容(parasitic capacitance),包括了pin脚的电容和板子的电容。但是,push-pull相对的缺点是往往需要消耗更多的电流,即功耗相对大。而open-drain所消耗的电流相对较小,由电阻R所限制,而R不能太小,因为当输出为低电平的时候,需要sink更低的transistor,这意味着更高的功耗。(此段原文:because the lower transistor has to sink that current when the output is low; that means higher power consumption.)而open-drain的好处之一是,允许你cshort(?)多个open-drain的电路,公用一个上拉电阻,此种做法称为wired-OR连接,此时可以通过拉低任何一个IO的pin脚使得输出为低电平。为了输出高电平,则所有的都输出高电平。此种逻辑,就是“线与”的功能,可以不需要额外的门(gate)电路来实现此部分逻辑。

图表 4 open-drain“线与”功能

优点

Push-Pull推挽输出

(1)可以吸电流,也可以贯电流;

(2)和开漏输出相比,push-pull的高低电平由IC的电源低定,不能简单的做逻辑操作等。

Open-Drain开漏输出

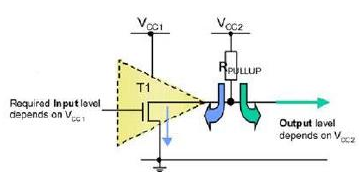

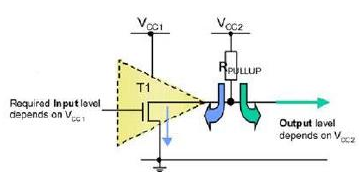

(1)对于各种电压节点间的电平转换非常有用,可以用于各种电压节点的Up-translate和down-translate转换

(2)可以将多个开漏输出的Pin脚,连接到一条线上,形成“与逻辑”关系,即“线与”功能,任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。

(3)利用 外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很下的栅极驱动电流。

(4)可以利用改变上拉电源的电压,改变传输电平:图表 5 open-drain输出电平的原理,IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。

缺点

Push-Pull推挽输出

一条总线上只能有一个push-pull输出的器件;

在CMOS电路里面应该叫CMOS输出更合适,因为在CMOS里面的push-pull输出能力不可能做得双极那么大。输出能力看IC内部输出极N管P管的面积。push-pull是现在CMOS电路里面用得最多的输出级设计方式

Open-Drain开漏输出

开漏Pin不连接外部的上拉电阻,则只能输出低电平。当输出电平为低时,N沟道三极管是导通的,这样在Vcc'和GND之间有一个持续的电流流过上拉电阻R和三极管Q1。这会影响整个系统的功耗。采用较大值的上拉电阻可以减小电流。但是,但是大的阻值会使输出信号的上升时间变慢。即上拉电阻R pull-up的阻值 决定了逻辑电平转换的沿的速度。阻值越大,速度越低功耗越小。反之亦然。

转自: wair-博客