一、电路噪声

对于电子线路中所标称的噪声,可以概括地认为,它是对目的信号以外的所有信号的一个总称。最初人们把造成收音机这类音响设备所发出噪声的那些电子信号,称为噪声。

但是,一些非目的的电子信号对电子线路造成的后果并非都和声音有关,因而,后来人们逐步扩大了噪声概念。

例如,把造成视屏幕有白班呀条纹的那些电子信号也称为噪声。可能以说,电路中除目的的信号以外的一切信号,不管它对电路是否造成影响,都可称为噪声。例如,电源电压中的纹波或自激振荡,可对电路造成不良影响,使音响装置发出交流声或导致电路误动作,但有时也许并不导致上述后果。

对于这种纹波或振荡,都应称为电路的一种噪声。又有某一频率的无线电波信号,对需要接收这种信号的接收机来讲,它是正常的目的信号,而对另一接收机它就是一种非目的信号,即是噪声。在电子学中常使用干扰这个术语,有时会与噪声的概念相混淆,其实,是有区别的。

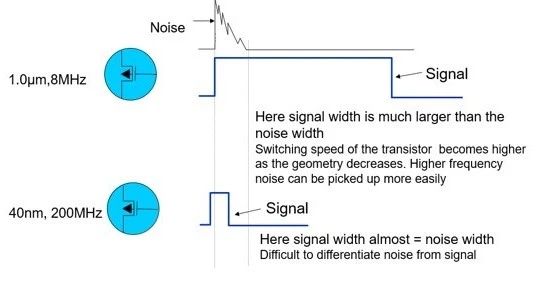

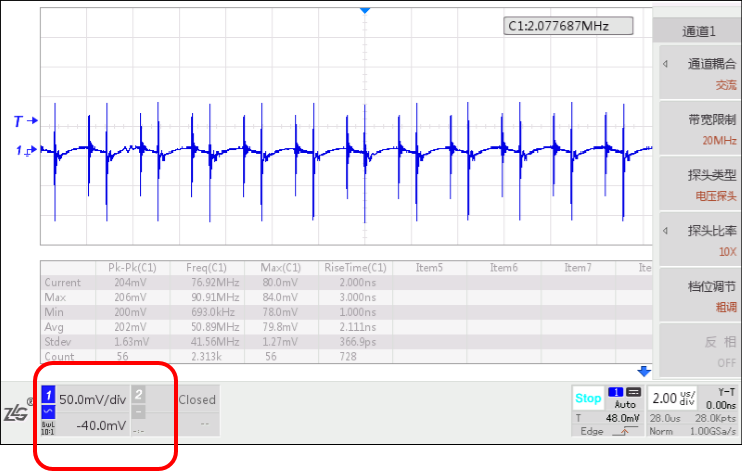

噪声是一种电子信号,而干扰是指的某种效应,是由于噪声原因对电路造成的一种不良反应。而电路中存在着噪声,却不一定就有干扰。在数字电路中。往往可以用示波器观察到在正常的脉冲信号上混有一些小的尖峰脉冲是所不期望的,而是一种噪声。但由于电路特性关系,这些小尖峰脉冲还不致于使数字电路的逻辑受到影响而发生混乱,所以可以认为是没有干扰。

当一个噪声电压大到足以使电路受到干扰时,该噪声电压就称为干扰电压。而一个电路或一个器件,当它还能保持正常工作时所加的最大噪声电压,称为该电路或器件的抗干扰容限或抗扰度。一般说来,噪声很难消除,但可以设法降低噪声的强度或提高电路的抗扰度,以使噪声不致于形成干扰。

二、如何抑制电子电路中噪声的产生

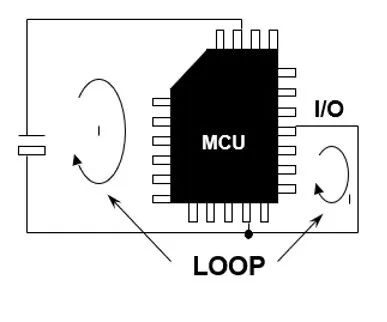

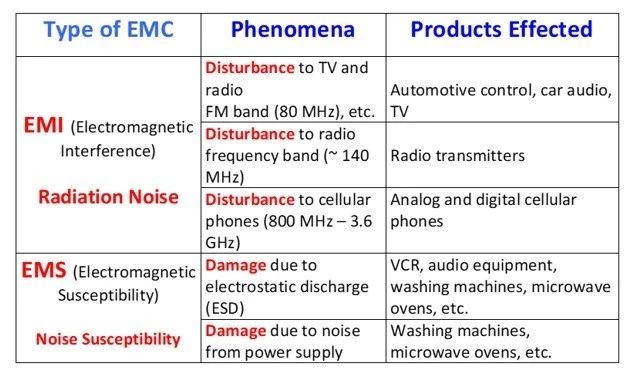

这个东西主要是由于电路中的数字电路和电源部分产生的。在数字电路中,普遍存在高频的数字电平,这些电平可以产生两种噪声:

1、电磁辐射,就像电视的天线一样,通过发射电磁波来干扰旁边的电路,也就是你说的噪声。

2、耦合噪声,指数字电路和旁边的电路存在一定的耦合,噪声可以直接在电器上直接影响其他的电路,这种噪声更厉害。

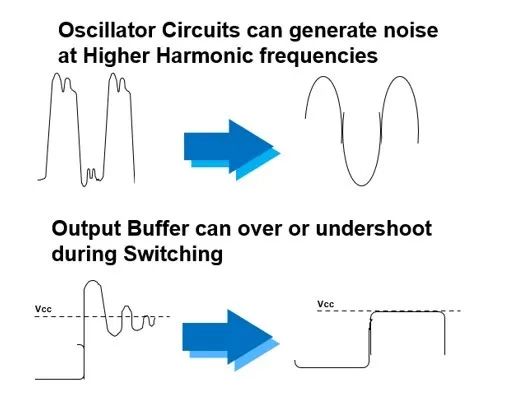

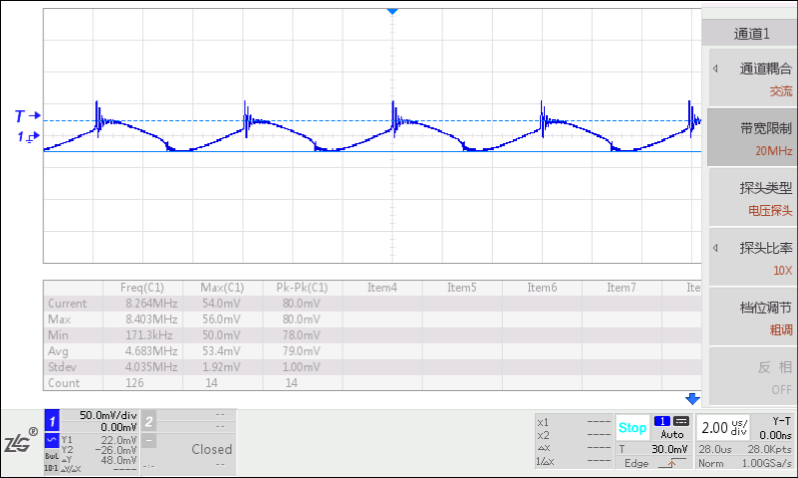

电源上存在的噪声:如果是线性电源,首先低频的50Hz就是一个严重的干扰源。由于初级进来的交流电本身就不纯净,而且是波浪的正弦波,容易对旁边的电路产生电磁干扰,也就是电磁噪声。如果是开关电源的话噪声更严重,开关电源工作在高频状态,并且在输出部分存在很脏的谐波电压,这些对整个的电路都能产生很大的噪声。

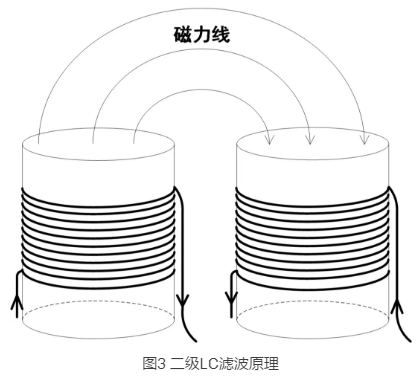

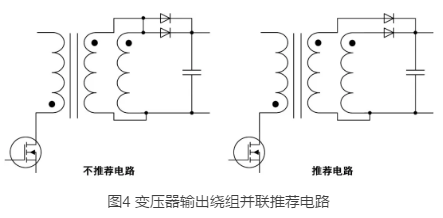

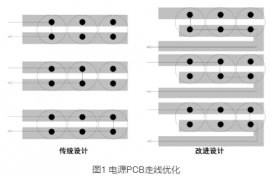

防止方法:合理地接地、采用差分结构传输模拟信号、在电路的电源输出端加去耦电容、采用电磁屏蔽技术、模拟数字地分开、信号线两边走底线、地线隔离等等。其实我说的这些在去除噪声的方面只是冰山一角,就算是玩了30年电子的人也不会完全掌握所有的这类技术,因为理解掌握这类东西需要很强的技术基础和相当丰富的经验,不过我告诉你的这些在大体上已经足够了。

本底噪声是由电路本身引起的,由于电源的不纯净,电路的相位裕度和增益裕度不合适等等电路本身和器件的原因。这部分需要在电路设计时进行改进。

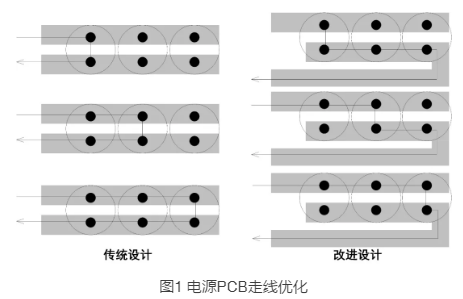

其他噪声是由于电路布局布线不合理等等认为因素,电磁兼容,导线间干扰等等。

模拟电路噪声的消除更多地依赖于经验而非科学依据。设计人员经常遇到的情况是电路的模拟硬件部分设计出来以后,却发现电路中的噪声太大,而不得不重新进行设计和布线。

这种“试试看”的设计方法在几经周折之后最终也能获得成功。不过,避免噪声问题的更好方法是在设计初期进行决策时就遵循一些基本的设计准则,并运用与噪声相关的基本原理等知识。

三、低噪声前置放大器电路的设计方法

前置放大器在音频系统中的作用至关重要。本文首先讲解了在为家庭音响系统或PDA设计前置放大器时,工程师应如何恰当选取元件。随后,详尽分析了噪声的来源,为设计低噪声前置放大器提供了指导方针。最后,以PDA麦克风的前置放大器为例,列举了设计步骤及相关注意事项。

前置放大器是指置于信源与放大器级之间的电路或电子设备,例如置于光盘播放机与高级音响系统功率放大器之间的音频前置放大器。

前置放大器是专为接收来自信源的微弱电压信号而设计的,已接收的信号先以较小的增益放大,有时甚至在传送到功率放大器级之前便先行加以调节或修正,如音频前置放大器可先将信号加以均衡及进行音调控制。无论为家庭音响系统还是PDA设计前置放大器,都要面对一个十分头疼的问题,即究竟应该采用哪些元件才恰当?

四、元件选择原则

由于运算放大器集成电路体积小巧、性能卓越,因此目前许多前置放大器都采用这类运算放大器芯片。我们为音响系统设计前置放大器电路时,必须清楚知道如何为运算放大器选定适当的技术规格。

在设计过程中,系统设计工程师经常会面临以下问题。

1. 是否有必要采用高精度的运算放大器?

输入信号电平振幅可能会超过运算放大器的错误容限,这并非运算放大器所能接受。若输入信号或共模电压太微弱,设计师应该采用补偿电压(Vos)极低而共模抑制比(CMRR)极高的高精度运算放大器。是否采用高精度运算放大器取决于系统设计需要达到多少倍的放大增益,增益越大,便越需要采用较高准确度的运算放大器。

2. 运算放大器需要什么样的供电电压?

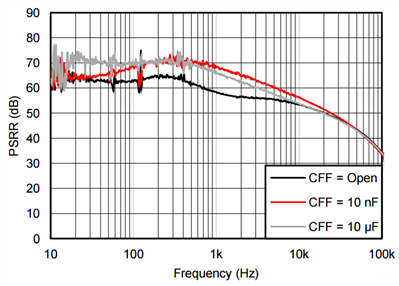

这个问题要看输入信号的动态电压范围、系统整体供电电压大小以及输出要求才可决定,但不同电源的不同电源抑制比(PSRR)会影响运算放大器的准确性,其中以采用电池供电的系统所受影响最大。此外,功耗大小也与内部电路的静态电流及供电电压有直接的关系。

3. 输出电压是否需要满摆幅?

低供电电压设计通常都需要满摆幅的输出,以便充分利用整个动态电压范围,以扩大输出信号摆幅。至于满摆幅输入的问题,运算放大器电路的配置会有自己的解决办法。由于前置放大器一般都采用反相或非反相放大器配置,因此输入无需满摆幅,原因是共模电压(Vcm)永远小于输出范围或等于零(只有极少例外,例如设有浮动接地的单供电电压运算放大器)。

4. 增益带宽的问题是否更令人忧虑?

是的,尤其是对于音频前置放大器来说,这是一个非常令人忧虑的问题。由于人类听觉只能察觉大约由20Hz至20kHz频率范围的声音,因此部分工程师设计音频系统时会忽略或轻视这个“范围较窄”的带宽。事实上,体现音频器件性能的重要技术参数如低总谐波失真(THD)、快速转换率(slewrate)以及低噪声等都是高增益带宽放大器所必须具备的条件。

五、深入了解噪声

在设计低噪声前置放大器之前,工程师必须仔细审视源自放大器的噪声,一般来说,运算放大器的噪声主要来自四个方面:

1. 热噪声(Johnson):由于电导体内电流的电子能量不规则波动产生的具有宽带特性的热噪声,其电压均方根值的正方与带宽、电导体电阻及绝对温度有直接的关系。对于电阻及晶体管(例如双极及场效应晶体管)来说,由于其电阻值并非为零,因此这类噪声影响不能忽视。

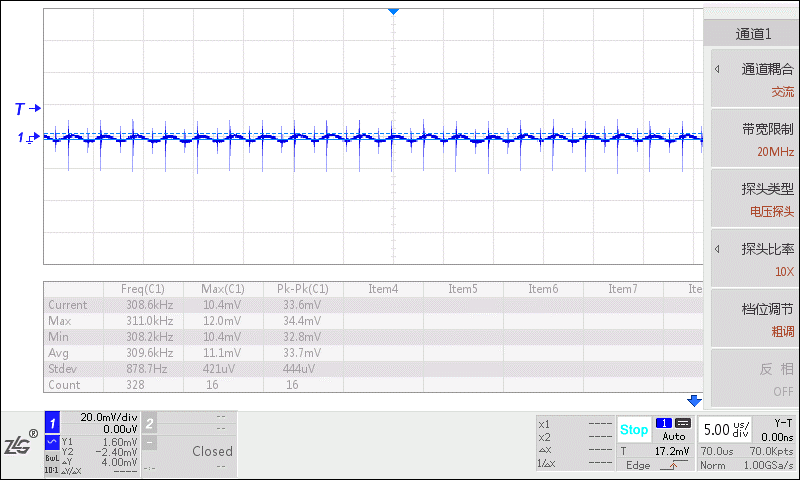

2. 闪烁噪声(低频):由于晶体表面不断产生或整合载流子而产生的噪声。在低频范围内,这类闪烁以低频噪声的形态出现,一旦进入高频范围,这些噪声便会变成“白噪声”。闪烁噪声大多集中在低频范围,对电阻器及半导体会造成干扰,而双极芯片所受的干扰比场效应晶体管大。

3. 射击噪声(肖特基):肖特基噪声由半导体内具有粒子特性的电流载流子所产生,其电流的均方根值正方与芯片的平均偏压电流及带宽有直接的关系。这种噪声具有宽带的特性。

4. 爆玉米噪声(popcornfrequency):半导体的表面若受到污染便会产生这种噪声,其影响长达几毫秒至几秒,噪声产生的原因仍然未明,在正常情况下,并无一定的模式。生产半导体时若采用较为洁净的工艺,会有助减少这类噪声。

此外,由于不同运算放大器的输入级采用不同的结构,因此晶体管结构上的差异令不同放大器的噪声量也大不相同。

下面是两个具体例子。

• 双极输入运算放大器的噪声:噪声电压主要由电阻的热噪声以及输入基极电流的高频区射击噪声所造成,低频噪声电平大小取决于流入电阻的输入晶体管基极电流产生的低频噪声;噪声电流主要由输入基极电流的射击噪声及电阻的低频噪声所产生。

• CMOS输入运算放大器的噪声:噪声电压主要由高频区通道电阻的热噪声及低频区的低频噪声所造成,CMOS放大器的转角频率(cornerfrequency)比双极放大器高,而宽带噪声也远比双极放大器高;噪声电流主要由输入门极漏电的射击噪声所产生,CMOS放大器的噪声电流远比双极放大器低,但温度每升高10(C,其噪声电流便会增加约40%。

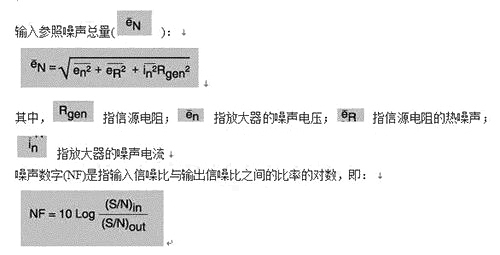

工程师必须深入了解噪声问题及进行大量计算,才可将这些噪声化为数字准确表达出来。为了避免将问题复杂化,这里只选用音频技术规格最关键的几个参数。

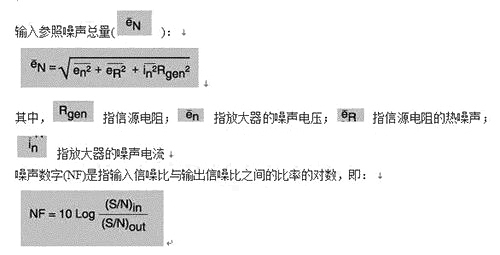

上述方程式中的S及N均为功率。

六、PDA麦克风前置放大器电路

在这里我们讨论一下如何设计一款适合PDA采用的麦克风前置放大器,正如上文所述,我们必须明白信源是输入前置放大器的信号。首先,我们必须知道以下信息:

• 计划采用的麦克风类型

• 麦克风输出信号电平

• 麦克风阻抗及指定阻抗的频率

• 增益规定,有关增益可能受运算放大器的增益带宽积所限制

• 输入信号频率范围

• 噪声规定

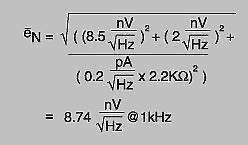

例如某种陶瓷麦克风的技术规格如下:

• 阻抗:2.2k((以1kHz的频率操作)

• 输出信号:200(Vpp

• 音频输入频率范围:100Hz至4kHz

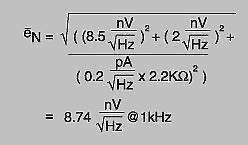

• 热噪声:2nV/(Hz

前置放大器的增益指标:500(非反相),第一级可达5倍增益,第二级可达100倍增益。

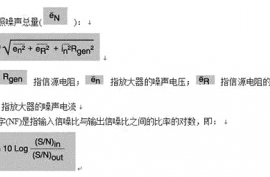

我们引用公式1:

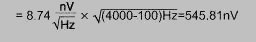

等量输入噪声(EIN)=输入参照噪声总量()×输入频率范围:

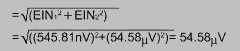

输出噪声=等量输入噪声×增益=545.81nV×5=2.73uV(适用于1级增益)或545.81nV×100=54.58uV(适用于2级增益)。

两个放大级的输出噪声总量:

1伏输出电压的信噪比电平=20×log(1V÷54.58uV)≈85.3dB

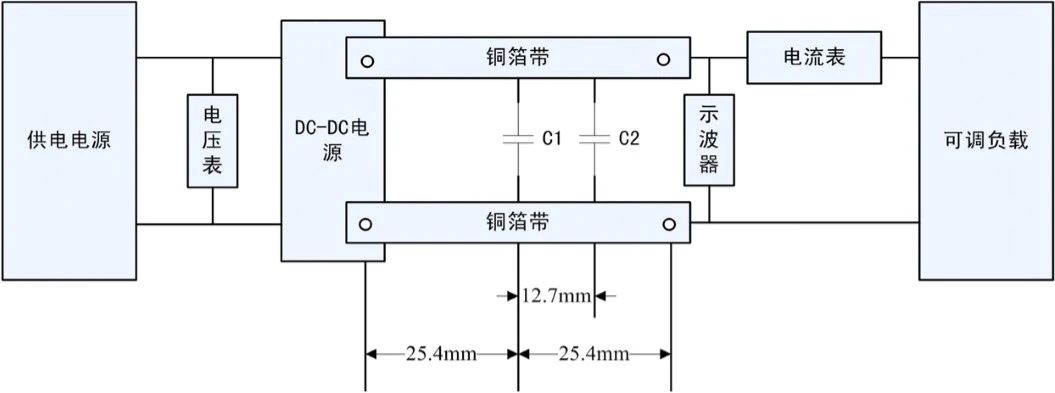

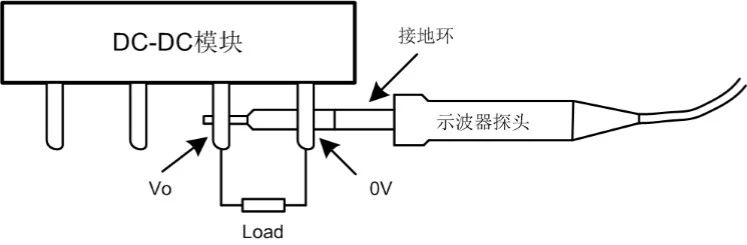

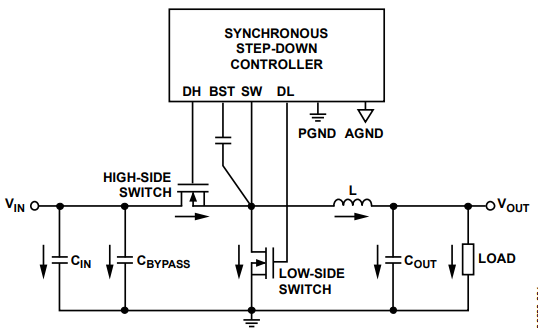

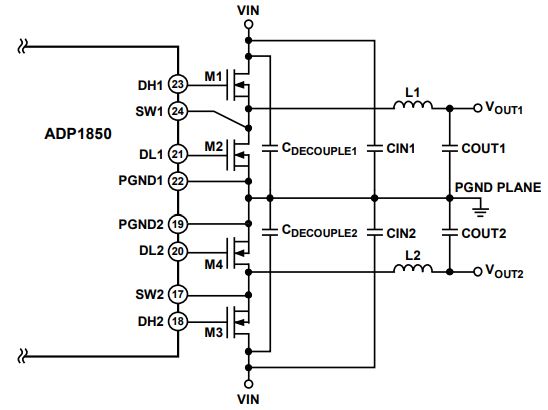

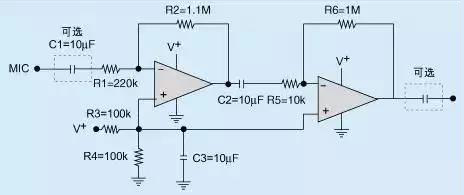

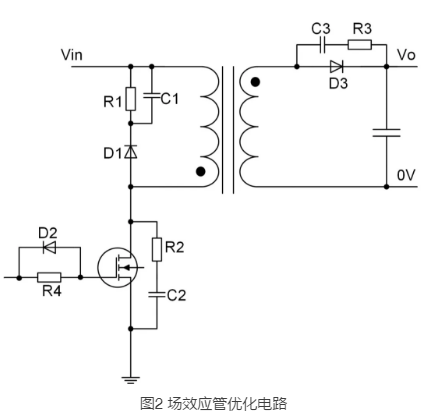

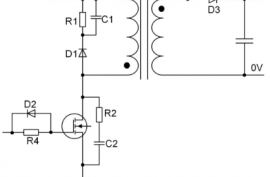

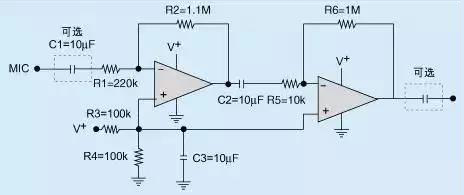

电路输出噪声总量大约是每一噪声源均方根的平均均方值总和的平方根,此外输出噪声通常绝大部分来自噪声量最大的信源。实际电路如图2所示。

MIC前置放大器电路图

MIC前置放大器电路图

请注意,这款电路只适用于单电源供电的设计,其中输入及输出电容器(C1及C4)只是选项,工程师可根据实际情况考虑选用。适用与否取决于用户系统的输入与输出如何连接。若麦克风输出设有直流补偿,那么便需要增设C1输入电容器,以便阻塞直流电信号。输出电容器也可发挥相同的作用。

目前市场上出售的麦克风大部分以2k(左右的高阻抗麦克风以及只有几百(的低阻抗麦克风为主,这两类麦克风都可采用上述前置放大器设计。高阻抗高输出麦克风前置放大器较为简单,可以采用非反相或反相放大器配置。

由于其频率响应较为平坦,因此无需特别加以均衡,而且输入电平较大,放大器对噪声的要求很低,但高阻抗麦克风对来历不明的噪声及磁场极为敏感。低阻抗低输出麦克风前置放大器也可采用非反相或反相放大器将输入信号放大,频率响应及均衡等方面的要求都与高阻抗高输出的前置放大器大致相同。

如果麦克风的输出电平较低,工程师必须注意选用低噪声的运算放大器。如性能较好的低噪声运算放大器应该产生较低的输入参照电压噪声,而且噪声不应超过10nV/((Hz)。

七、运算放大器电路中固有噪声的分析与测量

我们可将噪声定义为电子系统中任何不需要的信号。噪声会导致音频信号质量下降以及精确测量方面的错误。板级与系统级电子设计工程师希望能确定其设计方案在最差条件下的噪声到底有多大,并找到降低噪声的方法以及准确确认其设计方案可行性的测量技术。

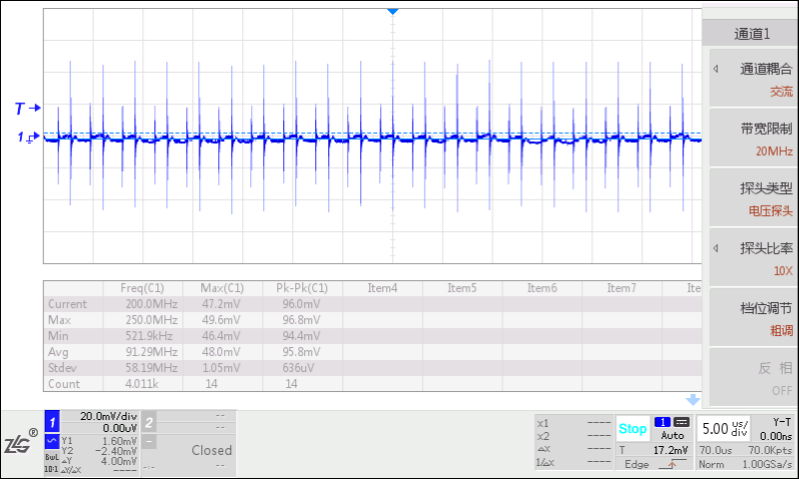

噪声包括固有噪声及外部噪声,这两种基本类型的噪声均会影响电子电路的性能。外部噪声来自外部噪声源,典型例子包括数字交换、60Hz噪声以及电源交换等。

固有噪声由电路元件本身生成,最常见的例子包括宽带噪声、热噪声以及闪烁噪声等。本系列文章将介绍如何通过计算来预测电路的固有噪声大小,如何采用SPICE模拟技术,以及噪声测量技术等。

转自:电子工程专辑