高压电路设计需要通过隔离来保护操作人员、与低压电路进行通信并消除系统内不必要的噪声。数字隔离器提供了一种简单可靠的方法,可以在工业和汽车应用中实现高压隔离通信。

要保持信号通过隔离栅的完整性,需要隔离电路初级侧和次级侧之间的所有耦合路径,包括电源。虽然数字隔离器的次级侧通常需要很少的电源,但系统设计者常常会增加额外的电源余量,以便为多个设备供电。

在本文中,我们将分享在隔离信号和电源设计时经常出现的问题,并简要概述可用的分立式和集成式器件。

问题 1、为什么要隔离数字隔离器的电源?

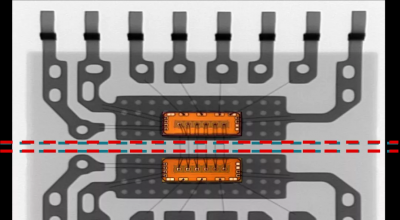

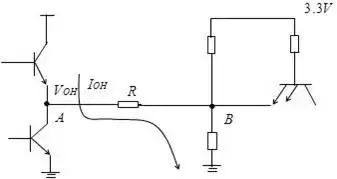

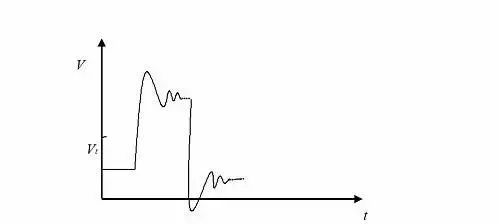

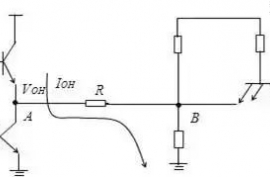

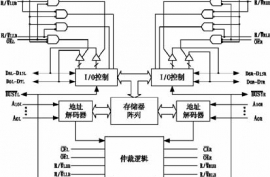

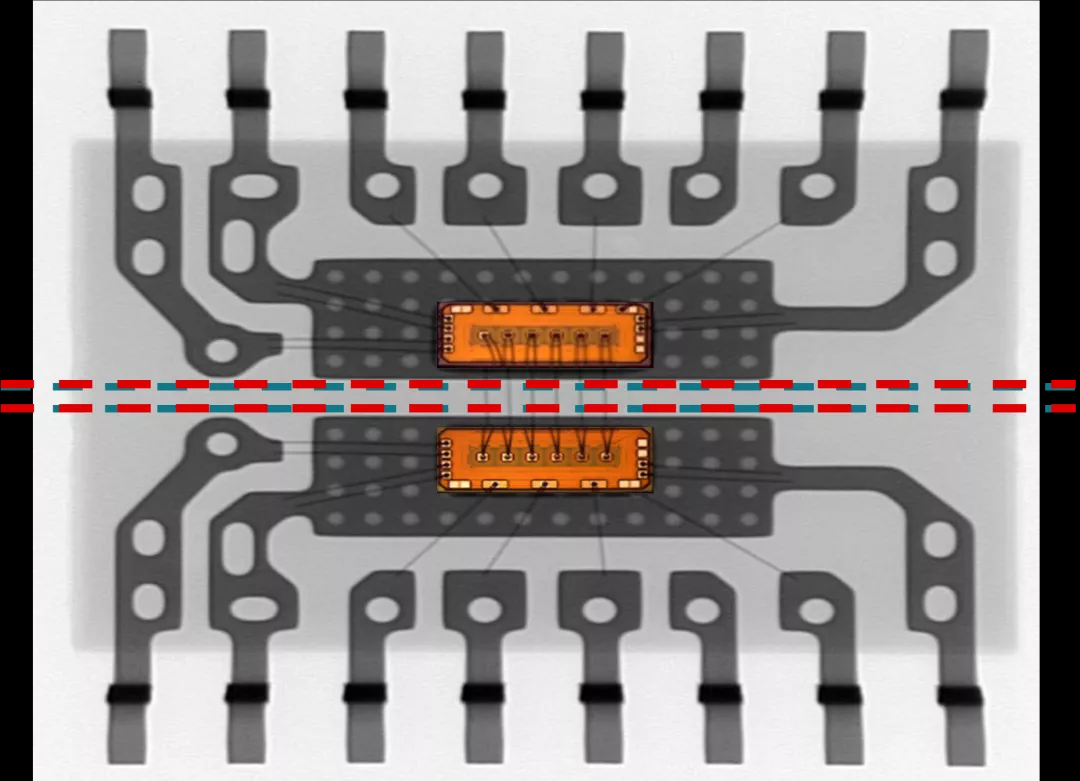

数字隔离器的内部架构由两个独立的数字集成电路 (IC) 组成,位于分离式引线框上,它们之间有一个高压隔离电介质屏障,如图1所示。每个IC都需要为设备的初级侧和次级侧提供单独的电源和接地,它们之间没有物理连接。此要求与器件支持基本隔离还是增强型隔离无关,适用于数字隔离器以及具有集成接口的隔离器件。

问题 2、数字隔离器的电源要求是什么?

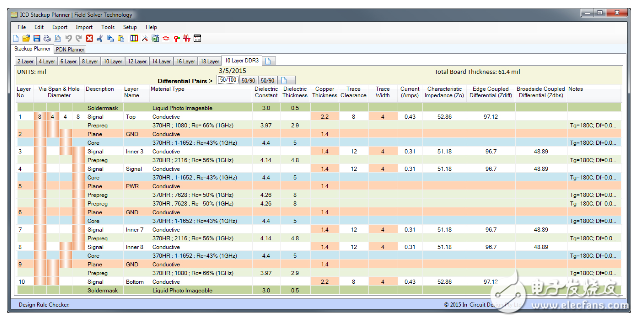

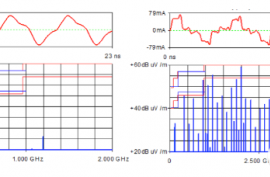

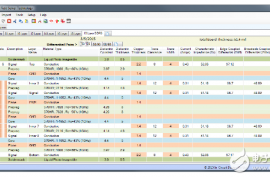

在为数字隔离器解决方案选择电源拓扑之前,重要的是要确定电源的基本要求,包括输入电压范围、输出电压、次级侧所需的输出功率和输出轨的数量。与非隔离电源解决方案相比,隔离电源解决方案的其他考虑因素包括系统绝缘额定值、所需的爬电距离和间隙距离,以及静电放电和系统的发射性能等电磁兼容性要求。行业终端设备标准对上述多种要求进行了规定。

数字隔离器的输入和输出信号电压通常取决于它们所施加的电源电压,并且通常与次级侧的电源电压(VCC)有直接关系。在最终确定电源输入和输出要求之前,建议仔细查看数字隔离器数据表中的电源要求。针对接口元件的逻辑电平来优化数字隔离器也是一个好主意。例如,为与微控制器连接的数字隔离器提供5V电压时,选择在次级侧也使用5V或接近5V逻辑电平的信号。

问题 3、次级侧电源可以用作隔离电源吗?

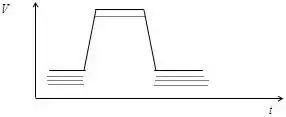

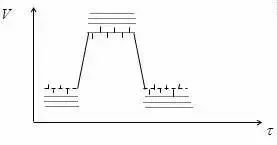

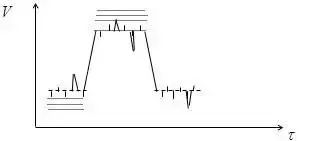

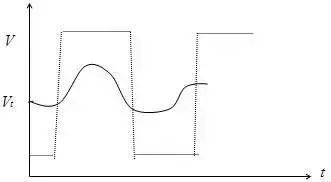

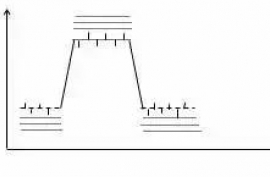

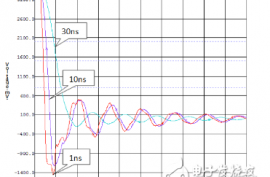

在某些情况下,只要满足隔离器逻辑电平的最低要求,系统中的两个独立电源轨即可用作初级侧和次级侧电源。其中包括与输入和输出信号电平相匹配的电源电压电平,每个电平均提供单独的接地。虽然可以使用现有的次级侧电源,但噪声耦合和电源调节通常会成为一项问题,设计者通常选择设计已针对逻辑电平和系统噪声性能进行了优化的隔离电源。

问题 4、隔离电源有哪些解决方案?

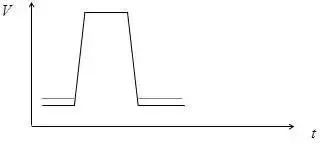

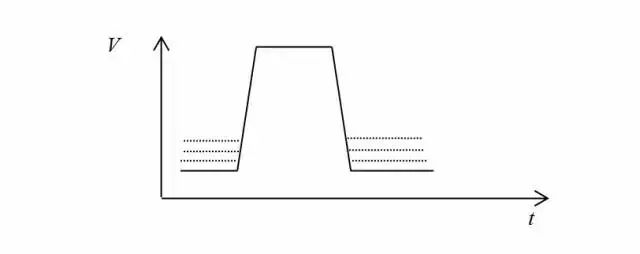

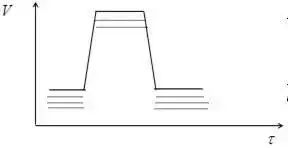

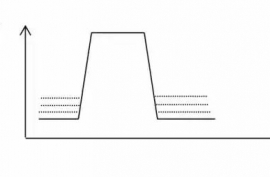

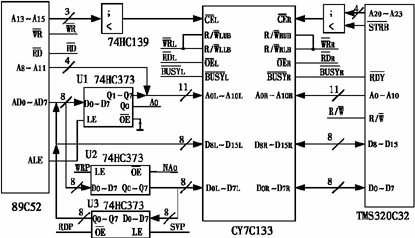

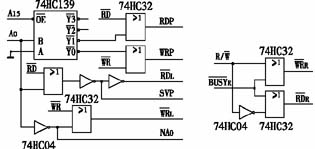

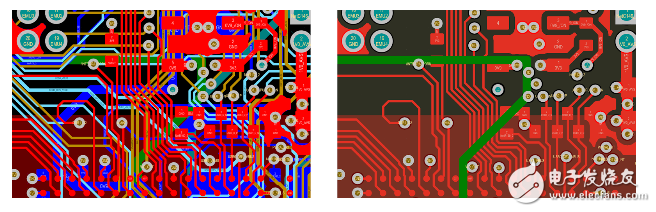

为数字隔离电路设计隔离电源时,可以使用的方案有许多。数字隔离器的电源解决方案包括反激式、H桥电感器-电感器-电容器、推挽式和集成式隔离数据和电源解决方案。

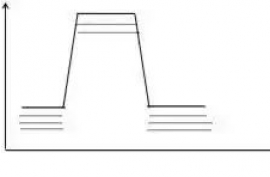

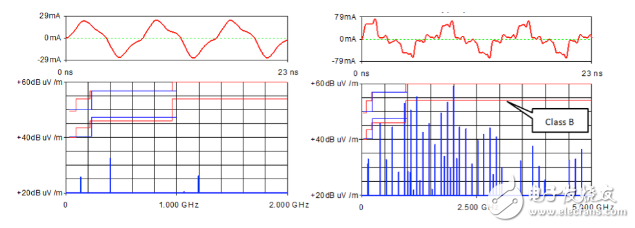

带电源的ISOW7741数字隔离器、带电源的ISOW1412隔离式RS-485收发器或带电源的ISOW1044控制器局域网收发器等集成的隔离数据和电源解决方案都具有集成式直流/直流转换器。这些器件旨在满足国际无线电干扰特别委员会(CIPSR) 32 B类限制,而且其尺寸明显小于分立式设计备选方案。为了在尽可能小的占用空间中实现高性能设计,无需在电路板上安装变压器、减小电路板尺寸和简化认证等优势通常是不容忽视的权衡因素。

因此,虽然分立式解决方案在某些情况下可以提高效率和降低辐射发射,但最终节省空间和简化认证的优势能够加快上市速度。

来源:德州仪器

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。