低功耗设计

引言:

用电池供电的产品来说能耗是一个重大的问题,一旦电能耗尽设备将“罢工”。在《MCU低功耗设计(一)理论》中,我们介绍了节能的原理,本文用万用表和MCU电路板,真刀真枪地测试功耗值。简单,但绝对真实的测试数据,看看官方宣称低功耗与实测结果有多大差距,Let’s Go知识库" Go!

说明:

博客的书写工具对于图片的编辑支持力度不够,喜欢本博文的读者可以从以下链接下载PDF版本的博文,那将是一个更好的排版文档。

http://download.csdn.net/detail/jiangjunjie_2005/8966291

一. 搭建测试环境

1. 硬件平台:

选用“长沙市锐米通信科技有限公司(www.rimelink.com)”的无线通信模块iWL881A(下图左),考虑只测试MCU能耗,特地将无线电射频模块去除(下图右),MCU为ST公司超低功耗STM8L151C8T6。

2. 软件平台:

开发平台选用IAR集成开发环境,它的具体型号如右图:

3. 测试工具:

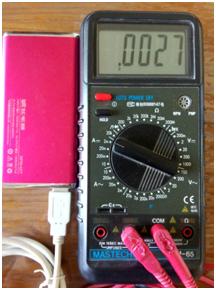

超高精度测低功耗,需要电池模拟器,那玩意可是RMB二十多万一台;老外(如Contiki之父Adam Dunkels)经常接100欧姆电阻,用示波器算积分,比较繁杂;我们使用最简单的办法,串联电流表,不要小看它,测量到uA的精度是可行的。测试环境搭建如下图所示

二. 低功耗模式下功耗测试

测试MCU低功耗比较科学的办法是,采用加法原则,即,首先测试最低工作状态下功耗,然后累加外设或I/O引脚,一步一步测试使能部件的功耗值。

为更好地测试STM8L151C8的功耗,我们写了一个C语言测试软件,它把MCU的5种低功耗运行模式都包括在内。当测试对应的运行模式时,只需要修改宏定义:#define MCU_MODE MODE_xxxxxx。

读者可以从以下链接直接下载该测试代码:

http://download.csdn.net/detail/jiangjunjie_2005/8959145

以下链接下载本博文的姊妹篇:

《MCU低功耗设计(一)理论》

http://download.csdn.net/detail/jiangjunjie_2005/8957767

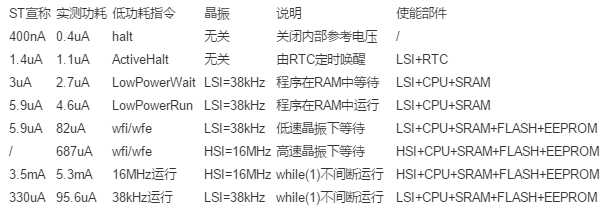

1. Halt功耗

将测试代码宏定义设置为:

#define MCU_MODE MODE_HALT

编译并烧录到MCU中,并电流表调整到2mA量程。可以看到,HALT模式下,功耗为0.4uA。

ST公司产品手册:Halt(400 nA)

看来,有信仰的民族(西欧基本都是基督教徒)更容易说真话呀!

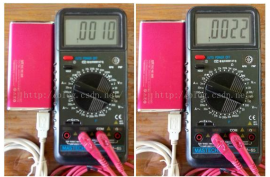

2. Active-Halt功耗

将测试代码宏定义设置为:#defineMCU_MODE MODE_ACTIVE_HALT,编译并烧录到MCU中,电流表仍为2mA量程。可以看到,Active-Halt模式下,功耗为1.0uA和2.2uA,为什么会有2个值呢?

如果您看过本系列的第一篇博文《MCU低功耗设计(一)理论》,那就知道,较低的功耗(1.0uA)是Halt状态,而较高的功耗(2.2uA)是唤醒状态。为什么同样是停止,Active-Halt(1.0uA)比Halt(0.4uA)功耗要高呢?答案是,前者有一个38kHz的内部RC晶振在运行,它给RTC提供时钟源,它也需要电能哦!

ST公司产品手册:Active-halt with full RTC(1.4 uA)

如果我们把1.0uA和2.2uA简单地取个平均,那将是1.6uA,和官方数据还是接近吧。当然,要更精确测量,需要拿示波器记录唤醒时间的占空比,这个工作留给更严谨的后续者来完成吧(记得给读者发博文,科技报国,需要身体力行!)。

3. LowPowerWait功耗

将测试代码宏定义设置为:

#define MCU_MODE

MODE_LOW_POWER_WAIT,

可以看到功耗为:2.7uA。

ST公司产品手册:Low power wait(3 uA)

那个0.3uA可以算测试误差否?欢迎讨论。

4. LowPowerRun功耗

将宏定义设置为:

#define MCU_MODE

MODE_LOW_POWER_RUN

该模式下功耗为:4.6uA。

ST公司产品手册:Low power run(5.9 uA).

实测功耗比官方宣称功耗还低1.3uA。

我们一起看看该模式下MCU的工作原理。

①进入“Low power run”模式的代码序列:

l 跳转到RAM;

l 切换系统时钟到LSI或LSE;

l 关闭高速晶振、ADC和没有使用的外设;

l 屏蔽所有中断;

l 关闭FLASH和EEPROM;(添加软件延时,确保关闭成功)

l 配置低功耗电压调节器。

②退出“Low power run”模式的代码序列:

l 打开主电压调节器;

l 打开FLASH和EEPROM;

l 使能所有中断;

l 打开需要使用的外设,如有必要跳转到FLASH和EEPROM。

特别注意的是,Lowpower run模式下,MCU是从RAM(不是ROM)取指令解析执行,因为需要将该代码段定位到RAM中。在IAR环境下,将代码段定位于RAM,需要在函数前加关键字“__ramfunc”。实例函数申明如下:

__ramfunc void LPR_Ram(void)

5. Wait功耗

看过第一篇博文《MCU低功耗设计(一)理论》的读者会了解到,Wait模式下仅CPU暂停运行,这样一来晶振可以是HSI(内部高速)或LSI(内部低速)。我们先测试HIS模式下功耗,设置模式:#define MCU_MODE MODE_WAIT,设置时钟:#define IS_ENABLE_LSI 0。实测功耗为:687uA,下图右所示。

再测试LIS模式下功耗,设置模式:#define MCU_MODE MODE_WAIT,设置时钟:#define IS_ENABLE_LSI 1,实测功耗为:82uA,下图左所示。

ST公司产品手册:Wait, Low power run(5.9 uA)

为什么会有如此大的差距,这个答案肯怕得ST公司的技术人员来回答了!

6. Run功耗

当MCU以HSI(16MHz)高速运行时,它的功耗如下图左所示:5.3mA(实测时小数点后2和3位在跳动)。

ST公司产品手册:Consumption: 200 uA/MHz + 330 uA.

按上述公式计算,理论功耗应该是3.5mA,与实测值5.3mA有较大差别,很想ST公司的技术人员来解答下。

当MCU以LSI(38kHz)低速运行时,它的功耗如下图右所示:95.6uA。按官方宣称Static能耗330uA,相差也不小。

我们一起总结下上述运行模式下功耗和使能部件。

三.I/O引脚与外设功耗测试

外设需要HSI(高速外部晶振)或LSI(低速晶振)提供时钟源,因此测试外设一般工作在Wait模式下:此时CPU停止运行,将外设开启的测量功耗值减去关闭时的测量功耗值,即可得该外设的运行功耗值。

外设数目比较多,我们测试一些常用的外设功耗如下:

I/O引脚属于模拟器件,往往它的功耗更高,如在上述测试电路有一Pin5(PA4),它连接到LED上。使能与禁止该LED引脚后,测得电流为320uA。

一般而言,I/O引脚需要连接到一个确定的逻辑电平。对于所有没有连接到确定逻辑信号的I/O引脚需要改变配置,否则,外部噪声会导致功耗增加,如引脚内部的施密特触发器检测噪声的翻转而消耗能量:输入引脚配置成上拉;输出引脚配置低(或高)的逻辑电平。

来源链接:http://blog.csdn.net/jiangjunjie_2005/article/details/47304927

一.MCU耗能因素

现代的MCU一般使用CMOS技术,耗能包括2方面:

静态消耗 主要是晶体管消耗能量;

动态消耗 公式=C×V2×f,其中C是CMOS的负载电容,V是供电电压,f是时钟频率;

总电能消耗是静态消耗和动态消耗之和,即:IDD=f×IDynamicRun[uA/MHz]+IStatic[uA].

因此,电能消耗依赖于:

MCU芯片尺寸 或者说晶体管的数目;

MCU供电电压 降低电压可以成平方级别地降低电能消耗;

时钟频率 可以把时钟频率降低到刚好满足应用需要;

外设数目 使能的外设越多,耗能越大;

运行模式 合理选择工作模式可以大幅节能,如,全速工作极短时间后进入睡眠模式。

二.节能方法

1. 关闭不需要使用的外设;

2. 所有未使用的引脚必须连接到一个确定的逻辑电平;

3. 当有外设必须保持激活时,使用Wait模式来获得低功耗;

4. 使用合适的VDD值;

5. 尽可能地使用低功耗运行模式;

6. 如果不能使用低功耗模式,那就将主频降低到满足应用的最小值;

7. 如果可能,使用动态控制I/O引脚的上拉功能。

三.低功耗模式

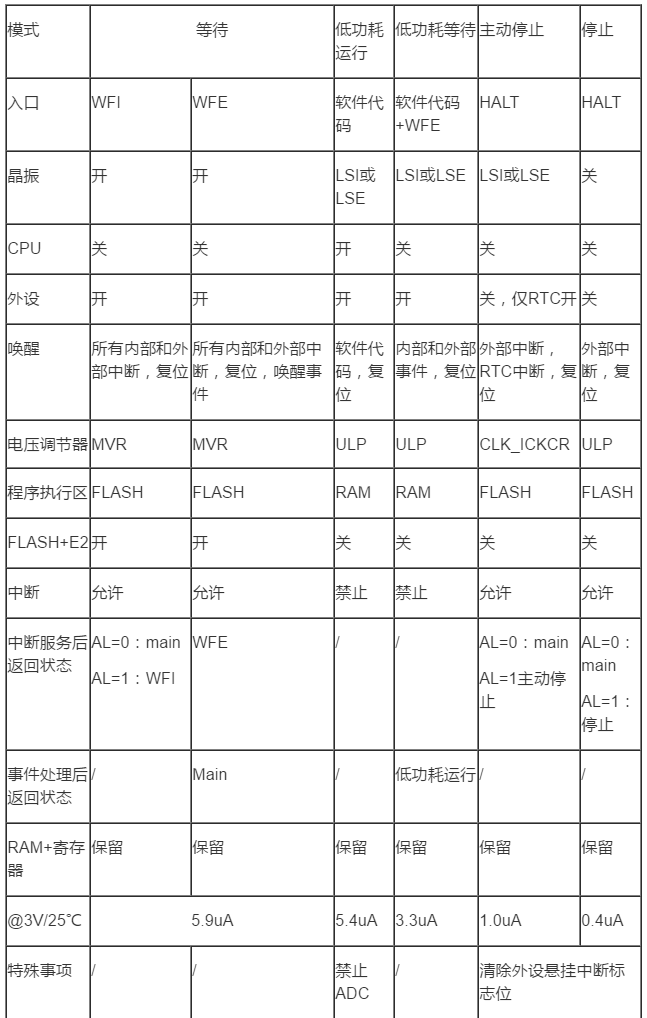

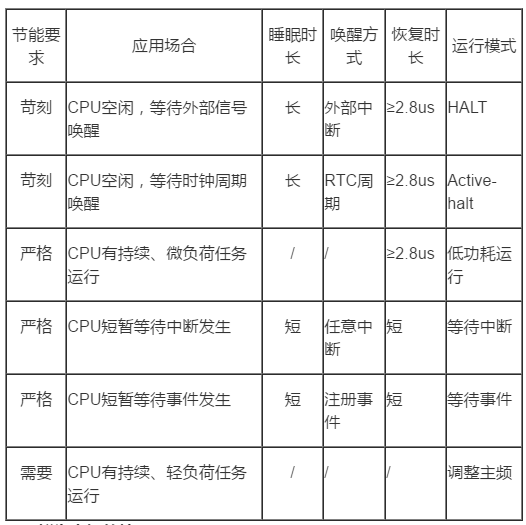

支持低功耗的MCU一般都有好几种运行模式,以ST公司的STM8L为例,它支持5种低功耗模式:等待、低功耗运行、低功耗等待、主动停止和停止。每一种模式的进入方式,节能级别和外设工作要求,总结表1:

表1 STM8L低功耗运行模式

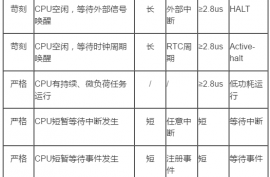

上述低功耗运行模式对于开发者来说有点多,尤其刚接触STM8L处理器。我们需要一般性的指导原则,表2是来源于实践的经验。

表2 选择合理的STM8L节能模式

四.鲜为人知的技巧

1. 使用Wait替换查询方式达到节能目的

常见的查询方式如下,此时CPU无事可干,白白消耗电能。

ADC_CR1 = ADC_START; /* start conversion */

while (!(ADC_SR & ADC_SR_EOC)) ; /* wait for EOC bit set */

可以使用等待事件的方式来节省电能。

先配置ADC为事件源,并使能相应的中断:

WFE_CR2 = ADC_COMP_EV; /* enable ADC as a source of event */

ADC_CR1 = ADC_EOCIE; /* enable interrupt for end of conversion */

当ADC转换完成后,唤醒处于等待的CPU:

ADC_CR1 = ADC_START; /* start conversion */

_asm(“wfe”); /* enter wait mode until waked by ADC_EOCIE*/

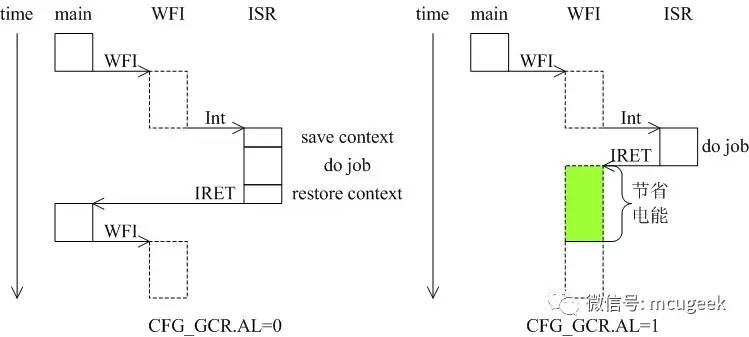

2. 无须上下文切换的中断模式

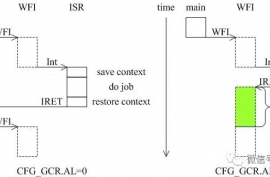

应用程序设计时,如果所有中断事件由ISR完成,可以通过将CFG_GCR寄存器中AL位置1来节省电能:避免保存/恢复context、无须主程序运行(返回到WFI模式),如下图1所示。

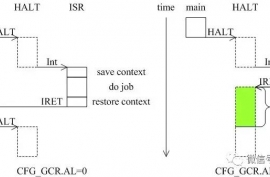

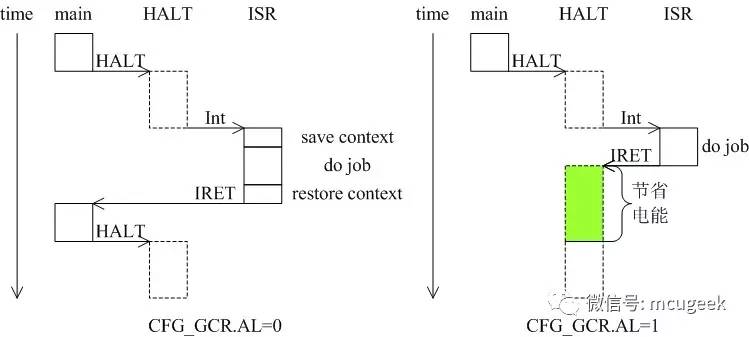

将AL位置1节省电能的方法同样可以用于HALT模式,原理如下图2所示。

3. 动态设置I/O口的上拉功能

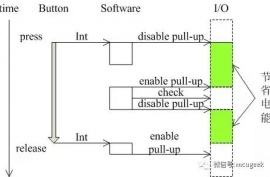

很多应用需要按键作为人机接口,按键一般连接到I/O上。当按键没有动作时I/O口设置内部上拉而获得确定的逻辑电平;一旦按键按下,I/O口对地导通将产生额外的40~70uA电流,这对于电池供电的低功耗来说是十分重要的。

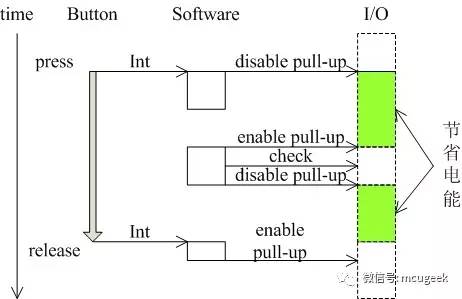

可以动态地控制I/O口的上拉达到节能的目的:一旦按键按下,中断服务程序将禁止该I/O口的上拉功能;然后软件定时执行—先使能上拉功能,再检测I/O口状态,如果按键仍按下再次禁止上拉功能,否则使能I/O口的上拉功能。整个逻辑如下图3所示:

4. CPU空闲节能策略

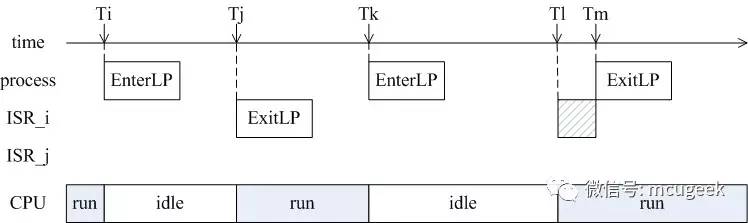

CPU的空闲节能如下图4所示,它的逻辑包括以下几个步骤:

(1)发现CPU空闲:带OS系统,表现为任务没有事件需要响应,或者进入idle进程;无OS系统,表现为程序运行结束。

(2) 选择一种合适的CPU节能模式:chip_EnterLowPower()完成进入节能前的准备工作,包括:关闭外设,切换I/O引脚到节能状态。

(3) 退出节能模式需要调用chip_ExitLowPower(),可能发生在以下2种情形:

a. 需要使用被关闭外设的ISR:

b. 由process直接退出;

chip_ExitLowPower()的善后工作包括:使能外设,切换I/O引脚到工作状态。同时为避免ISR和process两次操作chip_ExitLowPower(),该

函数设置了状态变量避免重复退出。

来源:http://blog.csdn.net/jiangjunjie_2005/article/details/47272017