6月14日,2023上海国际嵌入式展在上海世博展览馆3号馆盛大开幕。随着数字化与智能时代的到来,嵌入式产业在中国迅速崛起,新型的产业形态吸引越来越多的中国企业进入新的业务板块,展会涵盖嵌入式产业软件、系统、硬件、工具等全产业链关键环节。

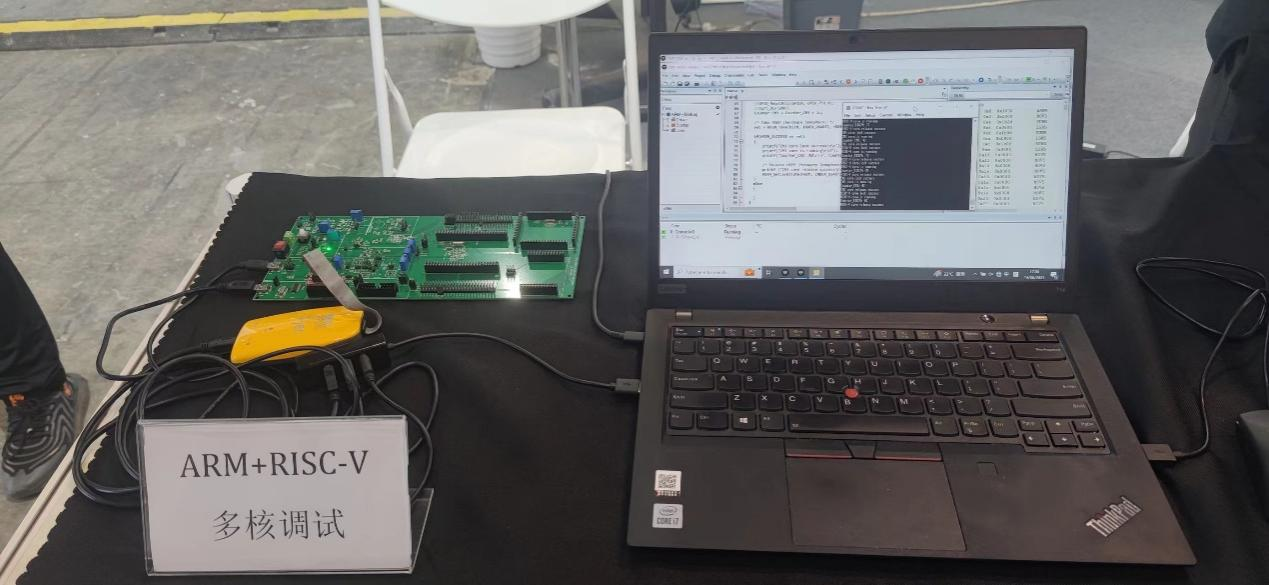

IAR Systems作为全球领先的嵌入式系统开发工具和服务的供应商,在本次展会给大家展示了多核调试技术。航顺芯片作为IAR System合作伙伴,提供了ARM+RISC-V异构多核MCU硬件平台。“嵌入式多核系统可分为同构多核和异构多核,航顺芯片HK32U3009采用ARM+RISC-V异构多核架构,在国产嵌入式MCU中属于国内首创!”IAR System工程师说道。

HK32U3009采用了ARM-Cortex和RISC-V异构双核架构,填补国产异构多核MCU芯片技术空白。该芯片还带有MMU硬件级系统资源访问权限管理,采用自研IPC双核通讯协议,高效实现双核间数据交互,并且支持双线SWD调试和五线JTAG调试。

ARM+RISC-V多核测试

多核基本概念同构多核(Homogeneous)vs 异构多核(Heterogeneous)

从硬件设计上,多核可以分为同构多核和异构多核:同构多核指的是所有的CPU内核具用相同的架构,比如NXP的S32K3(Cortex-M7)和芯驰科技的E3(Cortex-R5)。异构多核指的是CPU内核具用不同的架构,比如Infineon的Traveo T2G(Cortex-M0+ + Cortex-M4/Cortex-M7)和ST的STM32H7 (Cortex-M4 + Cortex-M7)。航顺的HK32U3009(ARM + RISC-V)属于异构多核。

对称多处理(SMP)vs 非对称多处理(AMP)

从软件设计上,多核可以分为对称多处理(SMP)和非对称多处理(AMP):SMP指的是所有的CPU内核运行同一套程序(一般通过CoreID来实现不同的CPU内核执行不同的操作),AMP指的是不同的CPU内核运行不同的程序。只有同构多核才能实现SMP,同构多核也可以实现AMP,异构多核只能实现AMP。

想详细了解多核调试技术,请点击链接:在 IAR Embedded Workbench中进行ARM+RISC-V多核调试

来源:航顺芯片

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。