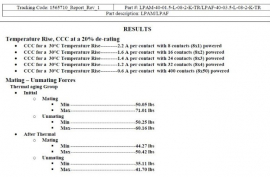

PCB板

PCB板的储存及保质期

demi 在 提交

R107、C118、D202……PCB板上这些字母的含义,你造吗?

demi 在 提交

PCB板设计工艺十大缺陷总结

demi 在 提交

一、PCB板表面处理:

抗氧化,喷锡,无铅喷锡,沉金,沉锡,沉银,镀硬金,全板镀金,金手指,镍钯金 OSP: 成本较底,可焊性好,存储条件苛刻,时间短,环保工艺、焊接好 、平整 。

喷锡:喷锡板一般为多层(4-46层)高精密度PCB样板,已被国内多家大型通讯、计算机、医疗设备及航空航天企业和研究单位都可以用到,金手指(connecting finger)是内存条上与内存插槽之间的连接部件,所有的信号都是通过金手指进行传送的。

金手指由众多金黄色的导电触片组成,因其表面镀金而且导电触片排列如手指状,所以称为“金手指”。

金手指实际上是在覆铜板上通过特殊工艺再覆上一层金,因为金的抗氧化性极强,而且传导性也很强。

不过因为金昂贵的价格,目前较多的内存都采用镀锡来代替,从上个世纪90年代开始锡材料就开始普及,目前主板、内存和显卡等设备的“金手指”几乎都是采用的锡材料,只有部分高性能服务器/工作站的配件接触点才会继续采用镀金的做法,价格自然不菲的。

二、为什么要用镀金板

随着IC的集成度越来越高,IC脚也越多越密。而垂直喷锡工艺很难将成细的焊盘吹平整,这就给SMT的贴装带来了难度;另外喷锡板的待用寿命(shelf life)很短。

而镀金板正好解决了这些问题:

1、对于表面贴装工艺,尤其对于0603及0402 超小型表贴,因为焊盘平整度直接关系到锡膏印制工序的质量,对后面的再流焊接质量起到决定性影响,所以,整板镀金在高密度和超小型表贴工艺中时常见到。

2、在试制阶段,受元件采购等因素的影响往往不是板子来了马上就焊,而是经常要等上几个星期甚至个把月才用,镀金板的待用寿命(shelf life)比铅锡合金长很多倍,所以大家都乐意采用。

再说镀金PCB在度样阶段的成本与铅锡合金板相比相差无几。

但随着布线越来越密,线宽、间距已经到了3-4MIL。

因此带来了金丝短路的问题:随着信号的频率越来越高,因趋肤效应造成信号在多镀层中传输的情况对信号质量的影响越明显。

趋肤效应是指:高频的交流电,电流将趋向集中在导线的表面流动。根据计算,趋肤深度与频率有关。

为解决镀金板的以上问题,采用沉金板的PCB主要有以下特点:

1、因沉金与镀金所形成的晶体结构不一样,沉金会呈金黄色较镀金来说更黄,客户更满意。

2、沉金较镀金来说更容易焊接,不会造成焊接不良,引起客户投诉。

3、因沉金板只有焊盘上有镍金,趋肤效应中信号的传输是在铜层不会对信号有影响。

4、因沉金较镀金来说晶体结构更致密,不易产成氧化。

5、因沉金板只有焊盘上有镍金,所以不会产成金丝造成微短。

6、因沉金板只有焊盘上有镍金,所以线路上的阻焊与铜层的结合更牢固。

7、工程在作补偿时不会对间距产生影响。

8、因沉金与镀金所形成的晶体结构不一样,其沉金板的应力更易控制,对有邦定的产品而言,更有利于邦定的加工。同时也正因为沉金比镀金软,所以沉金板做金手指不耐磨。

9、沉金板的平整性与待用寿命与镀金板一样好。

对于镀金 工艺来讲,其上锡的效果上大打折扣的, 而沉金的上锡效果是比较好一点的;除非厂家要求的是绑定,不然现在大部分厂家会选择沉金 工艺

一般常见的情况下PCB表面处理为以下几种:

镀金(电镀金,沉金),镀银,OSP,喷锡(有铅和无铅)。

这几种主要是针对FR-4或CEM-3等板材来说的,纸基料还有涂松香的表面处理方式;上锡不良(吃锡不良)这块如果排除了锡膏等贴片厂家生产及物料工艺方面的原因来说。

这里只针对PCB问题说,有以下几种原因:

1、在PCB印刷时,PAN位上是否有渗油膜面,它可以阻挡上锡的效果;这可以做漂锡试验来验证。

2、PAN位的润位上否符合设计要求,也就是焊盘设计时是否能足够保证零件的支持作用。

3、焊盘有没有受到污染,这可以用离子污染测试得出结果;以上三点基本上是PCB厂家考虑的重点方面。

关于表面处理的几种方式的优缺点,是各有各的长处和短处!

镀金方面,它可以使PCB存放的时间较长,而且受外界的环境温湿度变化较小(相对其它表面处理而 言),一般可保存一年左右时间;喷锡表面处理其次,OSP再次,这两种表面处理在环境温湿度的存放时间要注意许多。

一般情况下,沉银表面处理有点不同,价格也高,保存条件更苛刻,需要用无硫纸包装处理!并且保存时间在三个月左右! 在上锡效果方面来说,沉金, OSP,喷锡等其实是差不多的,厂家主要是考虑性价比方面!

来源:EDA365电子论坛

为什么PCB板上要镀金和镀银?

demi 在 提交

PCB板和集成电路有什么区别?

demi 在 提交

PCB板设计工艺十大缺陷总结

demi 在 提交