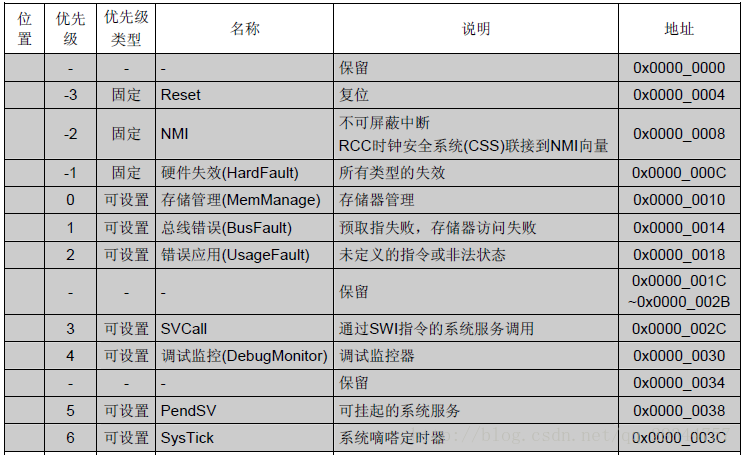

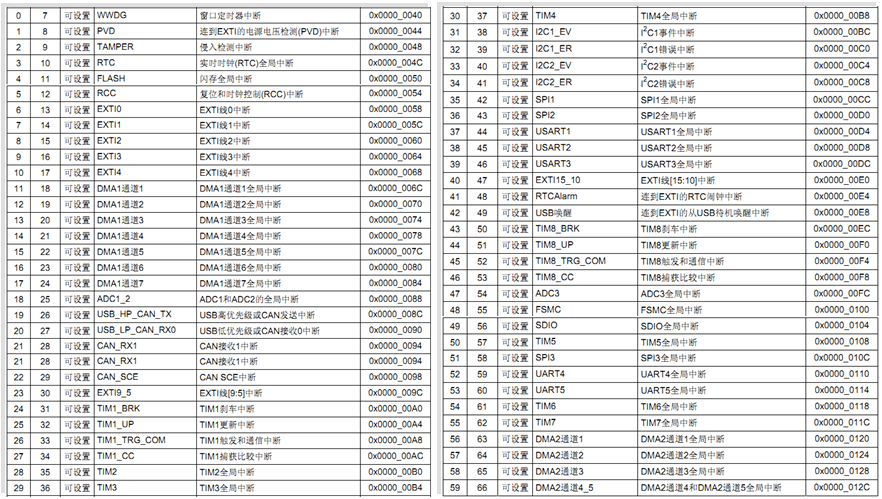

本课将为大家讲解CKS32F4xx系列产品的中断优先级管理单元NVIC。CM4内核共支持256个中断,其中包含了16个内核中断和240个外部中断,具有256级可编程中断设置。但CKS32F4xx系列只使用了CM4内核的一部分,共有98个中断,包括16个带有FPU核的CM4中断和82个可屏蔽中断,而我们常用的就是这82个可屏蔽中断。

NVIC寄存器简介

MDK为NVIC相关寄存器其定义了如下的结构体:

typedef struct

{

__IO uint32_t ISER[8]; /*!< Interrupt Set Enable Register */

uint32_t RESERVED0[24];

__IO uint32_t ICER[8];

/*!< Interrupt Clear Enable Register */

uint32_t RSERVED1[24];

__IO uint32_t ISPR[8];

/*!< Interrupt Set Pending Register */

uint32_t RESERVED2[24];

__IO uint32_t ICPR[8];

/*!< Interrupt Clear Pending Register */

uint32_t RESERVED3[24];

__IO uint32_t IABR[8];

/*!< Interrupt Active bit Register */

uint32_t RESERVED4[56];

__IO uint8_t IP[240];

/*!< Interrupt Priority Register, 8Bit wide */

uint32_t RESERVED5[644];

__O uint32_t STIR;

/*!< Software Trigger Interrupt Register */

} NVIC_Type;CKS32F4xx系列的中断在这些寄存器控制下有序执行,只有了解这些中断寄存器后,才能方便的使用CKS32F4xx系列中断功能。下面重点介绍这几个寄存器:

ISER[8]:ISER 全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。上面说了CM4内核支持256个中断,这里用8个32位寄存器来控制,每个位控制一个中断。但是CKS32F4xx系列的可屏蔽中断最多只有82个,所以对我们来说,有用的就是三个(ISER[0~2]),ISER[0]的bit 0~31分别对应中断0~31;ISER[1]的bit 0~31对应中断32~63;ISER[2]的bit 0~17对应中断64~81,共82个中断。你要使能某个中断,必须设置相应的ISER位为 1,使该中断被使能,另外还要配合中断分组、屏蔽、IO口映射等设置才算是一个完整的中断设置。具体每一位对应哪个中断,请参考CKS32f4xx.h。

ICER[8]:全称是:Interrupt Clear-Enable Registers,是一个中断除能寄存器组。该寄存器组与 ISER 的作用恰好相反,是用来清除某个中断的使能的。其对应位的功能,也和 ICER 一样。这里要专门设置一个 ICER 来清除中断位,而不是向 ISER 写 0 来清除,是因为 NVIC 的这些寄存器都是写 1 有效的,写 0 是无效的。

ISPR[8]:全称是:Interrupt Set-Pending Registers,是一个中断挂起控制寄存器组。每个位对应的中断和ISER是一样的。通过置1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写0是无效的。

ICPR[8]:全称是:Interrupt Clear-Pending Registers,是一个中断解挂控制寄存器组。其作用与ISPR相反,对应位也和 ISER是一样的。通过设置1,可以将挂起的中断接挂。写 0 无效。

IABR[8]:全称是:Interrupt Active Bit Registers,是一个中断激活标志位寄存器组。对应位所代表的中断和ISER一样,如果为 1,则表示该位所对应的中断正在被执行。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。

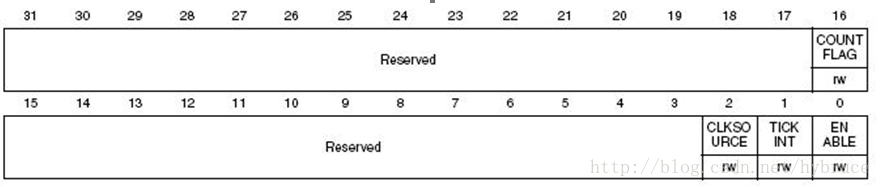

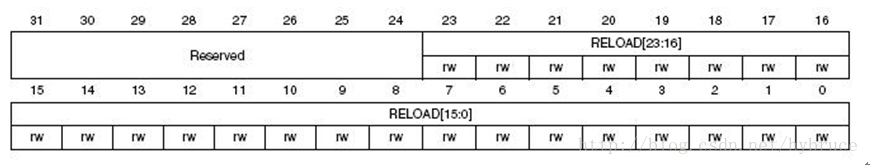

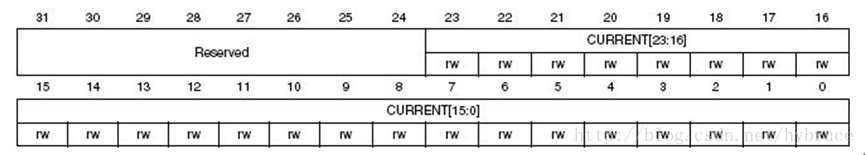

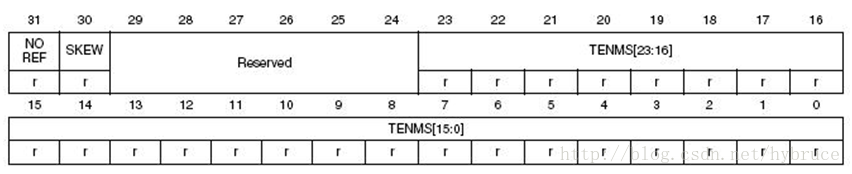

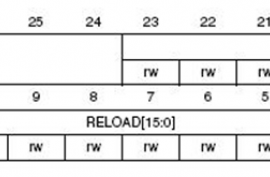

IP[240]:全称是:Interrupt Priority Registers,是一个中断优先级控制的寄存器组。CKS32F4的中断分组与这个寄存器组密切相关。IP寄存器组由240个8bit的寄存器组成,每个可屏蔽中断占用8bit,这样总共可以表示240个可屏蔽中断。而CKS32F4只用到了其中的82个。IP[81]~IP[0]分别对应中断 81~0。而每个可屏蔽中断占用的 8bit 并没有全部使用,而是只用了高4位。这4位,又分为抢占优先级和响应优先级。抢占优先级在前,响应优先级在后。而这两个优先级各占几个位又要根据 SCB->AIRCR 中的中断分组设置来决定。

NVIC中断分组

这里简单介绍一下 CKS32F4 的中断分组:CKS32F4将中断分为5个组,组0~4。该分组的设置是由 SCB->AIRCR 寄存器的 bit10~8 来定义的。具体的分配关系如下:

通过这个表,我们就可以清楚的看到组0~4对应的配置关系,例如组设置为3,那么此时所有的82个中断,每个中断的中断优先寄存器的高四位中的最高3位是抢占优先级,低1位是响应优先级。每个中断,你可以设置抢占优先级为0~7,响应优先级为1或0。抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

这里需要注意两点:

第一,如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行;

第二,高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。

结合实例说明一下:假定设置中断优先级组为2,然后设置中断3(RTC_WKUP中断)的抢占优先级为2,响应优先级为1。中断6(外部中断0)的抢占优先级为3,响应优先级为0。中断7(外部中断1)的抢占优先级为2,响应优先级为0。那么这3个中断的优先级顺序为:中断7>中断3>中断6。其中中断3和中断7都可以打断中断6的中断。而中断7和中断3却不可以相互打断!

软件实现

通过以上介绍,我们熟悉了CKS32F4中断设置的大致过程。接下来我们介绍如何使用库函数实现以上中断分组设置以及中断优先级管理,使得我们以后的中断设置简单化。NVIC中断管理函数主要在misc.c文件里面。

首先要讲解的是中断优先级分组函数NVIC_PriorityGroupConfig,其函数申明如下:

void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup);

这个函数的作用是对中断的优先级进行分组,这个函数在系统中只能被调用一次,一旦分组确定就最好不要更改。这个函数我们可以找到其实现:

void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)

{

assert_param(IS_NVIC_PRIORITY_GROUP(NVIC_PriorityGroup));

SCB->AIRCR = AIRCR_VECTKEY_MASK | NVIC_PriorityGroup;

}从函数体可以看出,这个函数唯一目的就是通过设置SCB->AIRCR寄存器来设置中断优先级分组,查看其定义为:

#define IS_NVIC_PRIORITY_GROUP(GROUP) (((GROUP) == NVIC_PriorityGroup_0) || ((GROUP) == NVIC_PriorityGroup_1) || \ ((GROUP) == NVIC_PriorityGroup_2) || \ ((GROUP) == NVIC_PriorityGroup_3) || \ ((GROUP) == NVIC_PriorityGroup_4))

可以看到这个定义对应上表中的分组范围0-4。如果我们需要设置系统的中断优先级分组值为2,那么方法是:NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2);这样就确定了一共为“2位抢占优先级,2位响应优先级”。设置好了系统中断分组,接下来设置中断的抢占优先级和响应优先级,这里需要用到一个重要的函数为中断初始化函数NVIC_Init,其函数声明为:voidNVIC_Init(NVIC_InitTypeDef*NVIC_InitStruct),其中NVIC_InitTypeDef是一个结构体,我们可以看看结构体的成员变量:

typedef struct

{

uint8_t NVIC_IRQChannel;

uint8_t NVIC_IRQChannelPreemptionPriority;

uint8_t NVIC_IRQChannelSubPriority;

FunctionalState NVIC_IRQChannelCmd;

} NVIC_InitTypeDef;NVIC_InitTypeDef结构体中间有四个成员变量,这四个成员变量的作用是:

NVIC_IRQChannel:

定义初始化的是哪个中断,这个我们可以在CKS32f4xx.h中定义的枚举类型IRQn的成员变量中可以找到每个中断对应的名字。例如串口1对应USART1_IRQn。

NVIC_IRQChannelPreemptionPriority:

定义这个中断的抢占优先级别;

NVIC_IRQChannelSubPriority:

定义这个中断的响应优先级别。

NVIC_IRQChannelCmd:

该中断通道是否使能。比如我们要使能串口1的中断,同时设置抢占优先级为1,响应优先级位2,初始化的方法是:

NVIC_InitTypeDef NVIC_InitStructure; NVIC_InitStructure.NVIC_IRQChannel = USART1_IRQn;//>>串口 1 中断 NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=1 ;//>> 抢占优先级为 1 NVIC_InitStructure.NVIC_IRQChannelSubPriority = 2;//>> 响应优先级位 2 NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //>>IRQ 通道使能 NVIC_Init(&NVIC_InitStructure);

这里我们讲解了中断的分组的概念以及设定优先级值的方法,至于每种优先级还有一些关于清除中断,查看中断状态,这在后面课堂中我们讲解每个中断的时候会详细讲解到。

课程总结

中断优先级设置的步骤:

1.系统初始化的时候设置中断分组:

确定组号,也就是确定抢占优先级和响应优先级的分配位数。调用函数为NVIC_PriorityGroupConfig();

2.设置所用到的中断的中断优先级别:

对每个中断调用函数NVIC_Init();确定具体的抢占优先级和响应优先级,并使能通道。

来源:中科芯MCU

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。