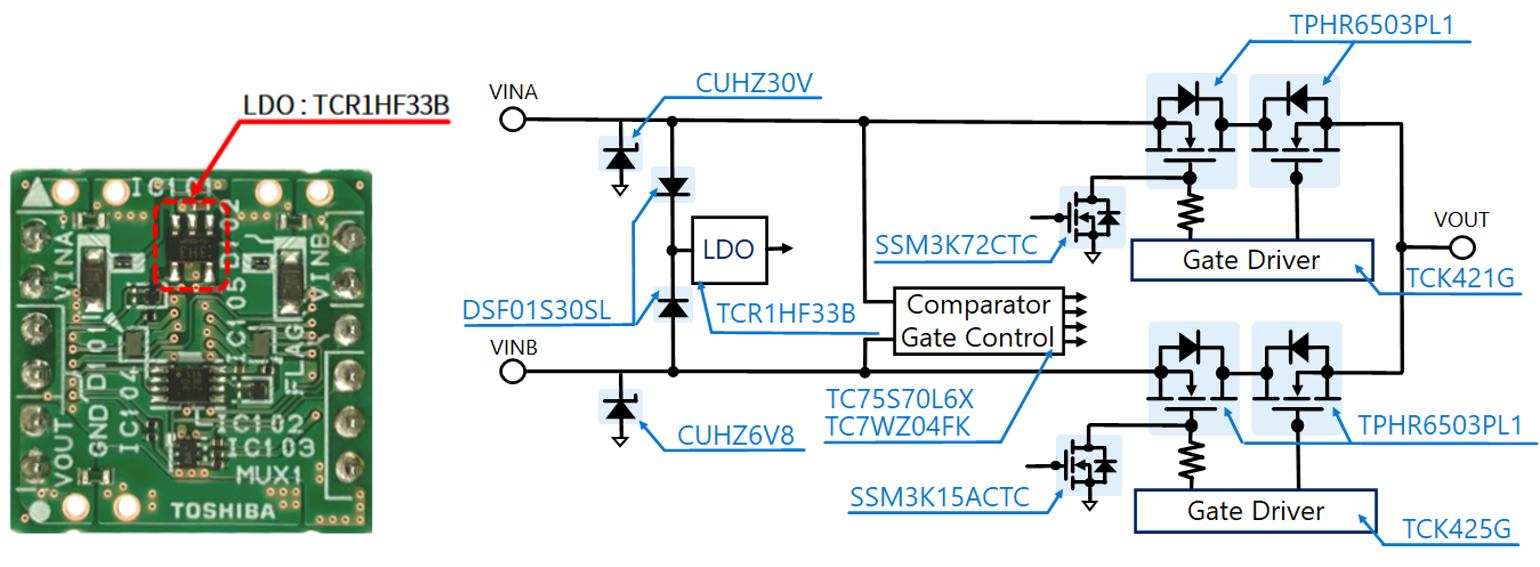

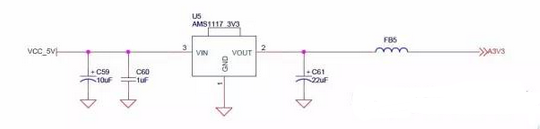

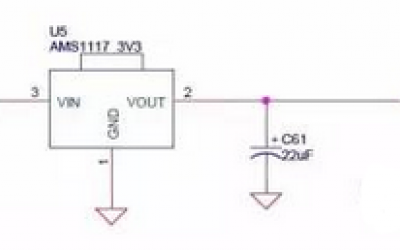

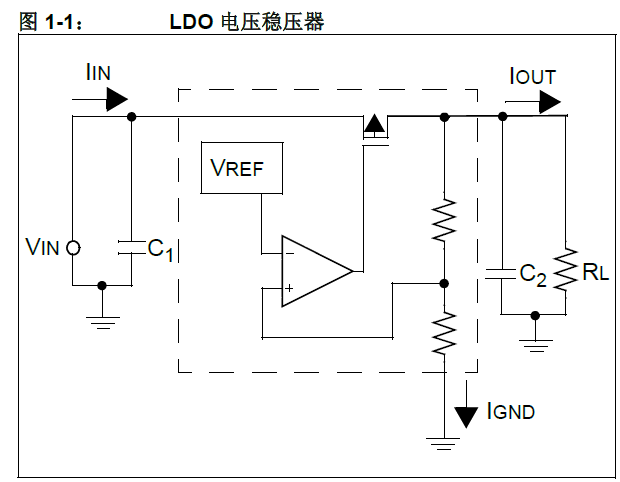

技巧一:使用LDO稳压器,从5V电源向3.3V系统供电

标准三端线性稳压器的压差通常是 2.0-3.0V。要把 5V 可靠地转换为 3.3V,就不能使用它们。

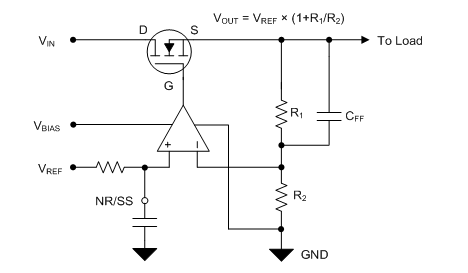

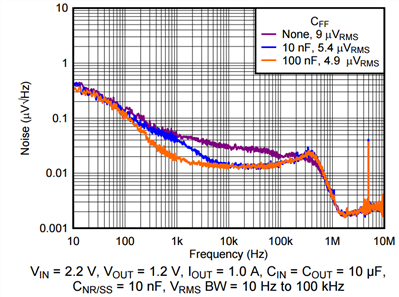

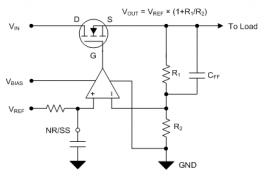

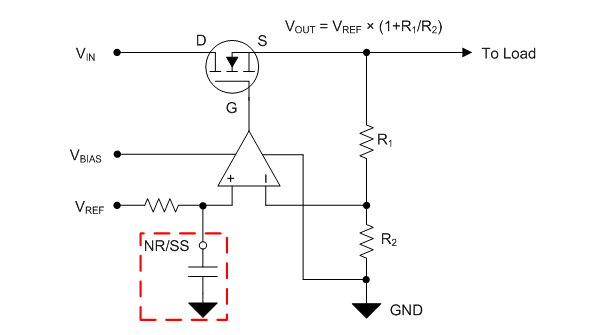

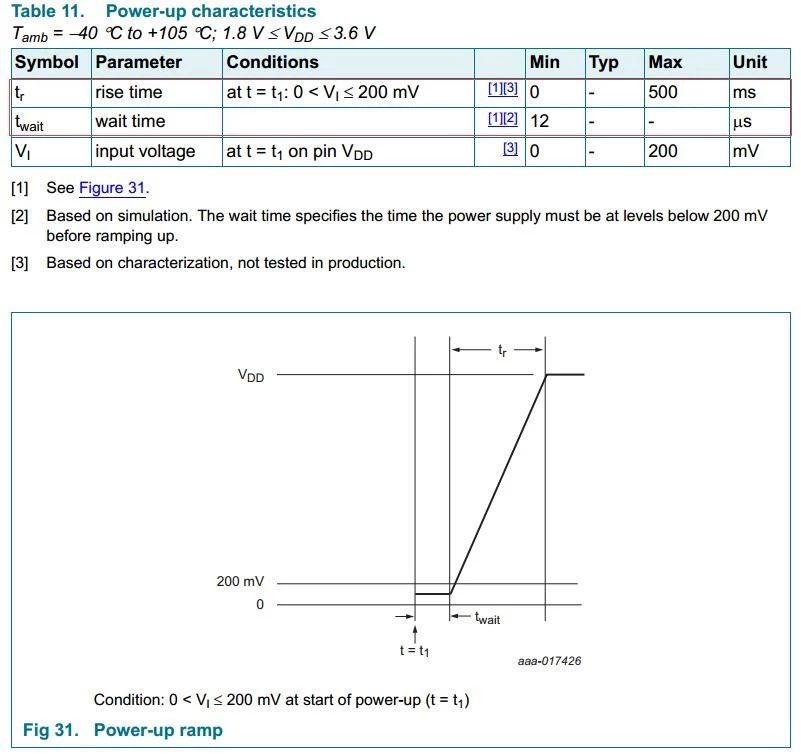

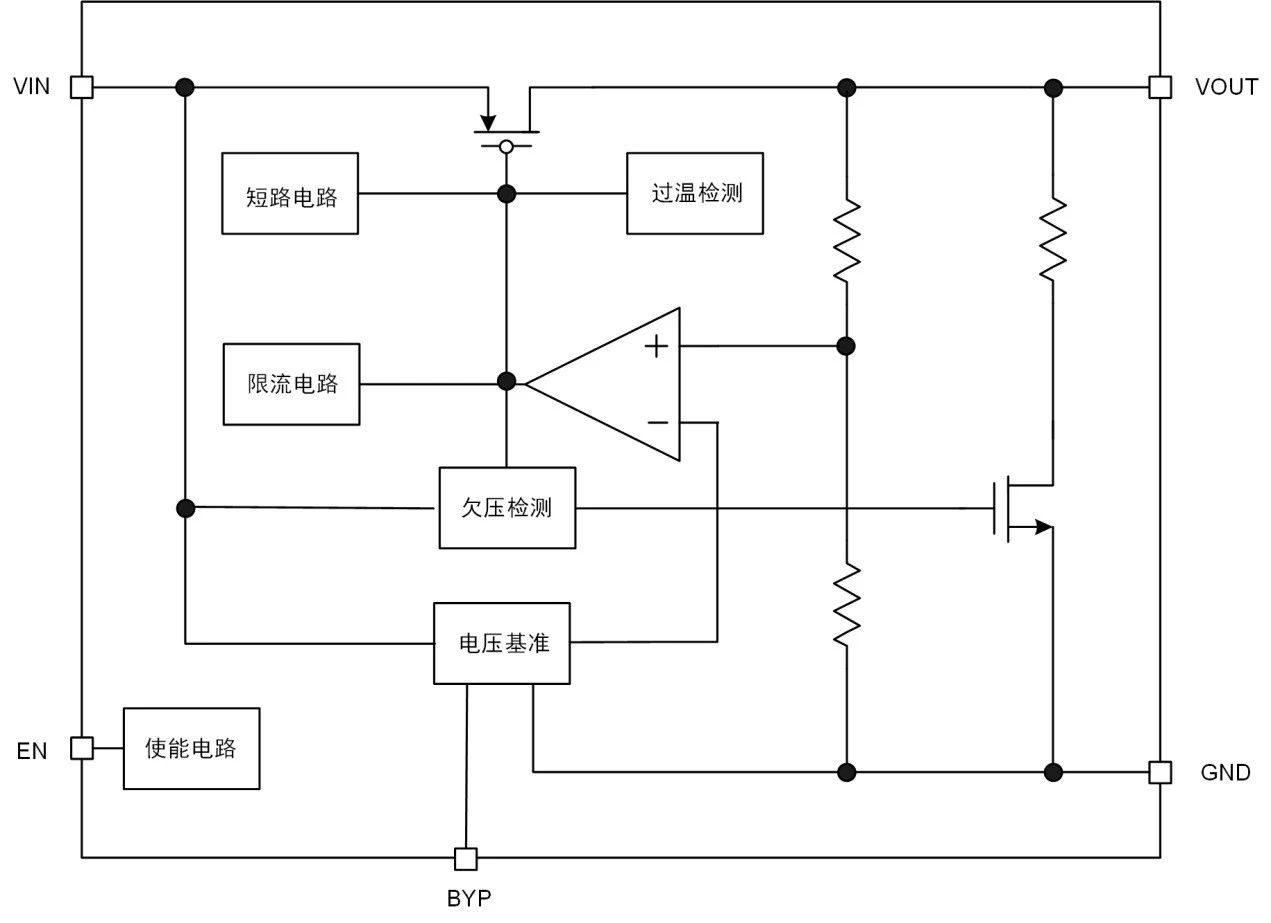

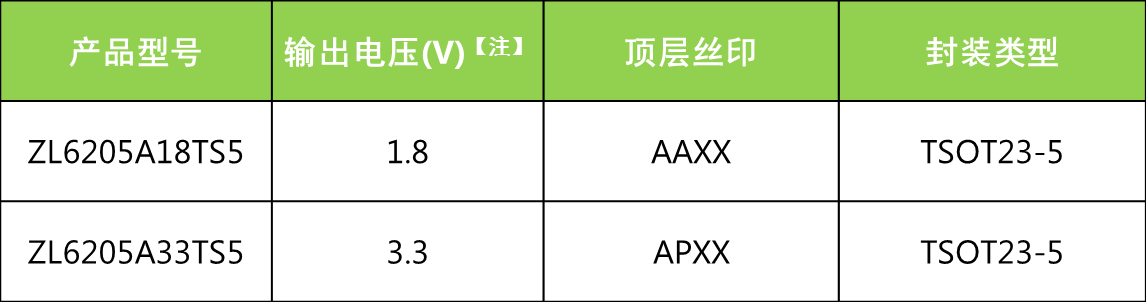

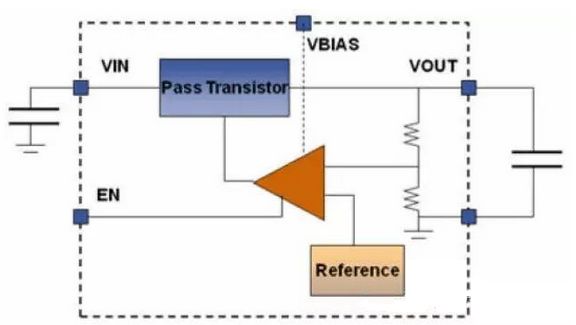

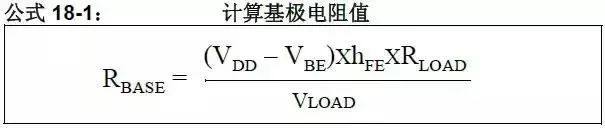

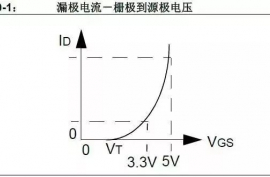

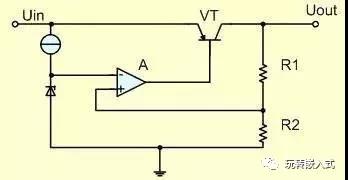

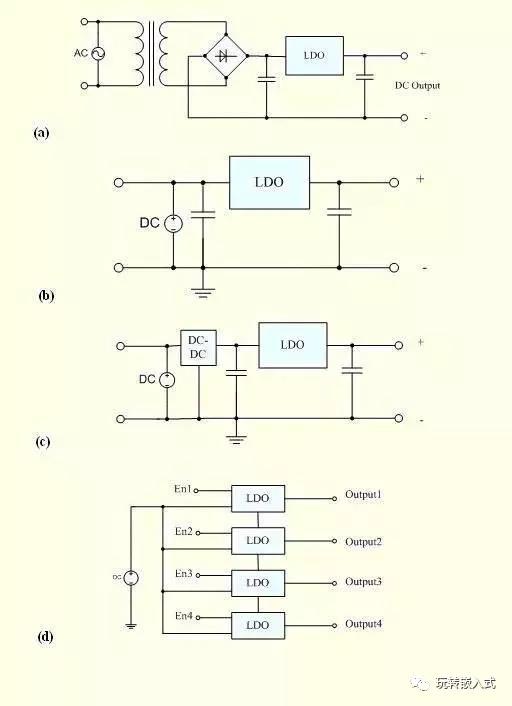

压差为几百个毫伏的低压降 (Low Dropout, LDO)稳压器,是此类应用的理想选择。图 1-1 是基本LDO 系统的框图,标注了相应的电流。从图中可以看出, LDO 由四个主要部分组成:

1. 导通晶体管

2. 带隙参考源

3. 运算放大器

4. 反馈电阻分压器

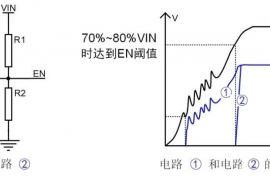

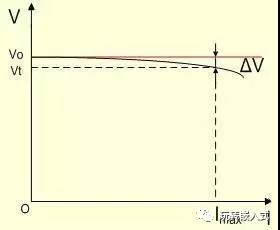

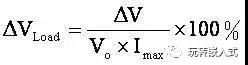

在选择 LDO 时,重要的是要知道如何区分各种LDO。器件的静态电流、封装大小和型号是重要的器件参数。根据具体应用来确定各种参数,将会得到最优的设计。

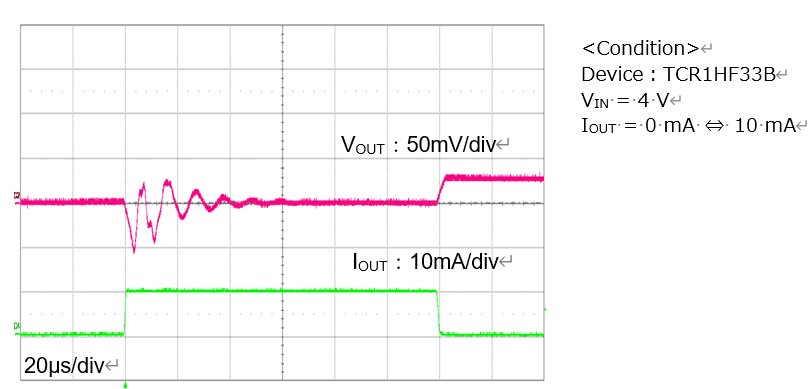

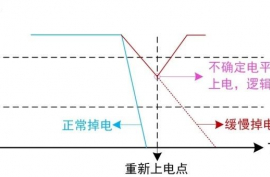

LDO的静态电流IQ是器件空载工作时器件的接地电流 IGND。IGND 是 LDO 用来进行稳压的电流。当IOUT>>IQ 时, LDO 的效率可用输出电压除以输入电压来近似地得到。然而,轻载时,必须将 IQ 计入效率计算中。

具有较低 IQ 的 LDO 其轻载效率较高。轻载效率的提高对于 LDO 性能有负面影响。静态电流较高的 LDO 对于线路和负载的突然变化有更快的响应。

技巧二:采用齐纳二极管的低成本供电系统

这里详细说明了一个采用齐纳二极管的低成本稳压器方案。

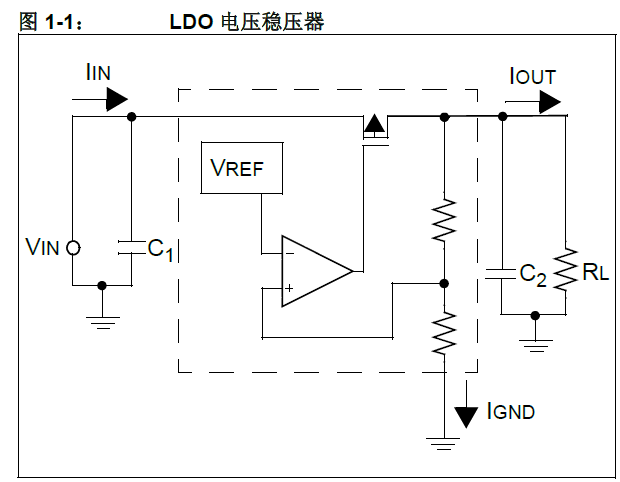

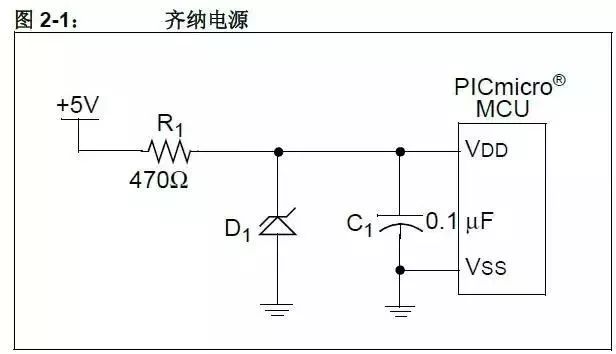

可以用齐纳二极管和电阻做成简单的低成本 3.3V稳压器,如图 2-1 所示。在很多应用中,该电路可以替代 LDO 稳压器并具成本效益。但是,这种稳压器对负载敏感的程度要高于 LDO 稳压器。

另外,它的能效较低,因为 R1 和 D1 始终有功耗。R1 限制流入D1 和 PICmicro® MCU的电流,从而使VDD 保持在允许范围内。由于流经齐纳二极管的电流变化时,二极管的反向电压也将发生改变,所以需要仔细考虑 R1 的值。

R1 的选择依据是:在最大负载时——通常是在PICmicro MCU 运行且驱动其输出为高电平时——R1上的电压降要足够低从而使PICmicro MCU有足以维持工作所需的电压。同时,在最小负载时——通常是 PICmicro MCU 复位时——VDD 不超过齐纳二极管的额定功率,也不超过 PICmicro MCU的最大 VDD。

技巧三:采用3个整流二极管的更低成本供电系统

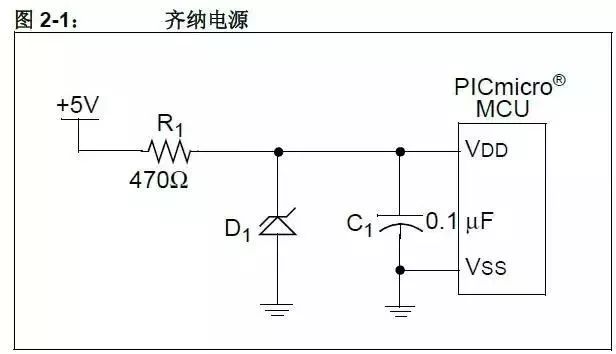

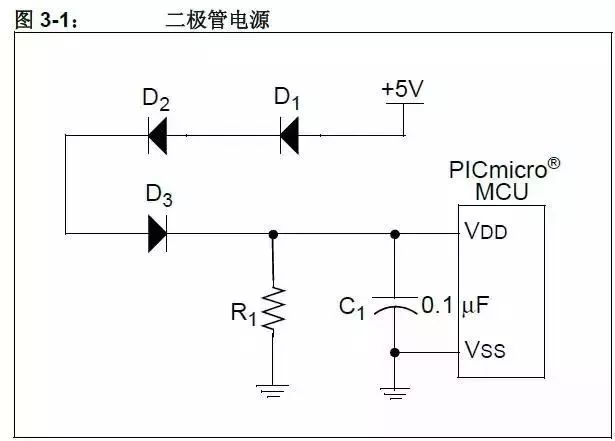

图 3-1 详细说明了一个采用 3 个整流二极管的更低成本稳压器方案。

我们也可以把几个常规开关二极管串联起来,用其正向压降来降低进入的 PICmicro MCU 的电压。这甚至比齐纳二极管稳压器的成本还要低。这种设计的电流消耗通常要比使用齐纳二极管的电路低。

所需二极管的数量根据所选用二极管的正向电压而变化。二极管 D1-D3 的电压降是流经这些二极管的电流的函数。连接 R1 是为了避免在负载最小时——通常是 PICmicro MCU 处于复位或休眠状态时——PICmicro MCU VDD 引脚上的电压超过PICmicro MCU 的最大 VDD 值。

根据其他连接至VDD 的电路,可以提高R1 的阻值,甚至也可能完全不需要 R1。二极管 D1-D3 的选择依据是:在最大负载时——通常是 PICmicro MCU 运行且驱动其输出为高电平时——D1-D3 上的电压降要足够低从而能够满足 PICmicro MCU 的最低 VDD 要求。

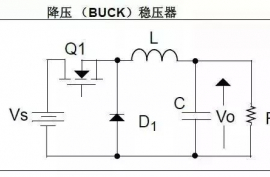

技巧四:使用开关稳压器,从5V电源向3.3V系统供电

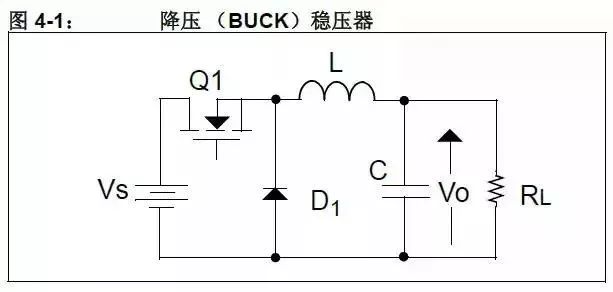

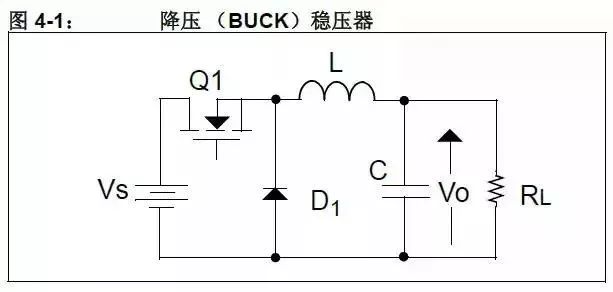

如图 4-1 所示,降压开关稳压器是一种基于电感的转换器,用来把输入电压源降低至幅值较低的输出电压。输出稳压是通过控制 MOSFET Q1 的导通(ON)时间来实现的。

由于 MOSFET 要么处于低阻状态,要么处于高阻状态(分别为 ON 和OFF),因此高输入源电压能够高效率地转换成较低的输出电压。

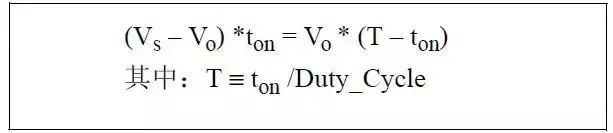

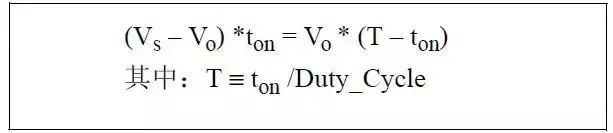

当 Q1 在这两种状态期间时,通过平衡电感的电压- 时间,可以建立输入和输出电压之间的关系。

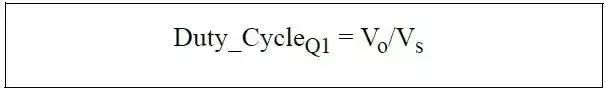

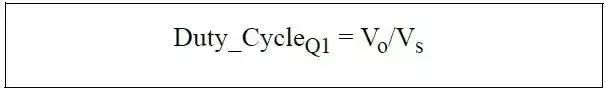

对于 MOSFET Q1,有下式:

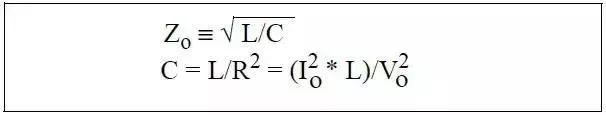

在选择电感的值时,使电感的最大峰 - 峰纹波电流等于最大负载电流的百分之十的电感值,是个很好的初始选择。

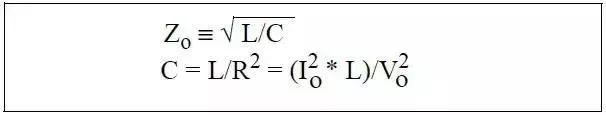

在选择输出电容值时,好的初值是:使 LC 滤波器特性阻抗等于负载电阻。这样在满载工作期间如果突然卸掉负载,电压过冲能处于可接受范围之内。

在选择二极管 D1 时,应选择额定电流足够大的元件,使之能够承受脉冲周期 (IL)放电期间的电感电流。

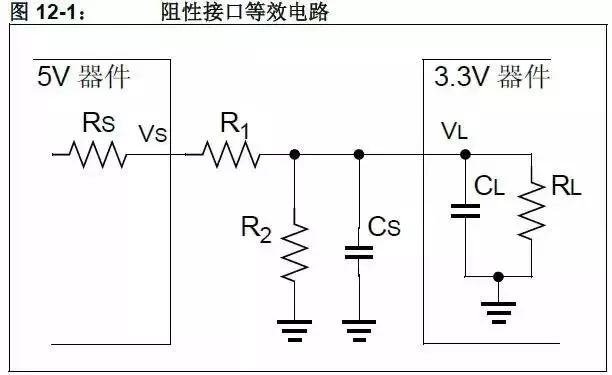

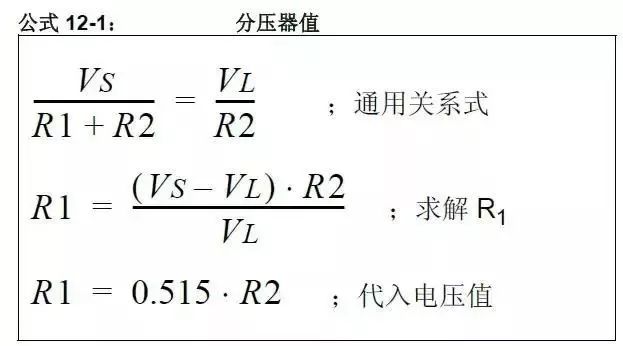

数字连接:在连接两个工作电压不同的器件时,必须要知道其各自的输出、输入阈值。知道阈值之后,可根据应用的其他需求选择器件的连接方法。

表 4-1 是本文档所使用的输出、输入阈值。在设计连接时,请务必参考制造商的数据手册以获得实际的阈值电平。

技巧五:3.3V →5V直接连接

将 3.3V 输出连接到 5V 输入最简单、最理想的方法是直接连接。直接连接需要满足以下 2 点要求:

• 3.3V输出的 VOH 大于 5V 输入的 VIH

• 3.3V输出的 VOL 小于 5V 输入的 VIL

能够使用这种方法的例子之一是将 3.3V LVCMOS输出连接到 5V TTL 输入。从表 4-1 中所给出的值可以清楚地看到上述要求均满足。

3.3V LVCMOS 的 VOH (3.0V)大于5V TTL 的VIH (2.0V)且3.3V LVCMOS 的 VOL (0.5V)小于 5V TTL 的VIL (0.8V)。

如果这两个要求得不到满足,连接两个部分时就需要额外的电路。可能的解决方案请参阅技巧 6、7、 8 和 13。

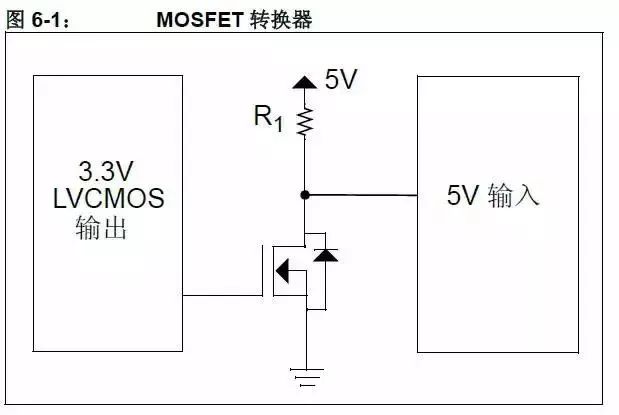

技巧六:3.3V→5V使用MOSFET转换器

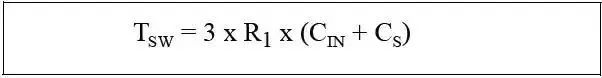

如果 5V 输入的 VIH 比 3.3V CMOS 器件的 VOH 要高,则驱动任何这样的 5V 输入就需要额外的电路。图 6-1 所示为低成本的双元件解决方案。

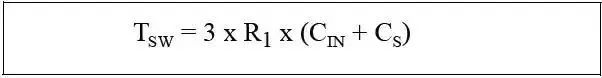

在选择 R1 的阻值时,需要考虑两个参数,即:输入的开关速度和 R1 上的电流消耗。

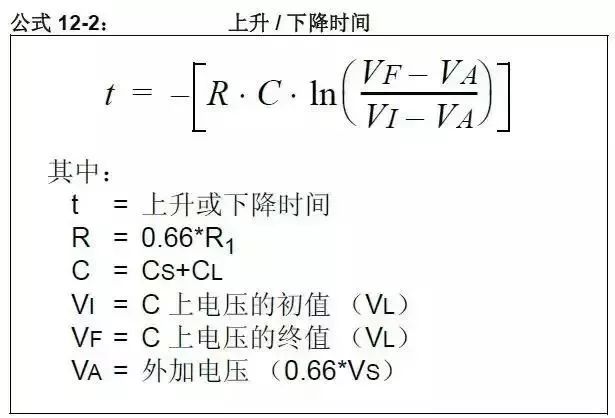

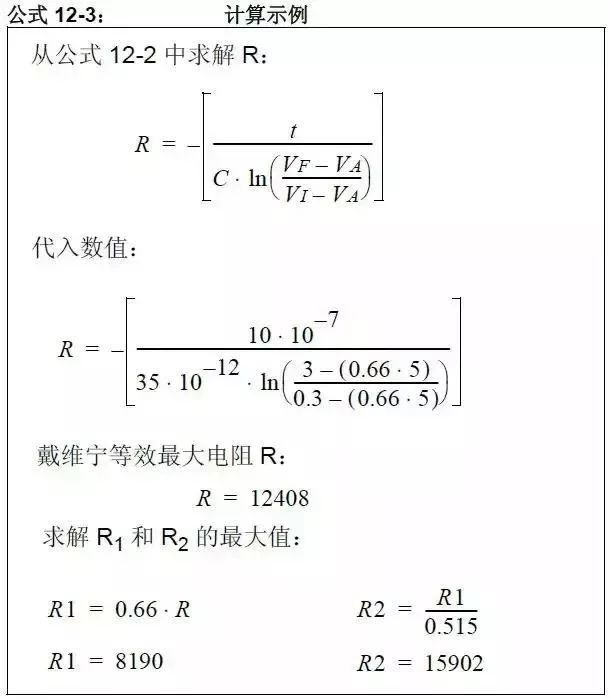

当把输入从 0切换到 1 时,需要计入因 R1 形成的 RC 时间常数而导致的输入上升时间、 5V 输入的输入容抗以及电路板上任何的杂散电容。输入开关速度可通过下式计算:

由于输入容抗和电路板上的杂散电容是固定的,提高输入开关速度的惟一途径是降低 R1 的阻值。而降低 R1 阻值以获取更短的开关时间,却是以增大5V 输入为低电平时的电流消耗为代价的。

通常,切换到 0 要比切换到 1 的速度快得多,因为 N 沟道 MOSFET 的导通电阻要远小于 R1。另外,在选择 N 沟道 FET 时,所选 FET 的VGS 应低于3.3V 输出的 VOH。

技巧七:3.3V→5V使用二极管补偿

表 7-1 列出了 5V CMOS 的输入电压阈值、 3.3VLVTTL 和 LVCMOS 的输出驱动电压。

从上表看出, 5V CMOS 输入的高、低输入电压阈值均比 3.3V 输出的阈值高约一伏。

因此,即使来自 3.3V 系统的输出能够被补偿,留给噪声或元件容差的余地也很小或者没有。我们需要的是能够补偿输出并加大高低输出电压差的电路。

输出电压规范确定后,就已经假定:高输出驱动的是输出和地之间的负载,而低输出驱动的是 3.3V和输出之间的负载。

如果高电压阈值的负载实际上是在输出和 3.3V 之间的话,那么输出电压实际上要高得多,因为拉高输出的机制是负载电阻,而不是输出三极管。

如果我们设计一个二极管补偿电路 (见图 7-1),二极管 D1 的正向电压 (典型值 0.7V)将会使输出低电压上升,在 5V CMOS 输入得到 1.1V 至1.2V 的低电压。它安全地处于 5V CMOS 输入的低输入电压阈值之下。

输出高电压由上拉电阻和连至3.3V 电源的二极管 D2 确定。这使得输出高电压大约比 3.3V 电源高 0.7V,也就是 4.0 到 4.1V,很安全地在 5V CMOS 输入阈值 (3.5V)之上。

注: 为了使电路工作正常,上拉电阻必须显著小于 5V CMOS 输入的输入电阻,从而避免由于输入端电阻分压器效应而导致的输出电压下降。上拉电阻还必须足够大,从而确保加载在 3.3V 输出上的电流在器件规范之内。

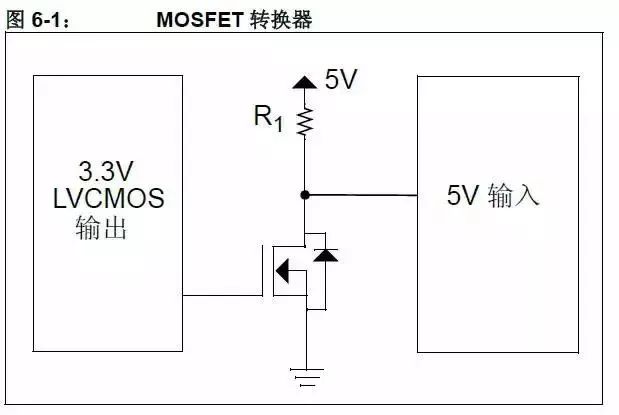

技巧八:3.3V→5V使用电压比较器

比较器的基本工作如下:

• 反相 (-)输入电压大于同相 (+)输入电压时,比较器输出切换到 Vss。

• 同相 (+)输入端电压大于反相 (-)输入电压时,比较器输出为高电平。

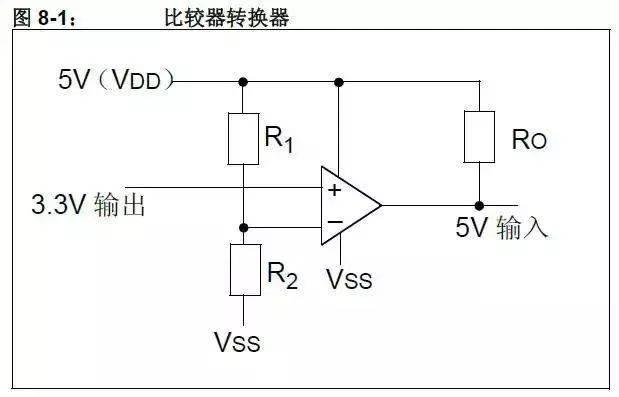

为了保持 3.3V 输出的极性, 3.3V 输出必须连接到比较器的同相输入端。比较器的反相输入连接到由 R1 和 R2 确定的参考电压处,如图 8-1 所示。

计算 R1 和 R2:R1 和 R2 之比取决于输入信号的逻辑电平。对于3.3V 输出,反相电压应该置于VOL 与VOH之间的中点电压。对于 LVCMOS 输出,中点电压为:

如果 R1 和 R2 的逻辑电平关系如下,

若 R2 取值为 1K,则 R1 为 1.8K。

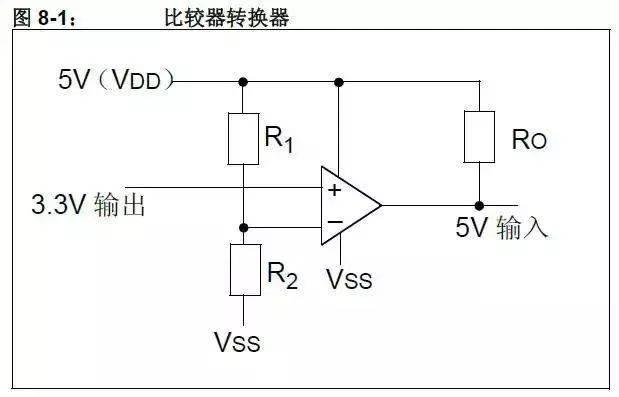

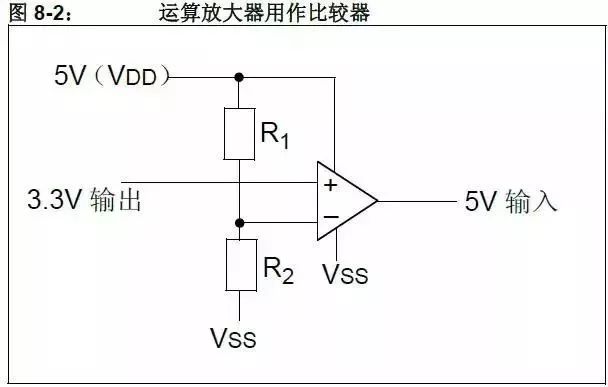

经过适当连接后的运算放大器可以用作比较器,以将 3.3V 输入信号转换为 5V 输出信号。这是利用了比较器的特性,即:根据 “反相”输入与 “同相”输入之间的压差幅值,比较器迫使输出为高(VDD)或低 (Vss)电平。

注: 要使运算放大器在 5V 供电下正常工作,输出必须具有轨到轨驱动能力。

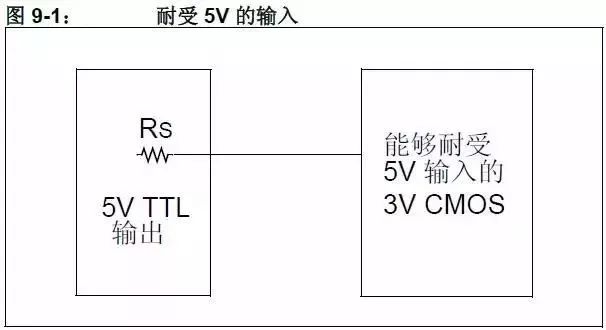

技巧九:5V→3.3V直接连接

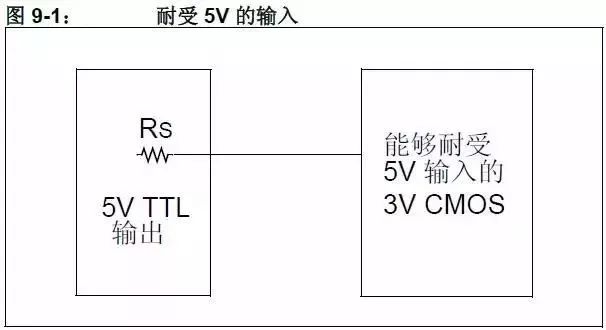

通常 5V 输出的 VOH 为 4.7 伏, VOL 为 0.4 伏;而通常 3.3V LVCMOS 输入的 VIH 为 0.7 x VDD, VIL为 0.2 x VDD。

当 5V 输出驱动为低时,不会有问题,因为 0.4 伏的输出小于 0.8 伏的输入阈值。

当 5V 输出为高时, 4.7 伏的 VOH 大于 2.1 伏 VIH,所以,我们可以直接把两个引脚相连,不会有冲突,前提是3.3V CMOS 输出能够耐受 5 伏电压。

如果 3.3V CMOS 输入不能耐受 5 伏电压,则将出现问题,因为超出了输入的最大电压规范。可能的解决方案请参见技巧 10-13。

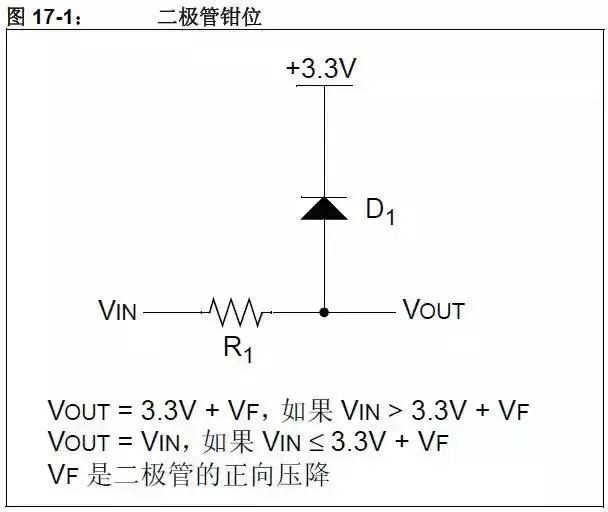

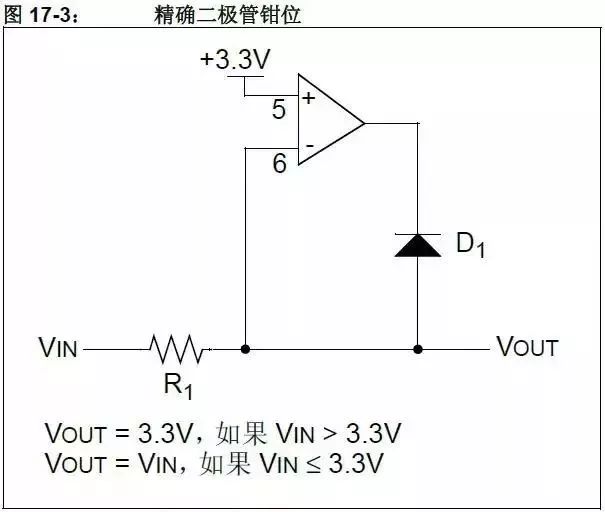

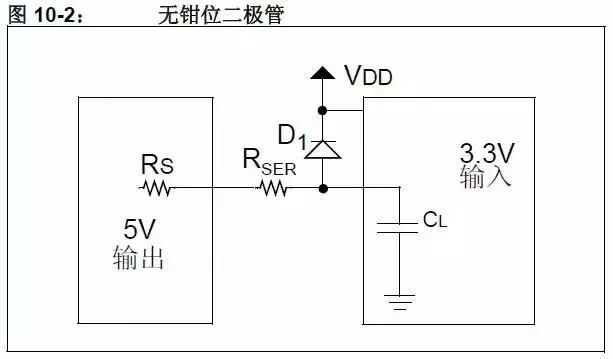

技巧十:5V→3.3V使用二极管钳位

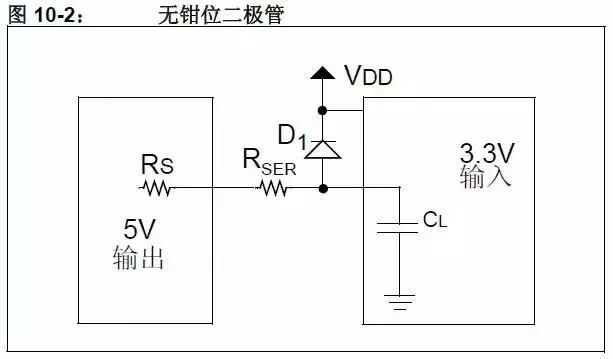

很多厂商都使用钳位二极管来保护器件的 I/O 引脚,防止引脚上的电压超过最大允许电压规范。钳位二极管使引脚上的电压不会低于 Vss 超过一个二极管压降,也不会高于 VDD 超过一个二极管压降。

要使用钳位二极管来保护输入,仍然要关注流经钳位二极管的电流。流经钳位二极管的电流应该始终比较小 (在微安数量级上)。

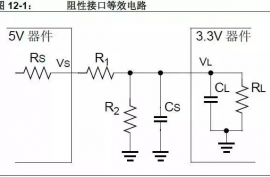

如果流经钳位二极管的电流过大,就存在部件闭锁的危险。由于5V 输出的源电阻通常在 10Ω 左右,因此仍需串联一个电阻,限制流经钳位二极管的电流,如图 10-1所示。

使用串联电阻的后果是降低了输入开关的速度,因为引脚 (CL)上构成了 RC 时间常数。

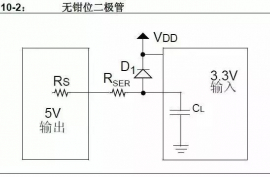

如果没有钳位二极管,可以在电流中添加一个外部二极管,如图 10-2 所示。

来源:EDA365电子论坛