ARM

全球物联网(IoT)应用热潮方兴未艾,然却已有不少MCU供应商铩羽而归,面对物联网应用整合控制/电源管理及无线连结的系统级解决方案需求,部分芯片供应商不是被迫待价而沽,就是面临被市场及客户边缘化危机,加上IP大厂安谋(ARM)版图正快速扩展到全球MCU市场,大幅降低进入门槛,并造成MCU市场杀价混战,全球MCU版图大洗牌已箭在弦上。

继恩智浦(NXP)购并飞思卡尔(Freescale),近期高通(Qualcomm)已经买下恩智浦,加上微芯(Microchip)从戴乐格(Dialog)手上抢亲艾特梅尔(Atmel),接着赛普拉斯(Cypress)购并博通(Broadcom)旗下物联网业务,以及瑞萨(Renesas)宣布合并英特矽尔(Intersil),凸显全球MCU大厂纷砸大钱布局物联网市场,全球MCU战火一触即发。

不过,全球物联网市场大饼仍不是很具体,加上众多竞争对手凭藉ARM的IP大刀,积极砍价抢攻市占率,对于过去擅长于少量、多样接单模式的中型MCU供应商,似乎愈来愈难找到生存空间,这亦让全球MCU产业除了排名前5大厂之外的其他MCU供应商,近期业绩表现呈现走滑趋势,并面临一波波的产业整并风暴。

芯片业者坦言,物联网市场商机其实并不容易吃到,除了各路人马全面加入战局外,ARM亦不断渗透全球MCU产业IP版图,甚至快速整合不少应用、产品及市场,让MCU供应商出现腹背受敌的危机,毕竟ARM透过全系列的高、中、低阶MCU IP,已大大降低全球MCU市场进入障碍。

由于各家芯片业者均可借由ARM IP及软件程式资源,开发自家高度客制化的MCU解决方案,对于老字号MCU供应商而言,过去拥有的客户基础及熟悉相关开发工具等竞争优势,已难抵挡新进业者积极杀价的进攻策略,迫使老字号MCU供应商成长动能疲软,尤其是中型MCU供应商受影响最明显,陷入被迫退出竞争行列的困境。

事实上,近期很多芯片业者为加速取得全球物联网市场参赛权,投入大笔资金进行购并,相较于过去MCU供应商提供客户包括芯片、软/韧体、公版及产品开发平台等资源,在物联网应用世代,MCU供应商更必须备齐控制/电源管理及无线连结等解决方案,不仅竞争压力大增,MCU供应商若不砸大钱,恐怕就只能退出这场竞赛。

在物联网市场快速萌芽,以及ARM IP掀起全面攻势的过程中,中型MCU供应商生存空间正持续遭到挤压,业者预期未来全球MCU产业版图将大幅变化,呈现大型、甚至超大型MCU供应商独占特定产品、应用及市场龙头情况。

由于这些大型MCU供应商多专注在领先的技术领域,让小型MCU供应商得以拿下一些利基及更少量、多样的产品市场商机,反而是夹在中间的中型MCU供应商,恐将面临一波波的产业淘汰赛。

MCU市场未来预测

据IC Insights预期,在经历了近几年的价格下滑之后,微控制器(MCU)的平均销售价格(ASP)预期将会回温,并再创销售额新高纪录。

市场研究机构IC Insights预期,IC产业的原始系统级晶片(SoC)产品──微控制器(microcontrollers,MCU)市场的年营收规模,将在未来五年稳定成长并达到新高纪录,尽管该市场整体出货量成长将趋缓。

IC Insights指出,MCU市场销售额在2015年几乎没有成长,幅度不到0.5%,但金额规模却达到了略高于159亿美元的新高纪录,主要是因为MCU出货量成长了15%,在去年达到了221亿颗的高峰(如下图)。强劲的出货量成长──由智慧卡应用与32位元产品带动──让MCU市场抵销了13%的平均销售价格(ASP)下滑;MCU的ASP在2015来到了0.72美元的历史新低。

价格下滑(特别是32位元产品),让MCU销售额成长率在过去四年中有三年都被拖累;但IC Insights指出,现在MCU的ASP预期将回稳,并在2015~2020年间可微幅成长,复合年平均成长率(CAGR)估计为1.6%;该数字在2010~2015年间为-7.7%。

虽然ASP终止下滑,MCU出货量的成长幅度则预测会在接下来五年比过去五年低;主要原因是智慧卡微控制器成长趋缓,还有因为物联网(IoT)应用对IC库存量的紧缩。ICInsights估计,MCU销售额在2016年将由2015年的159亿美元成长4%、来到近166亿美元。

MCU出货量在2016年则预期成长2%,达到224亿颗,而整体MCU的ASP则预测可在今年增加2%,来到0.74美元;在2015到2020年间,MCU销售额的CAGR估计为5.5%,并在2020年达到近209亿美元的规模。IC Insights表示,自1990年代中期以来,全球MCU销售额的CAGR约在2.9%。

MCU销售额到2020年将呈现上扬走势;预期在2016~2019年间,整体MCU市场营收成长率将逐渐增强(2019年成长率预测为9%),直到2020年缩减至4%的成长率;至于MCU出货量则预测在该期间以CAGR为3.9%的幅度成长。

IC Insights指出,MCU出货成长速度到2020年之间逐渐趋缓的原因,是智慧卡市场已迈入成熟阶段;该应用市场在近几年占据MCU出货量的近五成,占据MCU市场整体营收约15~16%。到2020年,智慧卡MCU预期将占据整体微控制器出货量的38%,而在整体销售额的占据幅度则缩减至12%。

ARM单片机是大多数新手选择的入门切入点,但由于知识的不足,在设计过程中新手们经常会遇到这样或那样的问题,ARM异常中断返回就是这样一种令人头疼的问题。在ARM的使用问题中异常中断返回是新手们较为苦恼的问题,本文就将对ARM异常中断的集中情况进行总结,并给出了一些解决方法。

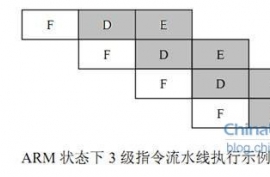

在正式介绍之前,要为大家补充一些较为重要的基础知识。首先R15(PC)总是指向“正在取指”的指令,而不是指向“正在执行”的指令或正在“译码”的指令。一般来说,人们习惯性约定将“正在执行的指令作为参考点”,称之为当前第一条指令,因此PC总是指向第三条指令。当ARM状态时,每条指令为4字节长,所以PC始终指向该指令地址加8字节的地址,即:PC值=当前程序执行位置+8;而ADS中的pc,是为了调试看着方便而修改过的,它指向的是正在执行的指令,即“真正pc-8”!

SWI和未定义指令异常中断的返回

指令地址:

A PC-8当前指令为SWI或未定义指令,此时发生中断.PC的值还没有更新。

A+4 PC-4中断时处理器将PC-4保存到LR。;r!

A+8 PC

返回时,从发生中断的指令A(PC-8)的下一条指令A+4(PC-4)处开始执行,所以直接把LR的值赋给PC就行了,具体指令为MOV PC,LR(PC=A+4=LR)。

白话解释:对于SWI和未定义指令发生异常时pc没有更新,根据ARM的三级流水线原理,pc没有更新,仍然等于(A+8);lr = pc – 4(这时处理器决定的,无法更改!)即A+4。

由于这类异常返回后应执行下一条指令(A+4),所以返回时,pc=lr即可。

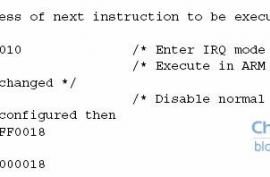

IRQ 和FIQ异常中断处理的返回指令地址对应于PC A,PC-8执行此指令完成后(!)查询IRQ及FIQ,如果有中断请求则产生中断。

A+4 PC-4

A+8 PC ;lr!

(此时PC的值已经更新,指向A+12.将当前PC-4,即A+8)。

保存到LR.返回时,要接着执行A+4(LR-4)处的指令,所以返回指令为:

SUBS PC,LR,#4(PC=A+4=LR-4)

白话解释:对于普中断和快中断异常,中断必须在一条指令执行完以后被检测到,如正在执行指令甲时发生了中断,不等指令甲执行完是不会处理该中断的,发生异常时pc已经更新(A+12); lr=pc– 4(这时处理器决定的,无法更改!)即A+8返回后,应执行被中断而没有执行的指令(上面的A+4),所以返回时,pc= lr-4。

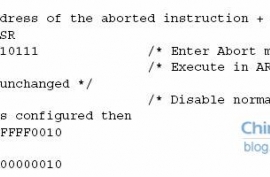

指令预取中止异常中断处理的返回

指令地址:

A PC-8 执行本指令时发生中断,A+4 PC-4处理器将A+4(PC-4)保存到:

LR. ;lr!A+8 PC

返回时,发生指令预取中止的指令A(PC-8)处重新执行,所以返回指令为SUBS PC,LR,#4(PC=A=LR-4)。

白话解释:对于预取指令中止异常发生预取指令异常时,是在执行时发生的异常,pc未更新,即pc=A+8;lr=pc – 4(这时处理器决定的,无法更改!)即A+4。

由于这类异常返回后应重新执行异常的那个指令(A),所以返回时,pc = lr-4。

数据访问中止异常中断处理的返回

指令地址:

A PC-8 本指令访问有问题的数据,产生中断时,PC的值已经更新。

A+4 PC-4 中断发生时PC=A+12,处理器将A+8(PC-4)保存到LR.。

A+8 PC ;lr!

返回时,要返回到A处继续执行,所以指令为SUBS PC,LR,#8.(PC=A=LR-8)

白话解释:对于数据访问中止异常时,是在执行时访问数据错误。

导致的异常,pc已经更新,即pc=A+12。

lr=pc–4(这时处理器决定的,无法更改!)即A+8。

由于这类异常返回后应重新执行异常的那个指令(A),所以返回时,pc=lr-8。

总结

引起PC更新的原因一种是数据中止,还有就是中断了。

中断必须是在一条指令执行完毕后才能被检测到,所以它中断的只是还未执行的那条。指令(pc-8),所以pc=lr – 4;

与中断相同,SWI和未定义指令异常也是返回到下一条指令(pc-4),只是他们在执行时,PC的值并没有更新,所以pc= lr。

预取指令中止异常,也没有发生pc更新,但它还得重新执行发生异常的那条指令,所以pc=lr–4。

数据访问中止异常,发生了pc更新,并且它也需要重新执行发生异常的那条指令,所以pc=lr–8。

通过以上的介绍,可以看到造成单片机中断返回的原因非常多,每种方法的应对方案都不尽相同。在ARM芯片调试过程中遇到中断返回问题的朋友不妨仔细阅读本文,相信会从中找到问题的解决方法。也可收藏本文以备不时之需,在遇到错误的时候进行查阅。

来源:网络(版权归原著作者所有)

1、一个ARM汇编语言源程序的基本结构:

AREA Init, CODE, READONLY

ENTRY

Start

LDR R0, =0x3FF5000

LDR R1, 0xFF

STR R1, [R0]

LDR R0, =0x3FF5008

LDR R1, 0x01

STR R1, [R0]

... ... ... ... ... ...

END

在 ARM( Thumb)汇编语言程序中,以程序段为单位组织代码。

段是相对独立的指令或数据序列,具有特定的名称。段可以分为代码段和数据段,代码段的内容为执行代码,数据段存放代码运行时需要用到的数据。一个汇编程序至少应该有一个代码段,当程序较长时,可以分割为多个代码段和数据段,多个段在程序编译链接时最终形成一个可执行的映象文件。

可执行映象文件通常由以下几部分构成:

— 一个或多个代码段,代码段的属性为只读。

— 零个或多个包含初始化数据的数据段,数据段的属性为可读写。

— 零个或多个不包含初始化数据的数据段,数据段的属性为可读写。

链接器根据系统默认或用户设定的规则,将各个段安排在存储器中的相应位置。因此源程序中段之间的相对位置与可执行的映象文件中段的相对位置一般不会相同。

在汇编语言程序中,用 AREA 伪指令定义一个段,并说明所定义段的相关属性,本例定义一个 名为 Init 的代码段,属性为只读。 ENTRY 伪指令标识程序的入口点,接下来为指令序列,程序的末尾为 END 伪指令,该伪指令告诉编译器源文件的结束,每一个汇编程序段都必须有一条 END 伪指令,指示代码段的结束。

2、 一个ARM汇编语言的子程序调用

AREA Init, CODE, READONLY

ENTRY

Start

LDR R0, =0x3FF5000

LDR R1, 0xFF

STR R1, [R0]

LDR R0, =0x3FF5008

LDR R1, 0x01

STR R1, [R0]

BL PRINT_TEXT

... ... ... ... ... ...

PRINT_TEXT

... ... ... ... ... ...

MOV PC,BL

... ... ... ... ... ...

END

在 ARM 汇编语言程序中,子程序的调用一般是通过 BL 指令来实现的。

在程序中,使用指令:

BL 子程序名

即可完成子程序的调用

该指令在执行时完成如下操作:将子程序的返回地址存放在连接寄存器 LR 中,同时将程序计器 PC 指向子程序的入口点,当子程序执行完毕需要返回调用处时,只需要将存放在 LR 中的返回地址重新拷贝给程序计数器 PC 即可。在调用子程序的同时,也可以完成参数的传递和从子程序返回运算的结果,通常可以使用寄存器 R0 ~ R3 完成。

在ARM处理器汇编语言程序设计里,有一些特殊的指令助记符。这些助记符与指令系统的助记符不同,没有相对应的操作码,通常称这些特殊的指令助记符为伪指令,它们所完成的操作称为伪操作。

伪指令在源程序中的作用是为完成汇编程序做各种准备工作的,这些伪指令仅在汇编过程中起作用,一旦汇编结束,伪指令的使命就完成了。在ARM处理器的汇编程序中,大体有如下几种伪指令:符号定义伪指令、数据定义伪指令、汇编控制伪指令、宏指令及其他伪指令。

伪操作符可以分为以下几类。

1)数据定义伪操作符

数据定义伪操作符主要包括LTORG、MAP、DCB、FIELD、SPACE、DCQ、DCW等,主要用于数据表定义、文字池定义、数据空间分配等。常用的有DCB/DCQ/DCW分配一段字节/双字/字内存单元,并且将它们初始化。

2)符号定义伪操作符

符号定义伪操作符包括GBLA、GBLL、GBLS、LCLA、CN、CP、DN、FN、RLIST、SETA等,用于定义ARM汇编程序的变量,对变量进行赋值,以及定义寄存器名称等。其中用于全局变量声明的GBLA、GBLL、GBLS和局部变量声明的LCAL、LCLL、LCLS伪指令较为常用。

3)报告伪操作符

报告伪操作符包括ASSERT、INFO、OPT等,主要用于汇编报告等。其中比较常用的有ASSERT,表示断言错误。

4)条件汇编伪操作符

条件汇编伪操作符包括IF、ELSE、ENDIF、WHIL、WEND、MACRO、MEND等,主要用于条件汇编、宏定义、重复汇编控制等操作。

5)杂项伪操作符

杂项伪操作符包括AREA、ALIGN、ENTRY、EQU、EXPORT、GLOBAL、IMPORT、CODE16、CODE32等。这些伪指令在汇编程序设计中较为常用,如段定义、入口点设置等伪指令。常用的伪指令主要有以下几条。

AREA:用来定义段;

ALIGN:用来设定边界对齐;

CODE16/CODE32:用来指定指令集;

ENTRY:指定程序入口;

END:汇编结束。

1、符号定义( Symbol Definition )伪指令

符号定义伪指令用于定义 ARM 汇编程序中的变量、对变量赋值以及定义寄存器的别名等操作。

常见的符号定义伪指令有如下几种:

— 用于定义全局变量的GBLA 、GBLL 和 GBLS

— 用于定义局部变量的 LCLA 、LCLL 和 LCLS

— 用于对变量赋值的 SETA 、SETL 、SETS

— 为通用寄存器列表定义名称的 RLIST

语法格式:

GBLA(GBLL或GBLS)全局变量名

GBLA、GBLL和GBLS伪指令用于定义一个 ARM 程序中的全局变量,并将其初始化。

其中:

GBLA 伪指令用于定义一个全局的数字变量,并初始化为 0;

GBLL 伪指令用于定义一个全局的逻辑变量,并初始化为 F;

GBLS 伪指令用于定义一个全局的字符串变量,并初始化为空;

由于以上三条伪指令用于定义全局变量,因此在整个程序范围内变量名必须唯一。

使用示例:

GBLA Test1 ;定义一个全局的数字变量,变量名为 Test1

Test1 SETA 0xaa ;将该变量赋值为 0xaa

GBLL Test2 ;定义一个全局的逻辑变量,变量名为 Test2

Test2 SETL {TRUE} ;将该变量赋值为真

GBLS Test3 ;定义一个全局的字符串变量,变量名为 Test3

Test3 SETS " Testing " ;将该变量赋值为 " Testing "

语法格式:

LCLA ( LCLL 或 LCLS ) 局部变量名

LCLA 、 LCLL 和 LCLS 伪指令用于定义一个 ARM 程序中的局部变量,并将其初始化。

其中:

LCLA 伪指令用于定义一个局部的数字变量,并初始化为0;

LCLL 伪指令用于定义一个局部的逻辑变量,并初始化为F(假);

LCLS 伪指令用于定义一个局部的字符串变量,并初始化为空;

以上三条伪指令用于声明局部变量,在其作用范围内变量名必须唯一。

语法格式:

变量名 SETA ( SETL 或 SETS ) 表达式:

伪指令 SETA 、 SETL 、 SETS 用于给一个已经定义的全局变量或局部变量赋值。

SETA 伪指令用于给一个数学变量赋值;

SETL 伪指令用于给一个逻辑变量赋值;

SETS 伪指令用于给一个字符串变量赋值;

语法格式:

名称 RLIST { 寄存器列表 }

RLIST 伪指令可用于对一个通用寄存器列表定义名称,使用该伪指令定义的名称可在 ARM 指令 LDM/STM 中使用。

在 LDM/STM 指令中,列表中的寄存器访问次序为根据寄存器的编号由低到高,而与列表中的寄存器排列次序无关。

使用示例:

RegList RLIST {R0-R5,R8,R10};

将寄存器列表名称定义为 RegList,可在 ARM 指令 LDM/STM中通过该名称访问寄存器列表。

2、数据定义( Data Definition )伪指令

数据定义伪指令一般用于为特定的数据分配存储单元,同时可完成已分配存储单元的初始化。

常见的数据定义伪指令有如下几种:

— DCB用于分配一片连续的字节存储单元并用指定的数据初始化。

— DCW(DCWU)用于分配一片连续的半字存储单元并用指定的数据初始化。

— DCD(DCDU)用于分配一片连续的字存储单元并用指定的数据初始化。

— DCFD(DCFDU)用于为双精度的浮点数分配一片连续的字存储单元并用指定的数据初始化。

— DCFS(DCFSU)用于为单精度的浮点数分配一片连续的字存储单元并用指定的数据初始化。

— DCQ(DCQU)用于分配一片以 8 字节为单位的连续的存储单元并用指定的数据初始化。

— SPACE用于分配一片连续的存储单元

— MAP 用于定义一个结构化的内存表首地址

— FIELD 用于定义一个结构化的内存表的数据域

语法格式:

标号 DCB 表达式

DCB 伪指令用于分配一片连续的字节存储单元并用伪指令中指定的表达式初始化。其中,表达式可以为 0 ~ 255 的数字或字符串。 DCB 也可用 " = " 代替。

使用示例:

Str DCB " This is a test ! " ;分配一片连续的字节存储单元并初始化。

语法格式:

标号 DCW (或 DCWU ) 表达式

DCW (或 DCWU )伪指令用于分配一片连续的半字存储单元并用伪指令中指定的表达式初始化。

其中,表达式可以为程序标号或数字表达式。。

用 DCW 分配的字存储单元是半字对齐的,而用 DCWU 分配的字存储单元并不严格半字对齐。

使用示例:

DataTest DCW 1,2,3;分配一片连续的半字存储单元并初始化。

语法格式:

标号 DCD (或 DCDU ) 表达式

DCD(或 DCDU)伪指令用于分配一片连续的字存储单元并用伪指令中指定的表达式初始化。其中,表达式可以为程序标号或数字表达式。DCD 也可用"& "代替。

用 DCD 分配的字存储单元是字对齐的,而用 DCDU 分配的字存储单元并不严格字对齐。

使用示例:

DataTest DCD 4,5,6;分配一片连续的字存储单元并初始化。

语法格式:

标号 DCFD (或 DCFDU ) 表达式

DCFD (或 DCFDU )伪指令用于为双精度的浮点数分配一片连续的字存储单元并用伪指令中指定的表达式初始化。

每个双精度的浮点数占据两个字单元。用 DCFD 分配的字存储单元是字对齐的,而用 DCFDU 分配的字存储单元并不严格字对齐。

使用示例:

FDataTest DCFD 2E115,-5E7;分配一片连续的字存储单元并初始化为指定的双精度数。

语法格式:

标号 DCFS (或 DCFSU ) 表达式

DCFS (或 DCFSU )伪指令用于为单精度的浮点数分配一片连续的字存储单元并用伪指令中指定的表达式初始化。

每个单精度的浮点数占据一个字单元。 用 DCFS 分配的字存储单元是字对齐的,而用 DCFSU 分配的字存储单元并不严格字对齐。

使用示例:

FDataTest DCFS 2E5,-5E-7;分配一片连续的字存储单元并初始化为指定的单精度数。

语法格式:

标号 DCQ (或 DCQU ) 表达式

DCQ (或 DCQU )伪指令用于分配一片以 8 个字节为单位的连续存储区域并用伪指令中指定的表达式初始化。

用 DCQ 分配的存储单元是字对齐的,而用 DCQU 分配的存储单元并不严格字对齐。

使用示例:

DataTest DCQ 100 ;分配一片连续的存储单元并初始化为指定的值。

语法格式:

标号 SPACE 表达式 - K7 ]' L4 `) T4 @8 H

SPACE 伪指令用于分配一片连续的存储区域并初始化为 0 。其中,表达式为要分配的字节数。

SPACE 也可用"%"代替。

使用示例:

DataSpace SPACE 100;分配连续 100 字节的存储单元并初始化为 0 。

语法格式:

MAP 表达式 { ,基址寄存器 }

MAP 伪指令用于定义一个结构化的内存表的首地址。 MAP 也可用 " ^ " 代替。

表达式可以为程序中的标号或数学表达式,基址寄存器为可选项。

当基址寄存器选项不存在时,表达式的值即为内存表的首地址,当该选项存在时,内存表的首地址为表达式的值与基址寄存器的和。

MAP 伪指令通常与 FIELD 伪指令配合使用来定义结构化的内存表。

使用示例:

MAP 0x100 , R0 ;定义结构化内存表首地址的值为 0x100 + R0 。

语法格式:

标号 FIELD 表达式

FIELD 伪指令用于定义一个结构化内存表中的数据域。 FILED 也可用 " # " 代替。

表达式的值为当前数据域在内存表中所占的字节数。

FIELD 伪指令常与 MAP 伪指令配合使用来定义结构化的内存表。

MAP 伪指令定义内存表的首地址,FIELD 伪指令定义内存表中的各个数据域,并可以为每个数据域指定一个标号供其他的指令引用。

注意 MAP 和 FIELD 伪指令仅用于定义数据结构,并不实际分配存储单元。

使用示例:

MAP 0x100 ;定义结构化内存表首地址的值为 0x100 。

A FIELD 16 ;定义 A 的长度为 16 字节,位置为 0x100

B FIELD 32 ;定义 B 的长度为 32 字节,位置为 0x110

S FIELD 256 ;定义 S 的长度为 256 字节,位置为 0x130

3、汇编控制( Assembly Control )伪指令

汇编控制伪指令用于控制汇编程序的执行流程,常用的汇编控制伪指令包括以下几条:

— IF 、 ELSE 、 ENDIF

— WHILE 、 WEND

— MACRO 、 MEND

— MEXIT

语法格式:

IF 逻辑表达式

指令序列 1

ELSE

指令序列 2

ENDIF

IF 、 ELSE 、 ENDIF 伪指令能根据条件的成立与否决定是否执行某个指令序列。

当 IF 后面的逻辑表达式为真,则执行指令序列1,否则执行指令序列2。

其中,ELSE及指令序列 2 可以没有,此时,当IF后面的逻辑表达式为真,则执行指令序列1,否则继续执行后面的指令。

IF 、 ELSE 、 ENDIF 伪指令可以嵌套使用。

使用示例:

GBLL Test ;声明一个全局的逻辑变量,变量名为 Test……

IF Test = TRUE

指令序列 1

ELSE

指令序列 2

ENDIF

语法格式:

WHILE 逻辑表达式

指令序列

WEND

WHILE 、 WEND 伪指令能根据条件的成立与否决定是否循环执行某个指令序列。

当 WHILE 后面的逻辑表达式为真,则执行指令序列,该指令序列执行完毕后,再判断逻辑表达式的值,若为真则继续执行,一直到逻辑表达式的值为假。

WHILE 、 WEND 伪指令可以嵌套使用。

使用示例:

GBLA Counter ;声明一个全局的数学变量,变量名为 Counter

Counter SETA 3 ;由变量Counter 控制循环次数

WHILE Counter <

指令序列

WEND

语法格式:

$ 标号 宏名 $ 参数 1 , $ 参数 2 ,……

指令序列

MEND

MACRO 、 MEND 伪指令可以将一段代码定义为一个整体,称为宏指令,然后就可以在程序中通过宏指令多次调用该段代码。

其中, $ 标号在宏指令被展开时,标号会被替换为用户定义的符号, 宏指令可以使用一个或多个参数,当宏指令被展开时,这些参数被相应的值替换。

宏指令的使用方式和功能与子程序有些相似,子程序可以提供模块化的程序设计、节省存储空间并提高运行速度。

但在使用子程序结构时需要保护现场,从而增加了系统的开销,因此,在代码较短且需要传递的参数较多时,可以使用宏指令代替子程序。

包含在 MACRO 和 MEND 之间的指令序列称为宏定义体,在宏定义体的第一行应声明宏的原型(包含宏名、所需的参数),然后就可以在汇编程序中通过宏名来调用该指 令序列。在源程序被编译时,汇编器将宏调用展开,用宏定义中的指令序列代替程序中的宏调用,并将实际参数的值传递给宏定义中的形式参数。

MACRO 、 MEND 伪指令可以嵌套使用。

语法格式:

MEXIT:

MEXIT 用于从宏定义中跳转出去。

4、其他常用的伪指令

还有一些其他的伪指令,在汇编程序中经常会被使用,包括以下几条:

— AREA

— ALIGN

— CODE16 、 CODE32

— ENTRY

— END

— EQU

— EXPORT (或 GLOBAL )

— IMPORT

— EXTERN

— GET (或 INCLUDE )

— INCBIN

— RN

— ROUT

语法格式:

AREA 段名 属性 1 ,属性 2 ,……

AREA 伪指令用于定义一个代码段或数据段。其中,段名若以数字开头,则该段名需用 " | " 括起来,如 |1_test| 。

属性字段表示该代码段(或数据段)的相关属性,多个属性用逗号分隔。常用的属性如下:

— CODE 属性:用于定义代码段,默认为 READONLY 。

— DATA 属性:用于定义数据段,默认为 READWRITE 。

— READONLY 属性:指定本段为只读,代码段默认为 READONLY 。

— READWRITE 属性:指定本段为可读可写,数据段的默认属性为 READWRITE 。

— ALIGN 属性:使用方式为 ALIGN 表达式。在默认时, ELF (可执行连接文件)的代码段和数据段是按字对齐的,表达式的取值范围为 0 ~ 31 ,相应的对齐方式为 2 表达式次方。

— COMMON 属性:该属性定义一个通用的段,不包含任何的用户代码和数据。各源文件中同名的 COMMON 段共享同一段存储单元。

一个汇编语言程序至少要包含一个段,当程序太长时,也可以将程序分为多个代码段和数据段。

使用示例:

AREA Init , CODE , READONLY

该伪指令定义了一个代码段,段名为 Init ,属性为只读

语法格式:

ALIGN { 表达式 { ,偏移量 }}

ALIGN 伪指令可通过添加填充字节的方式,使当前位置满足一定的对其方式 。其中,表达式的值用于指定对齐方式,可能的取值为 2 的幂,如 1 、 2 、 4 、 8 、 16 等。 若未指定表达式,则将当前位置对齐到下一个字的位置。偏移量也为一个数字表达式,若使用该字段,则当前位置的对齐方式为: 2 的表达式次幂+偏移量。

使用示例:

AREA Init,CODE,READONLY,ALIEN=3;指定后面的指令为 8 字节对齐。

指令序列

END

语法格式:

CODE16(或 CODE32)

CODE16 伪指令通知编译器,其后的指令序列为 16 位的 Thumb 指令。

CODE32 伪指令通知编译器,其后的指令序列为 32 位的 ARM 指令。

若在汇编源程序中同时包含 ARM 指令和 Thumb 指令时,可用 CODE16 伪指令通知编译器其后的指令序列为 16 位的 Thumb 指令, CODE32 伪指令通知编译器其后的 指令序列为 32 位的 ARM 指令。因此,在使用 ARM 指令和 Thumb 指令混合编程的代码里,可用这两条伪指令进行切换,但注意他们只通知编译器其后指令的类型,并不能对处理器进行状态的切换。

使用示例:

AREA Init , CODE , READONLY

……

CODE32 ;通知编译器其后的指令为 32 位的 ARM 指令

LDR R0 ,= NEXT + 1 ;将跳转地址放入寄存器 R0

BX R0;程序跳转到新的位置执行,并将处理器切换到 Thumb 工作状态

……

CODE16;通知编译器其后的指令为 16 位的 Thumb 指令

NEXT LDR R3,=0x3FF

……

END ;程序结束

语法格式:

ENTRY

ENTRY 伪指令用于指定汇编程序的入口点。在一个完整的汇编程序中至少要有一个 ENTRY (也可以有多个,当有多个 ENTRY 时,程序的真正入口点由链接器指定),但 在一个源文件里最多只能有一个 ENTRY (可以没有)。

使用示例:

AREA Init , CODE , READONLY

ENTRY ;指定应用程序的入口点

……

语法格式:

END

END 伪指令用于通知编译器已经到了源程序的结尾。

使用示例:

AREA Init , CODE , READONLY

……

END ;指定应用程序的结尾

语法格式:

名称 EQU 表达式 { ,类型 }

EQU 伪指令用于为程序中的常量、标号等定义一个等效的字符名称,类似于 C 语言中的#define 。

其中 EQU 可用" * "代替。

名称为 EQU 伪指令定义的字符名称,当表达式为 32 位的常量时,可以指定表达式的数据类型,可以有以下三种类型:

CODE16 、 CODE32 和 DATA

使用示例:

Test EQU 50 ;定义标号 Test 的值为 50

Addr EQU 0x55 , CODE32 ;定义 Addr 的值为 0x55 ,且该处为 32 位的 ARM 指令。

语法格式:

EXPORT 标号 {[WEAK]}

EXPORT 伪指令用于在程序中声明一个全局的标号,该标号可在其他的文件中引用。 EXPORT可用 GLOBAL 代替。标号在程序中区分大小写, [WEAK] 选项声明其他的同 名标号优先于该标号被引用。

使用示例:

AREA Init , CODE , READONLY

EXPORT Stest ;声明一个可全局引用的标号Stest……

END

语法格式:

IMPORT 标号 {[WEAK]}

IMPORT 伪指令用于通知编译器要使用的标号在其他的源文件中定义,但要在当前源文件中引用,而且无论当前源文件是否引用该标号,该标号均会被加入到当前源文件的 符号表中。

标号在程序中区分大小写, [WEAK] 选项表示当所有的源文件都没有定义这样一个标号时,编译器也不给出错误信息,在多数情况下将该标号置为 0 ,若该标号为 B 或 BL 指令引用,则将 B 或 BL指令置为 NOP 操作。

使用示例:

AREA Init , CODE , READONLY

IMPORT Main ;通知编译器当前文件要引用标号Main,但Main 在其他源文件中定义……

END

语法格式:

EXTERN 标号 {[WEAK]}

EXTERN 伪指令用于通知编译器要使用的标号在其他的源文件中定义,但要在当前源文件中引用,如果当前源文件实际并未引用该标号,该标号就不会被加入到当前源文件 的符号表中。

标号在程序中区分大小写, [WEAK] 选项表示当所有的源文件都没有定义这样一个标号时,编译器也不给出错误信息,在多数情况下将该标号置为 0 ,若该标号为 B 或 BL 指令引用,则将 B 或 BL指令置为 NOP 操作。

使用示例:

AREA Init , CODE , READONLY

EXTERN Main ;通知编译器当前文件要引用标号Main,但Main 在其他源文件中定义……

END

语法格式:

GET 文件名

GET 伪指令用于将一个源文件包含到当前的源文件中,并将被包含的源文件在当前位置进行汇编处理。可以使用 INCLUDE 代替 GET 。

汇编程序中常用的方法是在某源文件中定义一些宏指令,用 EQU 定义常量的符号名称,用 MAP和 FIELD 定义结构化的数据类型,然后用 GET 伪指令将这个源文件包含到 其他的源文件中。使用方法与 C 语言中的 " include " 相似。

GET 伪指令只能用于包含源文件,包含目标文件需要使用 INCBIN 伪指令

使用示例:

AREA Init , CODE , READONLY;

GET a1.s ;通知编译器当前源文件包含源文件a1.s;

通知编译器当前源文件包含源文件C:/ a2.s ……

END

语法格式:

INCBIN 文件名

INCBIN 伪指令用于将一个目标文件或数据文件包含到当前的源文件中,被包含的文件不作任何变动的存放在当前文件中,编译器从其后开始继续处理。

使用示例:

AREA Init , CODE , READONLY INCBIN a1.dat ;通知编译器当前源文件包含文件a1.dat

INCBIN C:/a2.txt ;通知编译器当前源文件包含文件C:/a2.txt……

END

语法格式:

名称 RN 表达式:

RN 伪指令用于给一个寄存器定义一个别名。采用这种方式可以方便程序员记忆该寄存器的功能。其中,名称为给寄存器定义的别名,表达式为寄存器的编码。

使用示例:

Temp RN R0 ;将R0 定义一个别名Temp

ROUT

语法格式:

{ 名称 } ROUT

ROUT 伪指令用于给一个局部变量定义作用范围。在程序中未使用该伪指令时,局部变量的作用范围为所在的 AREA ,而使用 ROUT 后,局部变量的作为范围为当前ROUT 和下一个 ROUT 之间。

全球最成功的投资者之一孙正义重酬押注人工智能革命。位居福布斯财富排行榜第82位的日本软银(Softbank)负责人本周二在加州圣克拉拉召开的ARM开发者大会上表示ARM芯片将推动人工智能走向奇点。奇点是未来主义者设想的时刻,那时候人工智能的智力将会超过人类,人类将无法预测和理解接下来的发展。

未来超级智能计算机能够控制卫生医疗到交通运输在内的一切,这或许会让你感到恐惧但同时会让你感到兴奋。孙正义说道:“很显然,如果这项技术被滥用那么就会带来难以想象的危险。不过如果你合理正确的使用,能够帮助人类获得更长拥有更高效的生活,在高速公路上也不会出现事故。”火和刀同样是非常危险的东西,但是只要能够合理使用就会给人类带来便利。

孙正义还给出一组数据:到了2018年,物联网设备的数量将会超过移动设备,到了2021年,我们将会拥有18亿台PC,86亿台移动设备,157亿台物联网设备。他还说:“在未来20年,物联网设备的数量将会超过1万亿台。”到了2035年,数据数量将会增长2400倍,从1 EB(exabyte)增长到2.3ZB(zetabytes)。

文章来源: cnBeta

近来翻了翻uC/OS-II官网给出来的ARM7-ARM9移植手册(AN-104),分析了在ARM中移植的问题,想想从来没有认真的学习过ARM的汇编,趁着这个机会复习复习吧。其实底层的东西才是创造力的心脏。

其中的移植代码中存在的很多问题比如中断的关闭和开启,任务级别的情景切换,中断到任务的情景切换都是我们在平时移植中讲到,我也不在此强调了。在官网中提供的移植过程中存在异常处理机制,这个本不是在移植过程中考虑的,但是文档中确实提供了一个比较好的处理方式。我在此对这一段时间的学习做一个总结。

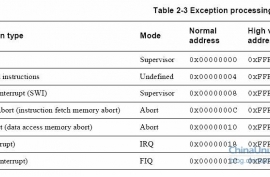

首先需要了解ARM的异常处理机制,异常是每一种处理器都必须考虑的问题之一,关键在于如何让处理,返回地址在什么位置都是需要考虑的,ARM中支持7种异常,其中包括复位、未定义指令异常、软中断异常、预取指令中止、数据中止、IRQ、IFQ。每一种异常运行在特定的处理器模式下。我在此逐一的分析。

一般异常发生后,CPU都会进行一系列的操作,这些操作有一部分是CPU自动完成,有一部分是需要我们程序员完成。

首先说明CPU会自动完成的部分,用ARM结构手册中的代码描述如下:

R14_ = return link //这个可以参看寄存器的说明,两个作用

SPSR_< exception_mode > = CPSR

CPSR[4:0] = exception mode number

CPSR[5] = 0 ; //AEM指令

If ==Reset or Fiq then //只有在复位和FIQ模式下才会关闭FIQ中断

CPSR[6] = 1 ;

CPSR[7] = 1 ; //任何异常模式下都会关闭IRQ中断

PC = exception vector address

从上面的代码中我们可以发现CPU自动处理的过程包括如下:

1、拷贝CPSR到SPSR_

2、设置适当的CPSR位: 改变处理器状态进入ARM状态;改变处理器模式进入相应的异常模式;设置中断禁止位禁止相应中断。

3、更新LR_,这个寄存器中保存的是异常返回时的链接地址

4、设置PC到相应的异常向量

以上的操作都是CPU自动完成,异常的向量表如下:

返回地址问题

异常的返回地址也是需要我们注意的地方,不同的异常模式返回地址也是存在差异的,这主要是因为各种异常产生的机理存在差别所导致的。这样我们的需要在异常进入处理函数之前或者在返回时调整返回地址,一般采用进入异常处理函数前进行手动调整。下面每一种异常R14保存的值都给了出来,其中也包含了CPU自动处理的部分,根据保存的R14就可以知道怎样实现地址的返回。

复位异常:

可以看出该模式下的先对来说返回地址也比较简单,不需要做太多的描述。

未定义的指令异常:

返回的方式也比较简单:

MOVS PC, R14

软中断异常:

返回的方式也比较简单:

MOVS PC, R14

预取指令中止异常:

返回需要做下面的调整:

SUBS PC, R14, #4

数据中止

返回地址需要做下面的调整:

如果需要重新访问数据则:

SUBS PC, R14, #8

如果不需要重新访问数据则:

SUBS PC, R14, #4

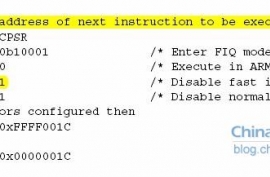

IRQ中断的处理过程:

返回地址需要做下面的调整:

SUBS PC,R14,#4

IFQ中断:

返回地址需要做下面的调整:

SUBS PC, R14 ,#4

从上面的代码可以知道,对于每一种异常,保存的返回地址都是不一样的,一般都需要我们手动的跳转,当然调整的时机也需要我们选择,是在进入处理前跳转还是返回时调整都是需要我们程序员控制的。

在ARM Developer Suite Developer Guide中对ARM处理器的异常处理操作提供能更加详细的解释,每一种异常下的处理方式如下文描述:

异常返回时另一个非常重要的问题是返回地址的确定,在前面曾提到进入异常时处理器会有一个保存LR 的动作,但是该保存值并不一定是正确的返回地址,下面以一个简单的指令执行流水状态图来对此加以说明。

我们知道在ARM 架构里,PC值指向当前执行指令的地址加8处,也就是说, 当执行指令A(地址0x8000)时,PC 等于指令C 的地址(0x8008)。假如指令A 是“BL”指令,则当执行该指令时,会把PC(=0x8008)保存到LR 寄存器里面,但是接下去处理器会马上对LR 进行一个自动的调整动作:LR=LR-0x4。这样,最终保存在 LR 里面的是 B 指令的地址,所以当从 BL 返回时,LR 里面正好是正确的返回地址。同样的调整机制在所有LR自动保存操作中都存在,比如进入中断响应时,处理器所做的LR 保存中,也进行了一次自动调整,并且调整动作都是LR=LR-0x4。

下面,我们对不同类型的异常的返回地址依次进行说明:

假设在指令A 处(地址0x8000)发生了异常,进入异常响应后,LR 上经过调整保存的地址值应该是B 的地址0x8004。

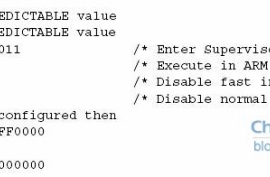

1、如果发生的是软件中断,即A 是“SWI”指令

异常是由指令本身引起的,从 SWI 中断返回后下一条执行指令就是B,正好是LR 寄存器保存的地址, 所以只要直接把LR 恢复给PC。

MOVS pc, lr

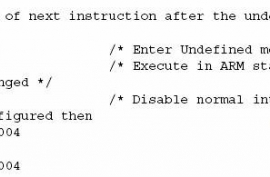

2、发生的是Undefined instruction异常

异常是由指令本身引起的,从异常返回后下一条执行指令就是B,正好是LR 寄存器保存的地址, 所以只要直接把LR 恢复给PC。

MOVS pc, lr

3、发生的是IRQ或FIQ中断

因为指令不可能被中断打断,所以A指令执行完以后才能响应中断,此时PC已更新,指向指令D的地址(地址0x800C),LR 上经过调整保存的地址值是C 的地址0x8008。中断返回后应该执行B指令,所以返回操作是:

SUBS pc, lr, #4

4、发生的是Prefetch Abort异常

该异常并不是处理器试图从一个非法地址取指令时触发,取出的指令只是被标记为非法,按正常处理流程放在流水线上,在执行阶段触发Prefetch Abort异常,此时LR 上经过调整保存的地址值是B 的地址0x8004。异常返回应该返回到A指令,尝试重新取指令,所以返回操作是:

SUBS pc, lr, #4

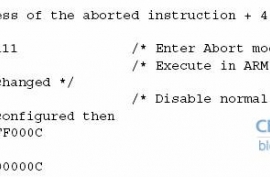

5、发生的是“Data Abort”

CPU访问存储器时触发该异常,此时PC指向指令D的地址(地址0x800C),LR 上经过调整保存的地址值是C 的地址0x8008。异常返回后,应回到指令A,尝试重新操作存储器,所以返回操作是:

SUBS pc, lr, #8

以上就是ARM异常的CPU操作部分,接下来就是程序员应该完成的操作。

1. 由于CPU会自动跳转到对应的异常向量中,因此只需要在在各个异常向量中存放对应的操作,最简单的都是存放一个B指令跳转到对应的异常处理函数的操作即可。但由于B指令的跳转返回只有+-32M,而异常处理函数的地址可能会超过+-32M,因此可以采用另一种方式实现方式:在异常向量中保存一条指令LDR PC [addr],其中的addr中就保存了异常处理函数的地址,当然addr的相对地址要小于+-32M。这样也就解决了跳转范围的问题。

2. 接下来就是异常处理函数对应的操作,可以在进入异常处理之前就进行返回地址的调整,这样后面就不用进行处理啦,当然也可以在返回过程中再调整。一般都是在这个过程中进行调整。进行压栈操作,保存对应的环境变量。调用实际的处理过程等。

3. 出栈,恢复CPU的状态和寄存器的值。由于第一步中已经调整好返回地址,这一步不需要再次调整。当然如果之前没有调整,这里则需要进行相应的调整。

在uC/OS-II的官网移植中采用通用异常处理函数的方式实现异常的处理,下面我们来分析其中的部分代码:

首先是处理器部分的移植,包括异常向量、异常的ID号,存储异常处理函数地址的地址等:

/*ARM的异常ID号,支持7种类型的异常,每一种异常都存在一个ID号*/

#define OS_CPU_ARM_EXCEPT_RESET 0x00

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR 0x01

#define OS_CPU_ARM_EXCEPT_SWI 0x02

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT 0x03

#define OS_CPU_ARM_EXCEPT_DATA_ABORT 0x04

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT 0x05

#define OS_CPU_ARM_EXCEPT_IRQ 0x06

#define OS_CPU_ARM_EXCEPT_FIQ 0x07

#define OS_CPU_ARM_EXCEPT_NBR 0x08

/*异常向量地址*/

#define OS_CPU_ARM_EXCEPT_RESET_VECT_ADDR (OS_CPU_ARM_EXCEPT_RESET * 0x04 + 0x00) //0x00

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR (OS_CPU_ARM_EXCEPT_UNDEF_INSTR * 0x04 + 0x00) //0x04

#define OS_CPU_ARM_EXCEPT_SWI_VECT_ADDR (OS_CPU_ARM_EXCEPT_SWI * 0x04 + 0x00) //0x08

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_PREFETCH_ABORT * 0x04 + 0x00) //0x0c

#define OS_CPU_ARM_EXCEPT_DATA_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_DATA_ABORT * 0x04 + 0x00) //0x10

/*这个异常是ARM中不支持的异常*/

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT_VECT_ADDR (OS_CPU_ARM_EXCEPT_ADDR_ABORT * 0x04 + 0x00) //0x14

#define OS_CPU_ARM_EXCEPT_IRQ_VECT_ADDR (OS_CPU_ARM_EXCEPT_IRQ * 0x04 + 0x00) //0x18

#define OS_CPU_ARM_EXCEPT_FIQ_VECT_ADDR (OS_CPU_ARM_EXCEPT_FIQ * 0x04 + 0x00) //0x1c

/*存储异常处理函数地址的地址*/

/* ARM exception handlers addresses */

#define OS_CPU_ARM_EXCEPT_RESET_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_RESET * 0x04 + 0x20) //0x20

#define OS_CPU_ARM_EXCEPT_UNDEF_INSTR_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_UNDEF_INSTR * 0x04 + 0x20) //0x24

#define OS_CPU_ARM_EXCEPT_SWI_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_SWI * 0x04 + 0x20) //0x28

#define OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_PREFETCH_ABORT * 0x04 + 0x20) //0x2c

#define OS_CPU_ARM_EXCEPT_DATA_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_DATA_ABORT * 0x04 + 0x20) //0x30

#define OS_CPU_ARM_EXCEPT_ADDR_ABORT_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_ADDR_ABORT * 0x04 + 0x20) //0x34

#define OS_CPU_ARM_EXCEPT_IRQ_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_IRQ * 0x04 + 0x20) //0x38

#define OS_CPU_ARM_EXCEPT_FIQ_HANDLER_ADDR (OS_CPU_ARM_EXCEPT_FIQ * 0x04 + 0x20) //0x3c

/*存储在异常向量中的内容,实质上是LDR PC,[PC,#0x18]的机器码*/

#define OS_CPU_ARM_INSTR_JUMP_TO_SELF 0xEAFFFFFE

/* ARM "Jump To Exception Handler" asm instruction */

#define OS_CPU_ARM_INSTR_JUMP_TO_HANDLER 0xE59FF018

异常的初始化函数,首先,完成了在异常向量中存储指令的操作,采用机器码的形式就能避免直接访问寄存器什么的,其次,完成在固定的地址处存放对应异常处理函数的地址。其中采用了赋值的形式也是需要注意的,采用的强制类型转换和指针相结合的形式。保证了是修改地址处的内容。而不是修改地址。

/*初始化异常中断向量*/

void OS_CPU_InitExceptVect (void)

{

/*

OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR是对应中断向量表的地址

OS_CPU_ARM_INSTR_JUMP_TO_HANDLER是保存了对应的OS_CPU_ARM_INSTR_JUMP_TO_HANDLER(实质上是一个指令)

实质上就是在异常向量中存放了:LDR PC [PC, #0x18],也就是让PC指向对应的异常处理地址中的内容,

也就是实现到实际处理函数的跳转。

异常处理地址中存储了实际的异常处理函数的地址

其他的异常也有相同的操作,OS_CPU_ARM_INSTR_JUMP_TO_HANDLER是一个指令的机器码形式

*/

(*(INT32U *)OS_CPU_ARM_EXCEPT_UNDEF_INSTR_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U *)OS_CPU_ARM_EXCEPT_UNDEF_INSTR_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptUndefInstrHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_SWI_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U *)OS_CPU_ARM_EXCEPT_SWI_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptSwiHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U *)OS_CPU_ARM_EXCEPT_PREFETCH_ABORT_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptPrefetchAbortHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_DATA_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U *)OS_CPU_ARM_EXCEPT_DATA_ABORT_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptDataAbortHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_ADDR_ABORT_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U *)OS_CPU_ARM_EXCEPT_ADDR_ABORT_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptAddrAbortHndlr;

(*(INT32U *)OS_CPU_ARM_EXCEPT_IRQ_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U *)OS_CPU_ARM_EXCEPT_IRQ_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptIrqHndlr;

/*在异常向量中存储对应的操作,实质上就是将PC值调转*/

(*(INT32U *)OS_CPU_ARM_EXCEPT_FIQ_VECT_ADDR) = OS_CPU_ARM_INSTR_JUMP_TO_HANDLER;

(*(INT32U *)OS_CPU_ARM_EXCEPT_FIQ_HANDLER_ADDR) = (INT32U)OS_CPU_ARM_ExceptFiqHndlr;

}

有必要的讨论一下,为什么在向量中存储的是指令: LDR PC,[PC,#0x18],我们从上面的地址可以知道,IRQ异常处理函数地址被存储到了0x00000038中,异常向量与该地址之间的差值是0x20,那么为什么在其中存储的值只是0x18呢?这还要讨论ARM的流水线结构,当前执行的命令相比PC指向的地址差0x08。也就是当前执行的指令的地址是PC-0x08.当PC指向异常向量以后(取值),还需要等待一个时钟(译码)之后才会被执行(真正意义上的执行操作),而这时PC值已经被更新了。指向了Vector+0x8的位置,因此我们可以知道,当执行向量中的代码时,这时PC=Vector+0x8,而这时相对于固定的0x20-0x08=0x18,这也就是为什么是LDR PC,[PC,#0x18],而不是LDR PC,[PC,#0x20].

采用上面的例子说明IRQ的向量为0x00000018,而设定好的固定地址用来存储对应异常处理函数地址的地址是0x00000038,当CPU执行完PC = 0x00000018以后,还需要译码、才能被执行,这时候PC值已经更新为PC = 0x00000018 + 0x08;这时候固定地址距离PC的相对位置位0x00000038 – PC = 0x18,而该地址中保存了IRQ中断的通用处理函数OS_CPU_ARM_ExceptIrqHndlr()的地址,LDR PC,[PC,#0x18]这条指令是指将PC+0x18地址处的内容加载到PC中,实质上也就完成跳转到异常处理函数的操作。

这样处理的好处是因为LDR的加载范围是一个固定值+-32M,我们不能保证异常处理程序的地址刚好在+-32M左右,采用这种LDR PC, ADDR(固定地址)的形式就能实现大范围的跳转操作。

我们仅仅以FIQ中断处理的形式进行讨论,其他的异常有一定的相似性,只是在返回地址上存在差别。这段代码主要是完成寄存器的压栈,返回地址的调整,保存等操作。具体的看下面的分析:

AREA CODE, CODE, READONLY

CODE32

OS_CPU_ARM_ExceptFiqHndlr

;修改中断返回地址,这属于进入真正处理函数前的返回地址调整,具体的返回地址依据前面保存的R14进行相应的修改。

SUB LR, LR, #4 ; LR offset to return from this exception: -4.

;压栈操作

STMFD SP!, {R0-R12, LR} ; Push working registers.

;保存链接寄存器

MOV R2, LR ; Save link register.

;设置好ID号,这是非常必要的,只有这样才能辨别属于那种异常

MOV R0, #OS_CPU_ARM_EXCEPT_FIQ ; Set exception ID

/*跳转到通用的异常处理函数,传递的参数是异常ID号*/

B OS_CPU_ARM_ExceptHndlr ; Branch to global exception handler.

OS_CPU_ARM_ExceptHndlr(except_type)是一个通用的异常处理函数,可以对除了IRQ以外的其他异常进行控制操作。在这个通用处理函数中又调用了下面的函数OS_CPU_ARM_ExceptHndlr_BreakExcept()或者OS_CPU_ARM_ExceptHndlr_BreakTask()。这两个函数中又调用了通用处理函数OS_CPU_ExceptHndlr(),然后OS_CPU_ExceptHndlr()中调用具体的中断处理操作。

一般的OS_CPU_ExceptHndlr()处理形式,可以认为是一个模板如下:

void OS_CPU_ExceptHndlr (INT32U except_type)

{

/* Determine behavior according to exception type (except_type) */

/* If an IRQ or FIQ ,具体的可能要使用中断向量等形式实现*/

while (there are interrupting devices) {

/* Clear interrupting device */

OS_CPU_SR_INT_En(); /* Enable nesting, if desired */

/* Handle interrupt */

}

}

这是其中的一段关于IRQ中断的文字复述:

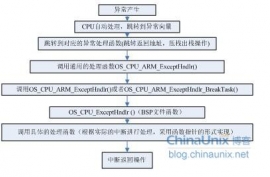

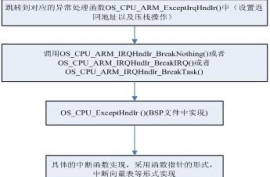

IRQ中断的基本的流程图如下:

以上的uC/OS-II异常处理就分析完了,这种方式的实现实质上是采用了通用模板的形式,这样实现出来的形式只需要控制一定的,具体的一些IRQ中断处理函数(如定时器,GPIO等的中断),与具体的厂商有很大的关系,有的厂商采用硬件寄存器的方式进行设计,有的采用软件方式实现,因此具体的中断。

后面我再分析我们通常认为的中断(实质上就是IRQ和IFQ中某一个具体中断)处理方式。

文章来源:博客园