ARM

你知道单片机、ARM、DSP都是CPU吗?

demi 在 提交

处理器的命名应该包含两类:指令集架构命名规则和处理器系列规则。

ARM 架构是构建每个 ARM 处理器的基础。ARM 架构随着时间的推移不断发展,其中包含的架构功能可满足不断增长的新功能、高性能需求以及新兴市场的需要。

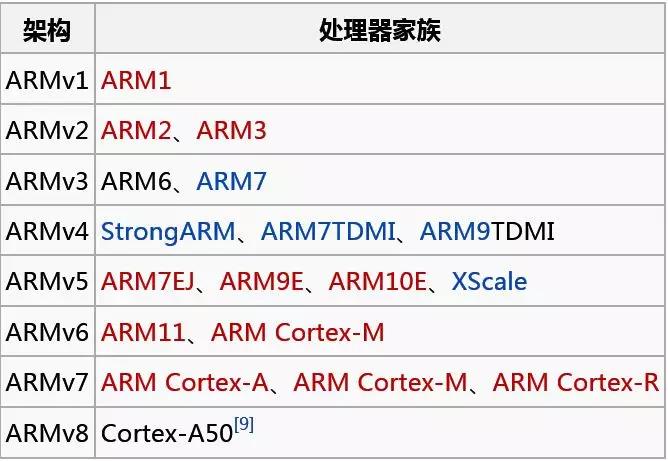

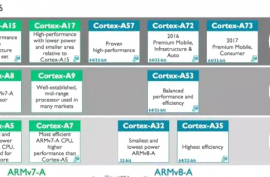

可以先来看一张简图:

可见:架构的命名比较规则从ARMv1到ARMv8,数字越大越先进。x(variants) 分成四个组成部分:

ARMv -- 固定字符,即ARM Version

n -- 指令集版本号。迄今为之,ARM架构版本发布了8个系列,所以n=[1:8]。其中最新的版本是第8版,具体看ARM官方网站。

variants -- 变种。

x(variants)-- 排除x后指定的变种

但是处理器系列的命名就比较混乱了,因此接下来以架构的顺序来介绍ARM的历史:

(1) ARMv1、ARMv2 这两代没有做CPU,没有商业化;

(2)ARMv3 对应的 CPU 是 ARM6,它作为IP核、独立的处理器、具有片上高速缓存、MMU和写缓冲的集成CPU;

(3)ARMv4 首次增加 Thumb 指令集:

有符号和无符号的半字读取和写入指令。

带符号的字节读取和写入指令。

增加了处理器的系统模式(特权模式)。在该模式下,使用的是用户模式下的寄存器。

为结构定义的操作预留一些SWI(软中断指令)空间

ARMv4和ARMv4T结构的处理器得到了广泛的应用。SA-110、SA-1110等是基于ARMv4的;

对应的 CPU 有:ARM7TDMI、ARM720T、 ARM9TDMI、ARM940T、ARM920T、Intel的StrongARM等是基于ARMv4T版本。

(4) ARMv5 包括v5TE和v5TEJ ,v5TE在v5T的基础上增加了信号处理(DSP)指令集,v5TEJ除了具备v5T的功能外,还可以执行JAVA字节 代码,是在ARM上执行JAVA指令的效率提高了5-10倍,并且降低了功耗。

对应的 CPU 有:

ARMv5TE指令集:ARM9-E-S,ARM966-E-S,ARM1020-E,ARM1022-E,ARM940-T

ARMv5EJ指令集:ARM926-EJ-S,ARM7-EJ-S,ARM1026-EJ-S

(5) ARMv6 首次增加 SIMD,升级为 Thunmb-2,首次增加TrustZone;

ARMv6是2001年发布的。其目标是在有效的芯片面积上为嵌入式系统提供更高的性能。

对应 CPU 有:ARM1136-J(F)-S,ARM1156-J(F)-S,ARM1176-J(F)-S,ARM11 MPCore

ARMv6是ARM进化史上的一个重要里程碑:从那时候起,许多突破性的新技术被引进,存储器系统加入了很多的崭新的特性,单指令流多数据流(SIMD)指令也是从v6开始首次引入的。而最前卫的新技术,就是经过优化的Thumb‐2指令集,它专为低成本的单片机及汽车组件市场。

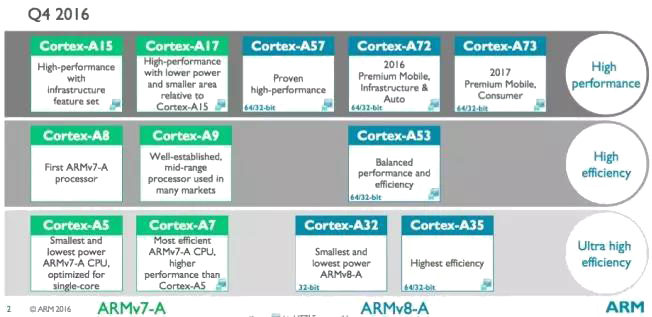

(6)ARMv7 首次增加 M(长乘法指令),NEON(DSP+SIMD),2004年发布了新的ARMv7体系结构。在这个版本中,内核架构首次从单一款式变成3种款式。

CPU 系列名字为“Cortex”,分为了3个款式:A、R、M & SC;

(6.1)A 系列,支持大型嵌入式系统,如手机;

节能:A5,A7

平衡:A8,A9

性能:A15,A17

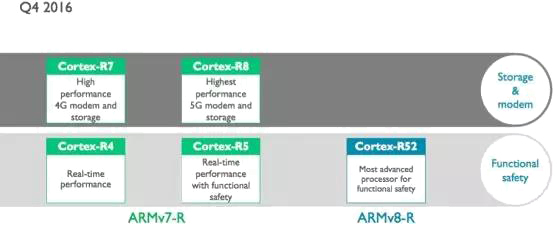

(6.2)R 系列,Real-time 处理器,即执行一个指令段的耗时是固定时钟周期数,用于高端的嵌入式系统,尤其是那些带有实时要求的--又要快又要实时。

用于比如汽车控制,这种不允许随机执行时间的应用

功能安全:R4,R5

存储、调制解调:R7,R8

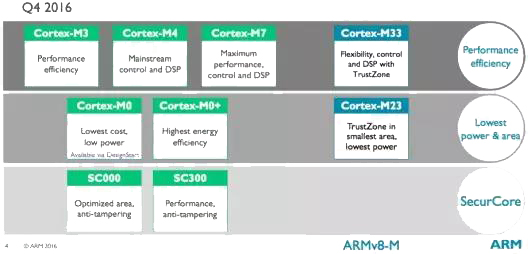

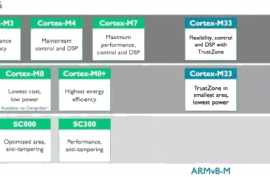

(6.3)M 系列,单片机市场,抢8051的生意;

超低的功耗、面积:M0,M0+

平衡:M3,M4,M7

(6.4)SC(SecurCore)系列,主打“安全”,面向支付、政府、SIM 卡

SC000,SC300;

(7)ARMv8 首次增加 指令集A64,可执行64位指令;可在 32位 和 64位 之间切换;是ARM公司为满足新需求而重新设计的一个架构,是近20年来,ARM架构变动最大的一次。它引入的Execution State、Exception Level、Security State等新特性,已经和我们对旧的ARM架构的认知,有很大差距了。

(7.1)A 系列,

节能:A32,A35

平衡:A53,

性能:A57,A72,A73

(7.2)R 系列

功能安全:R52

(7.3)M 系列,

超低的功耗、面积:M23

平衡:M33

本文简单介绍了ARM架构的一些命名规则,希望对大家有帮助。

转自:嵌入式ARM

• Arm以引领安全为己任,加速自动驾驶技术在大众市场部署

• Arm “安全就绪”(Safety Ready)计划:协助Arm芯片合作伙伴开发车用SoC

• 分核-锁步(Split-Lock):在应用处理器中首次搭载具有颠覆性的安全创新

• 针对7纳米制程进行优化,Cortex-A76AE是全球第一款具有集成安全、高性能、领先效率和防护等IP选项的自动驾驶级处理器

2018年9月28日 – Arm宣布推出 “安全就绪”(Arm Safety Ready)计划,及全球首款集成功能安全的自动驾驶级处理器——专为汽车行业设计的全新产品Arm Cortex-A76AE。该处理器搭载分核-锁步(Split-Lock)技术,这也是在应用处理器中首次集成具有颠覆性的安全创新技术。

对于那些明显的技术因素,无论是控制自动驾驶系统的各个方面还是在确保乘客信赖自动驾驶方面,安全都是其中汽车主机厂考量的重中之重。如果消费者无法信任其车辆的自动驾驶系统是安全的,那么这种技术在大众市场的普及将会很缓慢。

自动驾驶要消除的正是人为因素,即驾驶员所犯的错误。考虑到所有事故中有94%是由驾驶员的失误导致,因此预计全自动驾驶将显著减少事故数量和死亡人数。这也是为什么在开发自动驾驶级SoC和系统时,安全绝不可作为发生事故之后的措施,而将其置于次要于性能、能效和防护的位置。然而不幸的是,目前致力于实现L5级的自动驾驶原型车辆通常基于高能耗和代价不菲的数据中心CPU,其中甚至连最基本的功能安全都是缺失的。

多年来,Arm一直将安全放在首位,正因如此,Arm的 IP得以在ADAS(高级驾驶员辅助系统)应用芯片中占据高达65%的市场份额。Arm的汽车生态系统可通过最新的ISO认证获得业界最广泛的功能安全IP。为进一步确保Arm的芯片合作伙伴在安全性方面领先一步,Arm宣布推出Arm“ 安全就绪”计划,该计划集中了Arm在安全领域大量投入的成果,有助于加快Arm芯片合作伙伴和整个汽车供应链的开发进度,从而将更安全的产品以更快的速度推向市场。

Arm在安全领域的领先优势并不止于整合最新的认证和标准。Arm同时推出首款集成功能安全的自动驾驶级处理器——全新产品 Arm Cortex-A76AE,专为汽车行业设计。该芯片搭载 分核-锁步(Split-Lock)技术,是一款具有颠覆性的安全创新,并首次在应用处理器中得以实现。

为更高级别的自动驾驶实现“安全就绪”

“安全就绪”计划中包括Arm现有的安全产品以及全新产品或未来产品,这些产品的开发采用严格的功能安全流程,包括支持ISO 26262和IEC 61508标准的系统流程和开发。“安全就绪”计划提供一站式软件、工具、组件、认证和标准,可为Arm合作伙伴简化并降低整合功能安全的成本。凭借“安全就绪”计划,合作伙伴和汽车主机厂可以确保其SoC和系统具有自动驾驶应用所需的最高级别功能安全。

Cortex-A76AE:全球首款集成功能安全的自动驾驶级处理器

Cortex-A76AE专为汽车行业设计,针对7纳米工艺节点进行了优化,是一款颠覆性的全新处理器。其中AE代表“汽车增强型”,任何带有AE标志的Arm IP都将包含满足车载应用的特定功能。

自动驾驶需要更高层级的处理能力,其中内在的安全性将是标配。Cortex-A76AE作为业界首款具有分核-锁步功能的高性能应用处理器,结合了自动驾驶应用所需的处理性能和高汽车安全完整性。虽然分核-锁步功能对业界而言并不陌生,但Arm率先将其引入专为高性能汽车应用而设计的处理器,例如自动驾驶。

分核-锁步功能可实现以下性能:

• 具备以往锁步CPU部署中无法实现的灵活性

• SoC中的CPU群集可配置成“分核模式”以实现高性能,其中群集中的两个(或四个)独立CPU可用于各种任务和应用程序

• 若配置成“锁步模式”下,CPU将处于锁步状态,在群集中创建一对(或两对)锁步的CPU,以实现更高的汽车安全完整性应用

• CPU集群可在硅片生产后配置为在任一模式下混合运行

凭借Arm在高能效计算领域的领导地位,选用Cortex-A76AE的汽车主机厂还可在其原型车辆中设计仅需瓦级而非千瓦级能耗的自动驾驶系统。低能耗还可以实现更加节能地使用车辆电池电量,同时结合热效率提升计算能力的封装,进而延长车辆续航能力以降低行驶成本。

正如Arm一贯的开发思路,从整体系统的角度思考,对Cortex-A76AE进行完善。Arm正向业界推出全新的汽车增强型系统IP,用于设计全面的自动驾驶级SoC。全新CoreLink GIC-600AE、CoreLink MMU-600AE和CoreLink CMN-600AE可提供高性能的中断管理、扩展虚拟化和内存管理等关键功能,以及连接多个CPU集群扩展安全多核系统的功能。这些产品旨在实现高性能系统的同时,又将汽车安全完整性从ASIL-B级别提升至ASIL-D级别,并支持分核-锁步功能和嵌入到Cortex-A76AE设计之中的功能安全系统功能。

唯有Arm汽车生态系统方能提供的可扩展性

随着自动驾驶系统的软件复杂性和运算容量急剧增加,开发成本呈指数级增长态势。根据了解到的背景,预计L5级自动驾驶车辆将需要10亿行代码,相比波音787梦想飞机(Boeing 787 Dreamliner)需要的代码仅为1400万行。Arm与其强大的汽车开发人员生态系统正致力于通过通用架构简化汽车软件堆栈的各个层面及相关开发工具,从而实现成本最优。

Arm的汽车IP路线图

Cortex-A76AE是“汽车增强型”处理器路线图中的第一款产品,它将提供业界最全面的功能安全IP产品组合。全新路线图包括“Helios-AE”和“Hercules-AE”系列,都将针对7纳米制程进行优化。随着这些产品相继推出,更多细节将会随之公布。

自1996年以来,Arm一直为汽车应用设计芯片,目前也只有Arm能够解决整车所有元件的计算需求。正因如此,全球前15大汽车芯片制造商都是Arm的授权厂商,而基于Arm架构的芯片为当今65%的ADAS应用和85%的IVI应用提供驱动。通过为行业提供高安全性、自动驾驶级别的计算解决方案,Arm及其生态系统确保安全性不再是发生事故之后的措施,并帮助汽车主机厂赢得消费者信任,推动安全与全自动驾驶车辆的全面普及。

芯片的加密,保证了芯片内部信息的安全性。有工程师会问:芯片加密后别人还能解密吗?这芯片安全吗?本文将为大家介绍几种不同类型芯片的加密方式。

随着信息技术的发展,信息的载体——芯片的使用也越来越多了,随之而来的是各个芯片厂商对芯片保密性要求越来越高,用芯片加密的方式来确保芯片内部信息的安全性。其实芯片的安全加密问题与芯片的类型有关,不同类型的芯片加密后有不一样的效果。

市面上现有的芯片种类很多,主要包括Flash,MCU,ARM,DSP,CPLD等。

一、Flash类芯片加密

Flash类芯片包含SPI Nor FLASH ,并行Nor FLASH,NAND FLASH,EMMC等,这些Flash类的芯片都没有非常牢固的加密功能,对code区进行加密后,只能进行写保护,如果有人想复制你的代码,只要读取母片即可,所以这类芯片安全性较低。

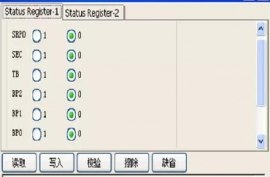

将上图所示的信息设置好写入芯片后,对应的区域即进入保护状态,不能编程,擦除,只能通过清空加密寄存器中的信息,才能从新对芯片进行擦除,编程操作。

二、MCU,ARM类芯片加密

经常会有人就MCU加密保护后能否二次使用的问题进行咨询。对于加密后的芯片能不能二次使用这个问题,得具体看是哪个类型的芯片,类似于TI 的MSP430系列芯片加密后即不可进行二次使用,这个加密为OTP(One Time Programmable)型,只能进行一次烧录。其原理是通过高压烧断熔丝,使外部设备再也无法访问芯片,这个是物理性,不可恢复,如要加密,请慎用!

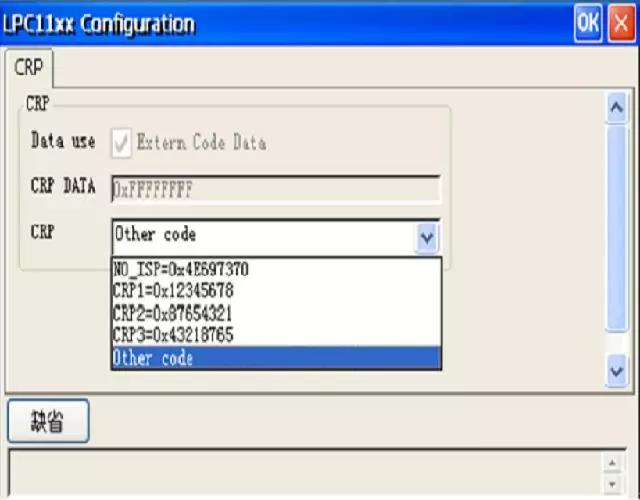

但对于大部分ARM芯片来说,加密后芯片还是可以进行二次使用的。类似于NXP ARM类型芯片有3级可选的加密,即Level 1,Level 2,Level 3。其中Level 1 就是不做读保护级别,即可以读出芯片中的数据,但不能对芯片进行编程,擦除操作。如果芯片被设置为Level 2保护,这种状态下,不能读取芯片内的程序代码内容,也不能对芯片再次做存储空间的擦写或芯片调试了。而Level 3级别的保护是不可逆的,保护后即不能进行其他操作。综上,3个级别当中的Level 1和Level 2加密后还是可以通过解密的方式对芯片进行第二次操作,这种加密等级设置是比较人性化的。下图为P800系列编程器加密设置操作界面。

三、DSP类芯片加密

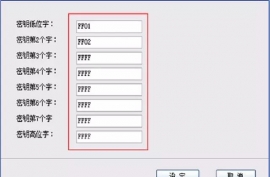

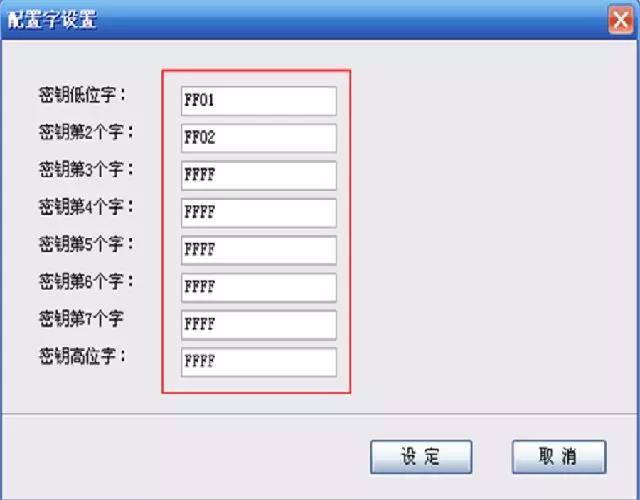

该类型的芯片加密形式是通过在特定的区域写入客户的密码进行加密。这种加密是可逆的,可以通过输入对的密码进行任何操作。但是有一种方式是不可逆的,即密码为全“0”。其P800系列编程器加密设置窗口如下。

四、CPLD、FPGA类芯片加密

这类芯片加密后一般都可以通过擦除方式进行解密,不能对加密的芯片进行读取操作,这种加密对芯片来说还是比较安全的。

以上便是几种常见类型芯片的加密方式以及加密后的效果,用户可以根据芯片类型选择对应的加密方式,最大程度确保芯片内部信息的安全。

转自:ZLG致远电子 研发部