硬件原理图中的“英文缩写”大全

demi 在 提交

demi 在 提交

常用控制接口

EN:Enable,使能。使芯片能够工作。要用的时候,就打开EN脚,不用的时候就关闭。有些芯片是高使能,有些是低使能,要看规格书才知道。

CS:Chip Select,片选。芯片的选择。通常用于发数据的时候选择哪个芯片接收。例如一根SPI总线可以挂载多个设备,DDR总线上也会挂载多颗DDR内存芯片,此时就需要CS来控制把数据发给哪个设备。

RST:Reset,重启。有些时候简称为R或者全称RESET。也有些时候标注RST_N,表示Reset信号是拉低生效。

INT:Interrupt,中断。前面的文章提到过,中断的意思,就是你正睡觉的时候有人把你摇醒了,或者你正看电影的时候女朋友来了个电话。

PD:Power Down,断电。断电不一定非要把芯片的外部供电给断掉,如果芯片自带PD脚,直接拉一下PD脚,也相当于断电了。摄像头上会用到这根线,因为一般的摄像头有3组供电,要控制三个电源直接断电,不如直接操作PD脚来的简单。(在USB Type-C接口中有一个Power Delivery也叫PD,跟这个完全不一样,不要看错了。)

CLK:Clock,时钟。时钟线容易干扰别人也容易被别人干扰,Layout的时候需要保护好。对于数字传输总线的时钟,一般都标称为xxx_xCLK,如SPI_CLK、SDIO_CLK、I2S_MCLK(Main Clock)等。对于系统时钟,往往会用标注频率。如SYS_26M、32K等。标了数字而不标CLK三个字,也是无所谓的,因为只有时钟才会这么标。

CTRL:control,控制。写CONTROL太长了,所以都简写为CTRL,或者有时候用CMD(Command)。

SW:Switch,开关。信号线开关、按键开关等都可以用SW。

PWM:PWM,这个已经很清晰了。

REF:Reference,参考。例如I_REF,V_REF等。参考电流、参考电压。

FB:Feedback。反馈。升压、降压电路上都会有反馈信号,意义和Reference是类似的,芯片根据外部采集来的电压高低,动态调整输出。外部电压偏低了,就加大输出,外部电压偏高了,就减小输出。

A/D:Analog/Digital,模拟和数字的。如DBB=Digital Baseband,AGNG=Analog Ground。

D/DATA:数据。I2C上叫做SDA(Serial DATA),SPI上叫做SPI_DI、SPI_DO(Data In,Data Out),DDR数据线上叫做D0,D1,D32等。

A/Address:地址线。用法同数据线。主要用在DDR等地址和数据分开的传输接口上。其他的接口,慢的像I2C、SPI,快的像MIPI、RJ45等,都是地址和数据放在一组线上传输的,就没有地址线了。

常用方向的标识

TX/RX:Transmit,Receive。发送和接收。这个概念用在串口(UART)上是最多的,一根线负责发送,一根线负责接收。这里要特别注意,一台设备的发送,对应另一台设备就是接收,TX要接到RX上去。如果TX接TX,两个都发送,就收不到数据了。

为了防止出错,可以标注为:UART1_MRST、UART1_MTSR。Master RX Slave TX的意思。Master就是主控芯片,Slave就是从设备。TX、RX很容易标错的,尤其是原理图有几十页的情况下。

P/N:Positive、Negative。正和负。用于差分信号线。现在除了DDR和SDIO之外,其他很少有并行数据传输接口了。USB、LAN、MIPI的LCD和Camera、SATA等等,高速数据总线几乎都变成了串行传输数据了。

串行信号线速度很高,随便就上GHz,电压很低只有几百毫伏,因此很容易被干扰,要做成差分信号,即用两根线传一个数据,一个传正的一个传负的。传到另外一边,数据相减,干扰信号被减掉,数据信号负负得正被加倍。

对于RESET_N这样的信号来讲,只起到重点标注的作用,表示这个RESET信号是拉低才生效的。大部分设备都是低有效的RESET,偶尔会有一些设备拉高RESET。

L/R:Left、Right。通常用于音频线,区分左右。有些时候如喇叭的信号是通过差分来传输的,就是SPK_L_N、SPK_L_P这样的标识。

如下图,某2.1声道智能音箱音频输出(喇叭连接器端)。TAS5751是音频功放,HF是高频High frequency(2.1音响有专门的低频输出)。P和N用 和-代替。

常用设备缩写

BB:Baseband,基带处理器。十几年前的的手机芯片只有通信功能,没有这么强大的AP(跑系统的CPU),手机里的主芯片都叫做Baseband基带芯片。后来手机性能强大了,还是有很多老工程师习惯把主芯片叫做BB,而不是叫CPU。

P(GPIO):很多小芯片,例如单片机,接口通用化比较高,大部分都是GPIO口,做什么用都行,就不在管脚上标那么清楚了,直接用P1,P2,P1_3这样的方式来标明。P多少就是第多少个GPIO。P1_3就是第1组的第3个GPIO。(不同组的GPIO可能电压域不一样)

BAT:Battery,电池。所有的电池电压都可以叫做VBAT。

CHG:Charge,充电。

CAM:Camera,摄像头。

LCD:显示器。

TP:Touch Panel,触摸屏。(注意不要和Test Point测试点搞混了)

DC:Direct Current,直流电。用在设备上通常用作外部直流输入接口,而不是指供电方式或者供电电压什么的,例如VCC_DC_IN的含义,就是外部DC接口供电。

来源:博客园isAndyWu

芯片在电子学中是一种把电路小型化的方式,主要包括半导体设备,也包括被动组件等,并通常制造在半导体晶圆表面上。

前述将电路制造在半导体芯片表面上的集成电路又称薄膜集成电路;另有一种厚膜混成集成电路是由独立半导体设备和被动组件,集成到衬底或线路板所构成的小型化电路。

集成电路产业的特色是赢者通吃,像Intel这样的巨头,巅峰时期的利润可以高达60%。那么,相对应动辄几百、上千元的CPU,它的实际成本到底是多少呢?

先来看看制造过程

芯片制作完整过程包括芯片设计、晶片制作、封装制作、成本测试等几个环节,其中晶片制作过程尤为的复杂。 精密的芯片其制造过程非常的复杂首先是芯片设计,根据设计的需求,生成的“图样”。

1、芯片的原料晶圆

晶圆的成分是硅,硅是由石英沙所精练出来的,晶圆便是硅元素加以纯化(99.999%),接着是将些纯硅制成硅晶棒,成为制造集成电路的石英半导体的材料,将其切片就是芯片制作具体需要的晶圆。晶圆越薄,生产的成本越低,但对工艺就要求的越高。

2、晶圆涂膜

晶圆涂膜能抵抗氧化以及耐温能力,其材料为光阻的一种。

3、晶圆光刻显影、蚀刻

该过程使用了对紫外光敏感的化学物质,即遇紫外光则变软。通过控制遮光物的位置可以得到芯片的外形。在硅晶片涂上光致抗蚀剂,使得其遇紫外光就会溶解。

这时可以用上第一份遮光物,使得紫外光直射的部分被溶解,这溶解部分接着可用溶剂将其冲走。这样剩下的部分就与遮光物的形状一样了,而这效果正是我们所要的。这样就得到我们所需要的二氧化硅层。

4、搀加杂质

将晶圆中植入离子,生成相应的P、N类半导体。具体工艺是是从硅片上暴露的区域开始,放入化学离子混合液中。

这一工艺将改变搀杂区的导电方式,使每个晶体管可以通、断、或携带数据。简单的芯片可以只用一层,但复杂的芯片通常有很多层,这时候将这一流程不断的重复,不同层可通过开启窗口联接起来。

这一点类似多层PCB板的制作制作原理。 更为复杂的芯片可能需要多个二氧化硅层,这时候通过重复光刻以及上面流程来实现,形成一个立体的结构。

5、晶圆测试

经过上面的几道工艺之后,晶圆上就形成了一个个格状的晶粒。通过针测的方式对每个晶粒进行电气特性检测。

一般每个芯片的拥有的晶粒数量是庞大的,组织一次针测试模式是非常复杂的过程,这要求了在生产的时候尽量是同等芯片规格构造的型号的大批量的生产。

数量越大相对成本就会越低,这也是为什么主流芯片器件造价低的一个因素。

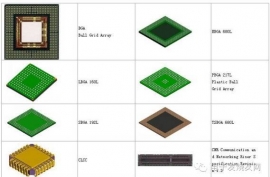

6、封装

将制造完成晶圆固定,绑定引脚,按照需求去制作成各种不同的封装形式,这就是同种芯片内核可以有不同的封装形式的原因。

比如:DIP、QFP、PLCC、QFN 等等。这里主要是由用户的应用习惯、应用环境、市场形式等外围因素来决定的。

7、测试、包装

经过上述工艺流程以后,芯片制作就已经全部完成了,这一步骤是将芯片进行测试、剔除不良品,以及包装。

芯片的硬件成本构成

芯片的成本包括芯片的硬件成本和芯片的设计成本。

芯片硬件成本包括晶片成本+掩膜成本+测试成本+封装成本四部分(像ARM阵营的IC设计公司要支付给ARM设计研发费以及每一片芯片的版税,但笔者这里主要描述自主CPU和Intel这样的巨头,将购买IP的成本省去),而且还要除去那些测试封装废片。

用公式表达为:

芯片硬件成本=(晶片成本+测试成本+封装成本+掩膜成本)/ 最终成品率

对上述名称做一个简单的解释,方便普通群众理解,懂行的可以跳过。

从二氧化硅到市场上出售的芯片,要经过制取工业硅、制取电子硅、再进行切割打磨制取晶圆。晶圆是制造芯片的原材料,晶片成本可以理解为每一片芯片所用的材料(硅片)的成本。

一般情况下,特别是产量足够大,而且拥有自主知识产权,以亿为单位量产来计算的话,晶片成本占比最高。不过也有例外,在接下来的封装成本中介绍奇葩的例子。

封装是将基片、内核、散热片堆叠在一起,就形成了大家日常见到的CPU,封装成本就是这个过程所需要的资金。在产量巨大的一般情况下,封装成本一般占硬件成本的5%-25%左右,不过IBM的有些芯片封装成本占总成本一半左右,据说最高的曾达到过70%.

测试可以鉴别出每一颗处理器的关键特性,比如最高频率、功耗、发热量等,并决定处理器的等级,比如将一堆芯片分门别类为:I5 4460、I5 4590、I5 4690、I5 4690K等,之后Intel就可以根据不同的等级,开出不同的售价。不过,如果芯片产量足够大的话,测试成本可以忽略不计。

掩膜成本就是采用不同的制程工艺所需要的成本,像40/28nm的工艺已经非常成熟,成本也低——40nm低功耗工艺的掩膜成本为200万美元;28nm SOI工艺为400万美元;28nm HKMG成本为600万美元。

不过,在先进的制程工艺问世之初,耗费则颇为不菲——在2014年刚出现14nm制程时,其掩膜成本为3亿美元(随着时间的推移和台积电、三星掌握14/16nm制程,现在的价格应该不会这么贵);而Intel正在研发的10nm制程。根据Intel官方估算,掩膜成本至少需要10亿美元。

不过如果芯片以亿为单位量产的话(貌似苹果每年手机+平板的出货量上亿),即便掩膜成本高达10亿美元,分摊到每一片芯片上,其成本也就10美元。而这从另一方面折射出为何像苹果这样的巨头采用台积电、三星最先进,也是最贵的制程工艺,依旧能赚大钱,这就是为什么IC设计具有赢者通吃的特性。

像代工厂要进行的光刻、蚀刻、离子注入、金属沉积、金属层、互连、晶圆测试与切割、核心封装、等级测试等步骤需要的成本,以及光刻机、刻蚀机、减薄机、划片机、装片机、引线键合机、倒装机等制造设备折旧成本都被算进测试成本、封装成本、掩膜成本中,就没有必要另行计算了。

晶片的成本

由于在将晶圆加工、切割成晶片的时候,并不是能保证100%利用率的,因而存在一个成品率的问题,所以晶片的成本用公式表示就是:

晶片的成本=晶圆的成本/(每片晶圆的晶片数*晶片成品率)

由于晶圆是圆形的,而晶片是矩形的,必然导致一些边角料会被浪费掉,所以每个晶圆能够切割出的晶片数就不能简单的用晶圆的面积除以晶片的面积,而是要采用以下公式:

每个晶圆的晶片数=(晶圆的面积/晶片的面积)-(晶圆的周长/(2*晶片面积)的开方数)

晶片的成品率和工艺复杂度、单位面积的缺陷数息息相关,晶片的成品率用公司表达为:

晶片的成品率=(1+B*晶片成本/A)的(-A次方)

A是工艺复杂度,比如某采用40nm低功耗工艺的自主CPU-X的复杂度为2~3之间;

B是单位面积的缺陷数,采用40nm制程的自主CPU-X的单位面积的缺陷数值为0.4~0.6之间。

假设自主CPU-X的长约为15.8mm,宽约为12.8mm,(长宽比为37:30,控制一个四核芯片的长宽比在这个比例可不容易)面积约为200平方毫米(为方便计算把零头去掉了)。

一个12寸的晶圆有7万平方毫米左右,于是一个晶圆可以放299个自主CPU-X,晶片成品率的公式中,将a=3,b=0.5带入进行计算,晶片成品率为49%,也就是说一个12寸晶圆可以搞出146个好芯片,而一片十二寸晶圆的价格为4000美元,分摊到每一片晶片上,成本为28美元。

芯片硬件成本计算

封装和测试的成本这个没有具体的公式,只是测试的价格大致和针脚数的二次方成正比,封装的成本大致和针脚乘功耗的三次方成正比。如果CPU-X采用40nm低功耗工艺的自主芯片,其测试成本约为2美元,封装成本约为6美元。

因40nm低功耗工艺掩膜成本为200万美元,如果该自主CPU-X的销量达到10万片,则掩膜成本为20美元,将测试成本=2美元,封装成本=6美元,晶片成本=28美元代入公式,则芯片硬件成本=(20+2+6)/0.49+28=85美元

自主CPU-X的硬件成本为85美元。

如果自主CPU-Y采用28nm SOI工艺,芯片面积估算为140平方毫米,则可以切割出495个CPU,由于28nm和40nm工艺一样,都属于非常成熟的技术,切割成本的影响微乎其微,因此晶圆价格可以依旧以4000万美元计算,晶片成品率同样以49%的来计算,一个12寸晶圆可以切割出242片晶片,每一片晶片的成本为16美元。

如果自主CPU-X产量为10万,则掩膜成本为40美元,按照封装测试约占芯片总成本的20%、晶片成品率为49%来计算,芯片的硬件成本为122美元。

如果该自主芯片产量为100万,则掩膜成本为4美元,按照封装测试约占芯片总成本的20%来,最终良品率为49%计算,芯片的硬件成本为30美元。

如果该自主芯片产量为1000万,则掩膜成本为0.4美元,照封装测试约占芯片总成本的20%来,最终良品率为49%计算,芯片的硬件成本21美元。

显而易见,在相同的产量下,使用更先进的制程工艺会使芯片硬件成本有所增加,但只要产量足够大,原本高昂的成本就可以被巨大的数量平摊,芯片的成本就可以大幅降低。

芯片的定价

硬件成本比较好明确,但设计成本就比较复杂了。这当中既包括工程师的工资、EDA等开发工具的费用、设备费用、场地费用等等。

另外,还有一大块是IP费用——如果是自主CPU到还好(某自主微结构可以做的不含第三方IP),如果是ARM阵营IC设计公司,需要大量外购IP,这些IP价格昂贵,因此不太好将国内外各家IC设计公司在设计上的成本具体统一量化。

按国际通用的低盈利芯片设计公司的定价策略8:20定价法,也就是硬件成本为8的情况下,定价为20,自主CPU-X在产量为10万片的情况下售价为212美元。别觉得这个定价高,其实已经很低了,Intel一般定价策略为8:35,AMD历史上曾达到过8:50.

在产量为10万片的情况下,自主CPU-Y也采用8:20定价法,其售价为305美元;

在产量为100万的情况下,自主CPU-Y也采用8:20定价法,其售价为75美元;

在产量为1000万的情况下,自主CPU-Y也采用8:20定价法,其售价为52.5美元。

由此可见,要降低CPU的成本/售价,产量至关重要,而这也是Intel、苹果能采用相对而昂贵的制程工艺,又能攫取超额利润的关键。

PS:本文参考自作者铁流