电子工程师出路在哪里?过来人分享

demi 在 提交

demi 在 提交

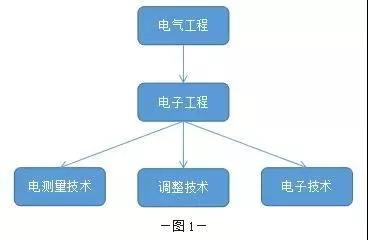

要想了解电子工程专业用得比较多的软件有哪些,首先我们得了解一下电子工程专业相关的一些技术与行业应用分类。电子工程又称“弱电技术”或“信息技术”,其大致分类及起源学科如图1。

电子工程的应用形式涵盖了电动设备以及运用了控制技术、测量技术、调整技术、计算机技术,直至信息技术的各种电动开关。电子工程的主要研究领域为电路与系统、通信、电磁场与微波技术以及数字信号处理等。

电子工程相关的职业一般分为硬件工程师和软件工程师。而电子工程师是一个对从事集成电路、电子电气设备等相关产品生产、研发工作的技术人员的统称。

硬件与软件是不可分离的,硬件需要软件来执行其程序实现具体功能。软件需要硬件做载体,它们之间是一个相辅相承的关系。

软件工程师:

精通电路知识模拟电路,数字电路,会分析电路图,设计电路图,制作PCB,了解各类电子元器件的原理,用途,型号,精通单片机开发技术,会使用编程语言(汇编语言、C语言),能很熟练的用电脑作为辅助设计工具进行工作,能得心应手的使用常用的设计软件。会分析电路故障,对产品进行调试、检测。

硬件工程师:

主要要了解电路方面的知识,知道常用电子元器件的作用,原理,会使用电子测量工具,会使用电子生产工具,还要会装配,测试,生产工艺,维修,等等,是技术与手动操作的结合。

今天我们就来给大家介绍一下目前被电子工程师用得最多,也是功能比较强大的17款软件工具

Altium Designer (简称AD)

Altium designer是一款一体化的电子产品开发系统软件。这套软件通过把原理图设计、电路仿真、PCB绘制编辑、拓扑逻辑自动布线、信号完整性分析和设计输出等技术的完美融合,为设计者提供了全新的设计解决方案,使设计者可以轻松进行设计,熟练使用这一软件使电路设计的质量和效率大大提高。

目前,这个软件的市场定位主要是一些简单的板子,相对是较简单的偏低端的产品设计。一般都是画2层 4层为主。这个软件,在内地城市使用的占有率很高。很多读电子或者机电相关专业的学生在学校里面就有教这个,或者有要求去学这个,主要用于画简单的板子。

PADS

PADS的前身是 POWER PCB ,这个软件界面菜单很少,易上手。特别是消费类电子产品市场占有率非常高,早期都可以说在消费类产品里面差不多是垄断的地位,比如从早期的 VCD,DVD,MP3 ,MP4,U盘,液晶电视,到现在的平板电脑,行车记录仪,车载电子产品,导航仪,数字机顶盒,安卓智能电视盒、手机等都是绝对的市场占有率。在整个消费类电子产品里面,PADS几乎占了绝对的优势。目前在沿海发达城市里面,PADS还是占主流市场,特别是深圳大部分公司还是用PADS ,其次是allegro 。

Cadence allegro

Cadence Allegro是Cadence推出的先进PCB设计布线工具。Allegro提供了良好且交互的工作接口和强大完善的功能,和它前端产品Capture的结合,为当前高速、高密度、多层的复杂PCB设计布线提供了最完美解决方案。

Cadence allegro不容易上手,一般只有大公司用,特别是做电脑主板的公司用,因为这个软件功能强大,画大型板子有优势。如电脑主板,大型工控板,服务器主板,等大型板子,它的效率和优势非常明显。所以它的市场目前主要还是在电脑主板,大型工控板,服务器主板,等这些大型板子上,以及现在一些平板电脑,手机板也会有少量公司用。

Solidworks

可能有人说这就是一个普通的3D软件,怎么会用在电子工程领域呢?那我来解释一下,之前我在深圳是做治具的,也称夹具。这是一个偏硬件的行业。

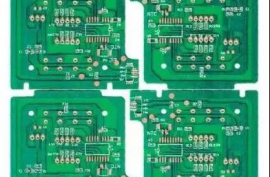

简要介绍一下其整个制造流程,分析工程师把客户的文件资料(通常是PCB资料)用Tebo软件分析出来,然后给结构工程师设计治具结构,然后将需要加工的零部件用JD加工出来,然后进行装配。治具是用于PCB(印刷电路板)测试的工具。这是PCB制造的一个下游行业。但却在保证PCB出厂质量这方面起着不可或缺的而作用。

Matlab

Matlab也是值得接触的软件。Matlab在分析数据、开发算法以及创建模型方面都非常好用。

LabVIEW

LabVIEW是专为测试、测量和控制应用而设计的系统工程软件,可快速访问硬件和数据信息。

Keil

Keil提供了包括C编译器、宏汇编、链接器、库管理和一个功能强大的仿真调试器等在内的完整开发方案,通过一个集成开发环境(μVision)将这些部分组合在一起。

Visual c++

Visual c++是一款集成开发环境(IDE)。它具有开发和调试 C ++代码的工具。

Multisim

Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。

工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。Multisim提炼了SPICE仿真的复杂内容,这样工程师无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。通过Multisim和虚拟仪器技术,PCB设计工程师和电子学教育工作者可以完成从理论到原理图捕获与仿真再到原型设计和测试这样一个完整的综合设计流程。

TestStand

TestStand也是美国国家仪器公司(NI)自主开发研究的一款软件平台。NI TestStand是一款可立即执行的测试管理软件,它可以帮助用户更快地开发自动测试和验证系统。NI TestStand可用于开发、执行和部署测试系统软件。此外,用户还可使用任何编程语言编写的测试代码模块开发测试序列。测试序列可以指定执行流、生成测试报告、进行数据库记录以及连接其他公司系统。最后,用户可借助易用的操作界面,在生产中部署测试系统。

Switch Executive

Switch Executive是一款开关管理与路由应用软件,能够快速加速开发过程,简化对复杂开关系统的维护。Switch Executive提供交互式配置和自动路由功能,使开关路由系统的设计更加容易。

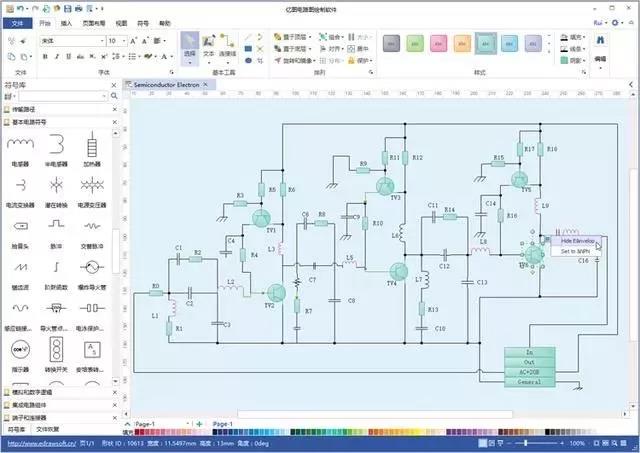

亿图电路图绘制

亿图电路图绘制软件是一款适合新手的入门级电路图设计软件,软件界面简单,包含丰富的图表符号,中文界面,以及各类图表模板。版本定期更新,不用担心无法绘制新型元件。适合专业的电子工程师用于电路图的设计。

Proteus

Proteus软件是英国Lab Center Electronics公司出版的EDA工具软件。设计套件结合了易用和强大的功能集,可实现专业PCB的快速设计,测试和布局。虽然目前国内推广刚起步,但已受到单片机爱好者、从事单片机教学的教师、致力于单片机开发应用的科技工作者的青睐。

ElectronicWorkbench

ElectronicWorkbench是一款电子电路仿真软件,可以进行各种电路工作演示,模拟各种电子电路,缩放显示的波形。ElectronicWorkbench是一款经典小巧,好用的模拟数字电路仿真软件。

LTspice 电路仿真软件

LTspiceIV 是一款高性能Spice III 仿真器、电路图捕获和波形观测器,并为简化开关稳压器的仿真提供了改进和模型。在电路图仿真过程中,其自带的模型往往不能满足需求,而大的芯片供应商都会提供免费的SPICE模型或者PSpice模型供下载,LTspice可以把这些模型导入LTSPICE中进行仿真。LTspice电路图仿真软件在欧洲,美国和澳大利亚,中国广为流传。

OrCAD

OrCAD是一款专业PCB设计,电路板布局和布线的工具。可以帮助更快地生产可制造的电路板设计。Cadence OrCAD产品以其直观的操作界面以及强大的功能而深受广大电子工程师们的喜爱。是世界上使用最广泛的EDA软件。

Tebo

这是一款同时具有CAD和GERBER输入接口的ICT、ATE治具辅助制作软件。能够处理各种GERBER以及埋盲孔、正负片数据。同时具有多种CAD接口,处理数据省时省力,是制作高精密、复杂ICT、ATE测试治具的最佳选择之一。

总的来说,电子工程的水还是比较深的,要想在电子工程有所建树还是需要扎实的功底。希望笔者的整理对大家的学习之路会有帮助!

来源:电子工程专辑

demi 在 提交