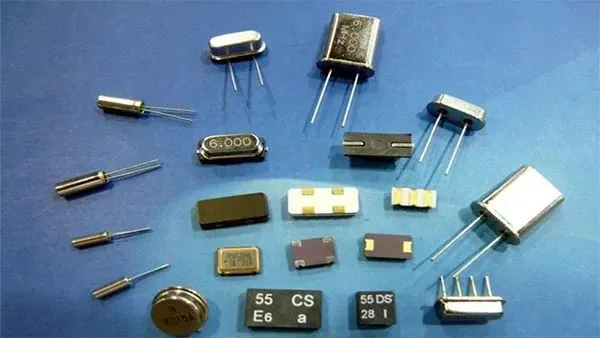

一、为什么51单片机爱用11.0592MHZ晶振?

其一:因为它能够准确地划分成时钟频率,与UART(通用异步接收器/发送器)量常见的波特率相关。特别是较高的波特率(19600,19200),不管多么古怪的值,这些晶振都是准确,常被使用的。

其二:用11.0592晶振的原因是51单片机的定时器导致的。用51单片机的定时器做波特率发生器时,如果用11.0592Mhz的晶振,根据公式算下来需要定时器设置的值都是整数;如果用12Mhz晶振,则波特率都是有偏差的,比如9600,用定时器取0XFD,实际波特率10000,一般波特率偏差在4%左右都是可以的,所以也还能用STC90C516 晶振12M 波特率9600,倍数时误差率6.99%,不倍数时误差率8.51%,数据肯定会出错。这也就是串口通信时大家喜欢用11.0592MHz晶振的原因,在波特率倍速时,最高可达到57600,误差率0.00%。用12MHz,最高也就4800,而且有0.16%误差率,但在允许范围,所以没多大影响。

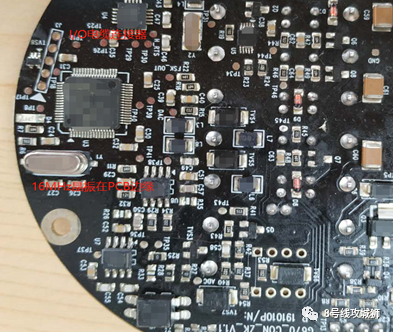

二、在设计51单片机系统PCB时,晶振为何被要求紧挨着单片机?

原因如下:晶振是通过电激励来产生固定频率的机械振动,而振动又会产生电流反馈给电路,电路接到反馈后进行信号放大,再次用放大的电信号来激励晶振机械振动,晶振再将振动产生的电流反馈给电路,如此这般。当电路中的激励电信号和晶振的标称频率相同时,电路就能输出信号强大,频率稳定的正弦波。整形电路再将正弦波变成方波送到数字电路中供其使用。

问题在于晶振的输出能力有限,它仅仅输出以毫瓦为单位的电能量。在 IC(集成电路) 内部,通过放大器将这个信号放大几百倍甚至上千倍才能正常使用。

晶振和 IC 间一般是通过铜走线相连的,这根走线可以看成一段导线或数段导线,导线在切割磁力线的时候会产生电流,导线越长,产生的电流越强。现实中,磁力线不常见, 电磁波却到处都是,例如:无线广播发射、电视塔发射、手机通讯等等。晶振和IC之间的连线就变成了接收天线,它越长,接收的信号就越强,产生的电能量就越强,直到接收到的电信号强度超过或接近晶振产生的信号强度时,IC内的放大电路输出的将不再是固定频率的方波了,而是乱七八糟的信 号,导致数字电路无法同步工作而出错。

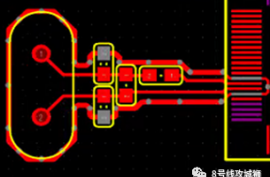

所以,画PCB(电路板)的时候,晶振离它的放大电路(IC管脚)越近越好。

三、单片机电路晶振不起振原因分析

遇到单片机晶振不起振是常见现象,那么引起晶振不起振的原因有哪些呢?

① PCB板布线错误;

②单片机质量有问题;

③ 晶振质量有问题;

④负载电容或匹配电容与晶振不匹配或者电容质量有问题;

⑤PCB板受潮,导致阻抗失配而不能起振;

⑥ 晶振电路的走线过长;

⑦晶振两脚之间有走线;⑧外围电路的影响。

解决方案,建议按如下方法逐个排除故障:

① 排除电路错误的可能性,因此可以用相应型号单片机的推荐电路进行比较。

② 排除外围元件不良的可能性,因为外围零件无非为电阻,电容,很容易鉴别是否为良品。

③ 排除晶振为停振品的可能性,因为不会只试了一二个晶振。

④试着改换晶体两端的电容,也许晶振就能起振了,电容的大小请参考晶振的使用说明。

⑤在PCB布线时晶振电路的走线应尽量短且尽可能靠近IC,杜绝在晶振两脚间走线。

四、51单片机时钟电路用12MHZ的晶振时那电容的值是怎样得出来的?拿内部时钟电路来说明吧!

其实这两个电容没人能够解释清楚到底怎么选值,因为22pF实在是太小了。这个要说只能说和内部的振荡电路自身特性有关系,搭配使用,用来校正波形,没有人去深究它到底为什么就是这么大的值。

五、单片机晶振电路中两个微调电容不对称会怎样?相差多少会使频率怎样变化?在检测无线鼠标的接受模块时,发现其频率总是慢慢变化(就是一直不松探头的手,发现频率慢慢变小)晶振是新的。

电容不对称也不会引起频率的漂移,说的频率漂移可能是因为晶振的电容的容量很不稳定引起的,可以换了试,换两电容不难,要不就是的晶振的稳定性太差了,或者测量的方法有问题。

六、单片机晶振与速度的疑问,执行一条指令的周期不是由晶振决定的吗。那么比如51单片机和MSP430,给51接高速晶振,430接低速的,是不是51跑的要快?是不是速度单片机速度仅仅与晶振有关,关键是单片机能不能支持那么大的晶振?

每个单片机的速度是受到内部逻辑门电平跳变速度限制的。两个芯片同时使用同样的晶振,比如12M的。因为AVR是RISC指令集,它在同样外部晶振频率下,比51要快。

比如,51最快能接40M,AVR是16M的晶振。

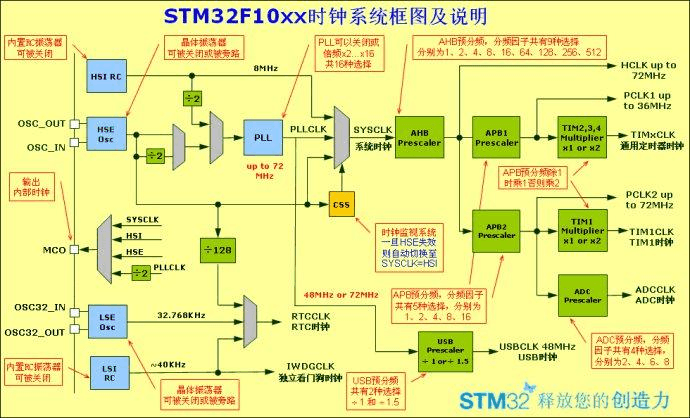

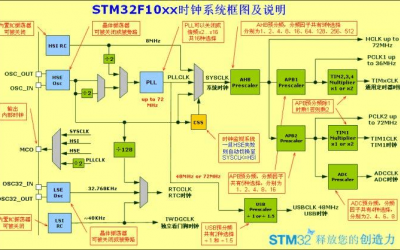

STC89C52大都用12MHz晶振,但由于其12个时钟周期才是一个机器周期,相当于其主频只有1MHz。

MSP430采用RISC精简指令集, 430单片机若采用内部DCO震荡可达21MHz主频。单个时钟周期就可以执行一条指令,相同晶振,速度较51快12倍。

对于一个51,给它用更高的晶振,速度会快些。但是对于高级的单片机就不一样了。高级单片机内部,一般都是有频率控制寄存器的,所以,简单的增加晶振,可能达到单片机的极限,导致跑飞。

七、请问:有什么方法可以确定某一款单片机在某一大小的晶振下是否能正常工作?

晶振选择太高不太合适,具体晶振上限是多少,恐怕测不出来,只能按照人家单片机的要求,一般STC系列单片机上限是35M或40M,stc单凭上写的有,如STC11F16XE 35I-LQFP44G其中35I就是晶振最高35M的工业级芯片。

超过上限会出现什么样的问题,没有测试过,一般晶振选择12M的比较多,如果选择STC 1T指令的,就相当于12*12=144M的晶振。如果用于串口通信,建议选用11.0592M的或22.184M,选择晶振最主要还是参照人家的说明书。

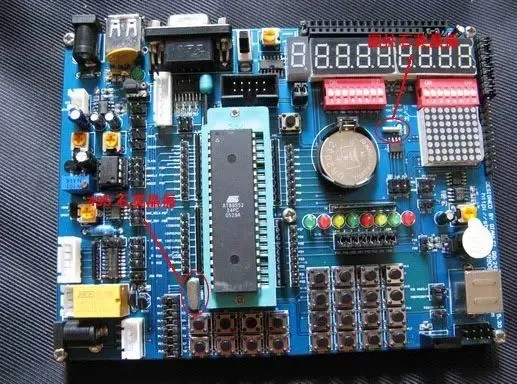

八、4个AT89C51单片机能否用一个12M的晶振使其都正常工作?一个采用内部时钟方式,其余三个用外部方式......那四个都用内部方式可以不(将4个单片机都并联在一个晶振上)?

可以,其中一个正常接晶振,他的XTAL2输出接到另外三个的XTAL1输入上。

九、单片机的运行速度和晶振大小的关系,若单片机的最高工作频率是40M,晶振是否可以选择24M或更高,但不超过40M,这样单片机的运行速度是否大增?长期在此工作频率下对单片机是否有不良影响?单片机对晶振的选择的原则是怎样的?

当然是有影响的,单片机的工作速度越快,功耗也越大,受干扰也会越厉害,总之最高能跑40M的,跑不超过40M的是没有问题的,只是对相关的技术(如PCB的设计元件的选取等)会高去很多。

十、89c51单片机的复位电路中常采用12MHZ的晶振,实际上市场上稍小于12MHZ,为什么呢?

答:需要串口通讯时一般是用11.0582MHZ的,这样波特率才好算。用12MHZ的工作周期就容易计算。

十一、单片机晶振上电不起振,但是手碰一下晶振就起振了,为什么?怎么判断单片机晶振是否起振呀?

看看晶振配的电容焊了没有,值有没有错误?

最简单是用示波器,另外可以看一下电源是否正常。

十二、怎样判断单片机外部晶振有没有起振?STC89C52单片机本来是好好的后来不行了,换了个晶振就好了。但是过了几个小时后又不行了,是怎么回事。还有就是怎样判断晶振是否起振?

①先换一块单片机试试,问题还在则排除单片机;

②可能是虚焊造成的,这点要注意;

③用STC89C52也碰到过类似的问题,换了块晶振就OK 了,好像STC起振不橡AT89S52那么顺。其实对于STC89C52可以直接看30脚(ALE),接个灯,起振一下子就能看出来了。

十三、51单片机晶振上接的电容大小该如何选择?是晶振越大,电容值也要大一些吗,一般常用多大的。有人说常用的从15-33pf,具体如何选择效果最好?比如分别用一个6M和12M的晶振,用多大电容更合适?

15-33pf都可以,一般用的是15P和30P 晶振,大小影响不大。常用的4M和12M以及11.0592M和20M 24M都用的30P,单片机内部有相应的整形电路,不必担心。

十四、没有程序的空白单片机,外部晶振能起振么?

没有内部晶振的单片机,外部晶振可以起振,如传统类MS51系列单片机有内部晶振的单片机,外部晶振不会起振,需要对外部晶振进行配置后才会起振,如果不对外部晶振进行配置仍使用内部晶振,如silicon lab系列C8051F020单片机。

十五、为什么at89c52 P1.0输出2.5v电压,单片机好像未工作,晶振波形是不规则的正弦波可不可以?线路板没有达到预想效果,发光二极管一直亮,感觉还是单片机的问题,P1.0输出2.5v电压,看门狗用的X5045,怎么回事?

将看门狗拿掉,暂时做成最小系统,既只有电源、8952、晶振和两只30P左右的电容。

①将P1.0口置1,测试该口的电压是否在2.5V以上;

②将P1.0口置0,测试改口电压是否约为0V。

是的话就是OK的,否则就要看看电源电压、晶振、8952了。电源电压是5+、-0.25V,且纹波一定要小。

十六、制作max232下载单片机,工作电压都正常,要外加晶振嘛?

当然要加,如果没有外加晶振,那么单片机的时钟电路就没有了,导致单片机串口就不能进行数据传输了,最终这个下载器具就不能下载程序了。

十七、若89c52单片机使用外接晶振,应如何设置?

晶振的两个管脚各接一个20~30pf的电容后分别接入单片机的XTAL1和XTAL2,两个电容的另一端并接后接地即可,不再需要任何设置。

十八、晶振的原理,如何产生正弦信号的,详细一点,从电路方面分析?

晶体可以等效为一个电感,与里面的电容形成振荡回路,能量从电感慢慢到电容,再从电容慢慢到电感,周而复始形成振荡。正半周是电容的充放电过程,负半周是电感的充放电过程。

十九、现在要用52单片机做一个交通灯电路。要求是红灯,绿灯30s,黄灯3s。循环变化。那么外界晶振怎样选择?单指令周期多少比较合适?图中外接的两个电容的作用是什么?大小多少合适?

如果选择晶振的话,那两个电容值可以选择:30加减10PF左右的(频率在0~33MHZ之间);

如果选择陶瓷晶振的话,电容值可以选择:40加减10PF左右的(频率在1.2~12MHZ)振荡器应尽量靠近电容。指令周期是可以算的,这个是有公式的。

二十、89c52单片机 晶振频率才12兆,太小了,怎样能改大晶振频率?

外接18.432或者24MHz的晶振。或者换4T的W77E58单片机,这样相当于把工作频率提高3倍。或者换1T的DS89C4XX单片机,这相当于把工作频率提高8倍。用1T的STC12C5A60S2单片机也有这样的效果。

二十一、单片机不能正常工作,晶振问题?如何去检查晶振正常还是不正常?另外看到说晶振跟两个小电容要离得很近,几乎都没剪引脚(就是买回来多长就多长)就插上去了,这个也有关系吗?

用万用表测量单片机连接晶振的两个引脚,正常起振的状态下电压大概比供电电压的1/2略低一些,如果其中一个或全部引脚为电源电压或零就表明没起振。那个引脚长些一般不会有什么影响,相比之下接地更关键些,两个谐振电容接地端到单片机的电源地要尽量近些。

二十二、22pf或30pf电容到底有什么作用?

刚学单片机的学长告诉我单片机的晶振电路中就是用22pf或30pf的电容就行,听人劝吃饱饭吧,照着焊电路一切ok,从没想过为什么,知其所以然而不知其为什么所以然,真是悲哀。后来,我才懂得反思,调整,我对自己持有怎么的学习态度和应该如何付诸于行动有了新的理解,这远比单纯的交给我一些知识要好很多。

让我们一起来看看到底晶振电路中为什么用22pf或30pf的电容而不用别的了。

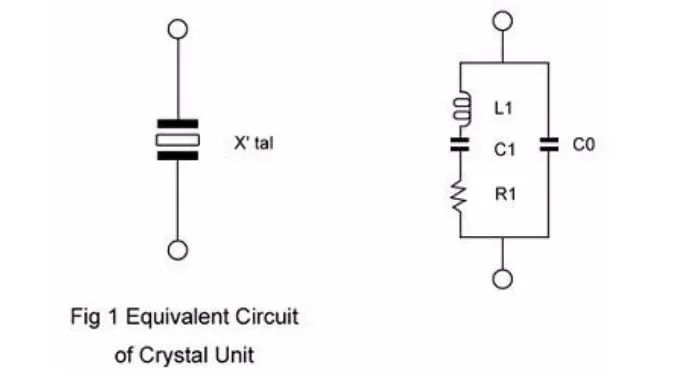

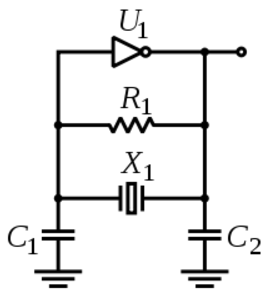

其实单片机和其他一些IC的振荡电路的真名叫“三点式电容振荡电路”,如下图

![“”]()

Y1是晶体,相当于三点式里面的电感,C1和C2就是电容,5404非门和R1实现一个NPN的三极管,接下来分析一下这个电路。

5404必需要一个电阻,不然它处于饱和截止区,而不是放大区,R1相当于三极管的偏置作用,让5404处于放大区域,那么5404就是一个反相器,这个就实现了NPN三极管的作用,NPN三极管在共发射极接法时也是一个反相器。

大家知道一个正弦振荡电路要振荡的条件是,系统放大倍数大于1,这个容易实现,相位满足360度,与晶振振荡频率相同的很小的振荡就被放大了。接下来主要讲解这个相位问题:

5404因为是反相器,也就是说实现了180°移相,那么就需要C1,C2和Y1实现180°移相就可以,恰好,当C1,C2,Y1形成谐振时,能够实现180移相,这个大家可以解方程等,把Y1当作一个电感来做。也可以用电容电感的特性,比如电容电压落后电流90°,电感电压超前电流90°来分析,都是可以的。当C1增大时,C2端的振幅增强,当C2降低时,振幅也增强。有些时候C1,C2不焊也能起振,这个不是说没有C1,C2,而是因为芯片引脚的分布电容引起的,因为本来这个C1,C2就不需要很大,所以这一点很重要。接下来分析这两个电容对振荡稳定性的影响。

因为5404的电压反馈是靠C2的,假设C2过大,反馈电压过低,这个也是不稳定,假设C2过小,反馈电压过高,储存能量过少,容易受外界干扰,也会辐射影响外界。C1的作用对C2恰好相反。因为我们布板的时候,假设双面板,比较厚的,那么分布电容的影响不是很大,假设在高密度多层板时,就需要考虑分布电容。

有些用于工控的项目,建议不要用无源晶振的方法来起振,而是直接接有源晶振。也是主要由于无源晶振需要起振的原因,而工控项目要求稳定性要好,所以会直接用有源晶振。在有频率越高的频率的晶振,稳定度不高,所以在速度要求不高的情况下会使用频率较低的晶振。

二十三、单片机晶振电路中两个微调电容不对称会怎样?相差多少会使频率怎样变化?我在检测无线鼠标的接受模块时,发现其频率总是慢慢变化(就是一直不松探头的手,发现频率慢慢变小)晶振是新的。

答:电容不对称也不会引起频率的漂移,你说的频率漂移可能是因为晶振的电容的容量很不稳定引起的,你可以换了试,换两电容不难,要不就是你的晶振的稳定性太差了,或者你测量的方法有问题。

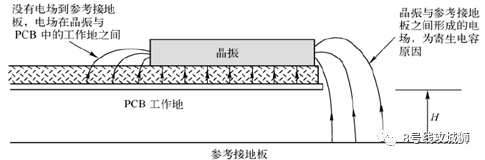

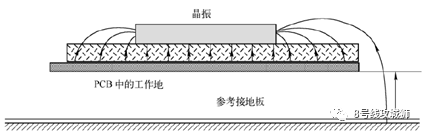

二十四、晶振为何被要求紧挨着IC,单片机晶振不起振?

答:原因如下:

晶振是通过电激励来产生固定频率的机械振动,而振动又会产生电流反馈给电路,电路接到反馈 后进行信号放大,再次用放大的电信号来激励晶振机械振动,晶振再将振动产生的电流反馈给电路,如此这般。当电路中的激励电信号和晶振的标称频率相同时,电 路就能输出信号强大,频率稳定的正弦波。整形电路再将正弦波变成方波送到数字电路中供其使用。

问题在于晶振的输出能力有限,它仅仅输出以毫瓦为单位的电能量。在 IC(集成电路) 内部,通过放大器将这个信号放大几百倍甚至上千倍才能正常使用。

晶振和 IC 间一般是通过铜走线相连的,这根走线可以看成一段导线或数段导线,导线在切割磁力线的时候会产生电流,导线越长,产生的电流越强。

现实中,磁力线不常见,电磁波却到处都是,例如:无线广播发射、电视塔发射、手机通讯等等。晶振和IC之间的连线就变成了接收天线,它越长,接收的信号就 越强,产生的电能量就越强,直到接收到的电信号强度超过或接近晶振产生的信号强度时,IC内的放大电路输出的将不再是固定频率的方波了,而是乱七八糟的信 号,导致数字电路无法同步工作而出错。

所以,画PCB(电路板)的时候,晶振离它的放大电路(IC管脚)越近越好。

二十五、4个AT89C51单片机能否用一个12M的晶振使其都正常工作?一个采用内部时钟方式,其余三个用外部方式...那我四个都用内部方式可以不(将4个单片机都并联在一个晶振上)?

答:可以,其中一个正常接晶振,他的XTAL2输出接到另外三个的XTAL1输入上。

二十六、AT89C51单片机4兆的晶振能不能启动?

答:当然可以,看看datasheet吧,我估计1M的都可以,还有的单片机如2051可能还能低,台系日系有的可以到32.768kHz。

二十七、怎样判断单片机外部晶振有没有起振?我的STC89C52单片机本来是好好的后来不行了,我换了个晶振就好了。但是过了几个小时后又不行了,是怎么回事。还有就是怎样判断晶振是否起振?

答: 第一点:先换一块单片机试试,问题还在则排除单片机;

第二点:可能是虚焊造成的,这点要注意;

第三点:我用STC89C52也碰到过类似的问题,换了块晶振就OK了,好像STC起振不橡AT89S52那么顺。

其实对于STC89C52可以直接看30脚(ALE),接个灯,起振一下子就能看出来了。

二十八、我用msp430的单片机,可是外部的两个晶振总是无法起振,没用。请问是什么原因?线路连接是对的,32768HZ没有接外接电容。8M的晶振接56PF的电容。

答:32.768K的晶振接两个30P的电容试试,还有8M的晶振的电容也换成30P的。

二十九、MSP430单片机8MHz的晶振,计数器TAR增加一次 需要多少时间?

答:MSP430单片机的晶振频率可以自己设置的,是使用外部晶振还是内部振荡器做始终源,还有MCLK,SMCLK,ACLK的选择,分不分频等都有影响 我现在有点忘了,不过你可以看看文档,计数器是使用mclk,smclk,ACLK的哪一个,在判断是否分频设置,一般在1Mhz TAR加一次是1us,那么8M是1/8us自己算吧。

三十、如果MSP430单片机不初始化晶振,那么单片机用什么作为时钟?DCO的频率大概是多少呢?

答:内部DCO,不同系列的DCO默认频率不同,要参看手册。4系列的好像是1M。

三十一、dspic30f6014单片机能够烧写程序,却不能运行。晶振没有起振(换过了也没用),复位电压测量为5v,电源正常,(是成熟产品,只是偶尔会出现这种情况)

答:

01、重新检讨振荡电路所用零件(晶振与电容)及晶振附近的pcb布局

02、检查配置位是否正确

03、还可找 FAE 谘询

三十二、单片机测试晶振电压时会对工作状态有影响吗?

我的51单片机从P2口连了两个发光二极管,正常时是只有一个亮。我插上电源后,结果两个都亮了。于是我就测量晶振电压,但是我黑表笔接地,红表笔一碰晶振引脚时,两个发光二极管中,就有一个会熄灭,一放开就两个都亮。

每次刚插电源的时候,两个晶振引脚分别时1.9V,1.5v,但是稍微过了一会儿,两个引脚就分别成了5.4V和0.02V了。

答:会有一点影响,对频率会有影响,严重的会导致晶振停振。因为你万用表一加上去相当于在振荡电路上又并上或串上了分部电容电阻电感等,就影响到了原来电路的状态。

三十三、静态工作点对晶振振荡有什么影响?

答: 具有高Q值的晶振对放大器的选择并不敏感,但在过驱动时很容易产生频率漂移(甚至可能损坏)。影响振荡器工作的环境因素有:电磁干扰(EMI)、机械震动与冲击。

三十四、我用的是外置4M晶振加两个30pf瓷片电容,用示波器测频率正常,但峰峰值有的板子是6V左右,有的是3V左右,板子功能正常但我怕电压低的不稳定。

答: 没关系的,峰峰值不同是电容和晶振的参数离散导致的。只要正常工作就可以,单片机里面都有放大处理的,它们都是放大展成方波来使用的。峰峰值多高都没用。

你那电压高的倒应该看看,pic一般工作电压是5V,怎么振荡器会进来这么高电压?

我一般都是在CPU晶振输入端串联一个电阻使用的。

三十五、pic单片机 AD采样程序 有源晶振应该如何选择?

如果使用片内振荡器,是不是必须要外接谐振器?我如果外接有源晶振,选用那种频率较好?我听说4MHz的并不理想。外接20MHz的可以吗?这个是怎样选择的啊。

答:用片内振荡器不需要外接谐振器。

如果你的单片机只做AD采集转换,那就不需要太高的频率,内部4Mhz振荡器即可。

但如果还要做其他对时序要求较严的工作比如说总线通信,那就要考虑使用外部振荡器,因为内部振荡器的误差太大(即使校准了还有1%的误差) ,而用多大的晶振要看工作要求,频率越高单片机功耗越大。但只做AD的话,4M够了。

三十六、大家好。我想问个pic单片机的问题:晶振频率不一样。编译器自己带的库延时函数延时一样吗?比如晶振20MHZ delayus(1)和5MHZ delayus(1)是同是1us吗?

答: 应该一样。因为频率不一样,编译时候你的设置不一样,编译时候自然计算需要的倍数,参数就不一样了。但可能因为频率除不尽的缘故,有一点点差异。

三十七、单片机外接24M的晶振,1ms的基准延时函数用C语言怎么写?

答:

定时器T0 工作方式1 晶振频率24MHz

定时器最大定时时间(us):32768

定时器最小定时时间(us):0.5

【1ms精确定时C51代码】

void T0_init(void) //定时器初始化

{

TMOD |= 0x01;

TH0 = 0xf8; //设置定时器计数初值,定时1000us

TL0 = 0x33;

IE |= 0x82; //打开总中断

TR0 = 1; //启动定时器

}

void T0_intservice(void) interrupt 1 //定时器中断服务

{

TH0 = 0xf8; //重装载定时器计数初值

TL0 = 0x33;

//这里可以插入其他处理程序,不会影响定时器工作

}

三十八、单片机24M晶振可以测量20MHZ的信号吗?

答 :要看用什么单片机了。有些单片机执行一条指令需要两个机器周期以上的。那肯定测量不到20MHZ的信号。

三十九、用单片机的晶振电路产生信号和555计时器产生信号哪个更好?

答:一般来说,晶振的稳定性好于RC震荡器。

四十、11.0952的晶振和单片机哪些引脚连接能起作用?电源和18B20应该和单片机的哪些引脚相连呢?RT,要把单片机从实验板上引出来,应该怎么连接?1602LCD的液晶该怎么和单片机相连呢?每次从仿真上连出来都是只有背光和黑点,但是不显示已经烧录的程序。

答:晶振接单片机x1(或者叫XTAL1)和x2(或者叫XTAL2)引脚。

电源接单片机的VCC和GND。

18b20电源脚接电源上,中间的数据线可以单片机的任意io口。具体控制是靠程序完成的。

1602的数据线接单片机io(比如51单片机的P1口),其它的控制线rw,reset,cs等可以接单片机的任意io口。

烧录了程序不能运行,而程序是正确的话,你得看程序怎么定义这些引脚,根据程序定义连接单片机的位置。

四十一、89c52单片机如果不接晶振会有什么后果?

答:单片机不工作了 程序无法烧入等等。

四十二、单片机工作频率的问题,晶振到底怎么选择?

答:

1、最基本的单片机,其机器工作频率为:晶振频率÷12

2、有的单片机(高级一些的)机器工作频率为:晶振频率÷2(或者6等等)

3、以汇编语言为例,单片机执行一条指令需要的时间为1~2个机器周期(机器周期 = 1÷机器工作频率)

4、举例:

一普通单片机晶振12MHz,其机器工作频率为 12MHz÷12 = 1MHz

其机器周期 = 1÷1MHz = 0.000001秒(也就是10的负6次方)

“MOV”指令需要一个机器周期来完成,也就是说执行这条指令需要耗费10的负6次方秒,这么长的时间。

四十三、我给51单片机12M晶振接2200pF电容会怎么样?电路图里貌似是22pF的,但是我没有22pF的...接2200pF会不会不正常工作?

答:不可以,晶体会不工作的。15-33p是合理范围。你可以试试看,对单片机不会有损坏。

本文转载自:网络

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。

的环路相移。

的环路相移。