摘要

从延长便携式设备电池寿命,到提高处理效率和响应能力,瑞萨的40纳米MCU技术正在重新定义嵌入式系统的可能性。

Markus Vomfelde

Director

瑞萨以其卓越的40纳米工艺技术彻底改变了微控制器技术的格局,致力于开发新一代微控制器。凭借对高集成度、能效、性能和可扩展性的高度重视,瑞萨的40纳米MCU已成为行业的新标杆。这些MCU利用较小的晶体管尺寸和优化的电路设计,为各种应用提供了无与伦比的能力。从延长便携式设备电池寿命,到提高处理效率和响应能力,瑞萨的40纳米MCU技术正在重新定义嵌入式系统的可能性。让我们深入探讨这些MCU所具有的变革性特质和优势,使其位列创新前沿。

探索瑞萨40纳米制程技术的主要特性和亮点

瑞萨的微控制器单元(MCU)工艺技术一直在迅猛发展,以满足半导体行业的需求。高性能和高集成度的MCU犹如敏捷的大师在演奏先进技术的交响乐,将各行各业的生产力和创新推向新的高度。借助我们闪电般的执行速度、无缝连接和处理大量数据的能力,这些MCU已成为现代工业系统的支柱,实现实时控制、智能自动化和数据驱动的决策。瑞萨正在积极缩小工艺节点的尺寸,其中最受欢迎的是40纳米技术。瑞萨早在2013年就率先推出了基于40纳米的MCU,随后不断发展这一技术,以提供高性能和高集成度,以满足各种苛刻的应用需求。瑞萨的40纳米制程技术旨在集成高速连接、高级安全功能以及对人工智能和机器学习等高级功能的支持。

借助40纳米技术的先进工艺,瑞萨的MCU集成了具有更高分辨率、更高采样率和更高线性度的模数转换器(ADC)。此外,分辨率更高的数模转换器(DAC)能够产生高质量的模拟输出信号。通过推动工艺技术的发展,瑞萨不断提升其MCU的性能和功能,为工程师提供满足各种应用所需强大模拟功能的创新设计解决方案。瑞萨MCU工艺技术发展的趋势包括缩小工艺节点、集成高级功能、注重能效和提高处理能力。随着这些趋势的不断发展,瑞萨已做好了准备来满足半导体行业不断变化的需求。

瑞萨的40纳米工艺MCU功能和支持应用

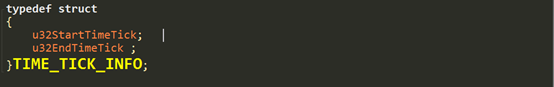

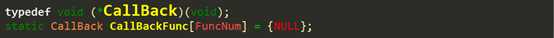

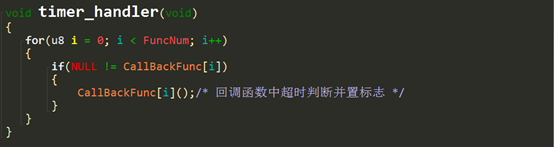

瑞萨的40纳米MCU采用了一种被称为40纳米节点的工艺技术。基于这一技术,瑞萨的MCU提供了领先的功能和终极集成,具体如下表所示。

高端40纳米MCU特性

性能:多核并拥有更高的计算频率

功耗更低:降低50%的功耗

集成:大容量闪存

可靠性:长达20年的数据保留能力

这种工艺技术指的是制造MCU时使用的晶体管和互连的尺寸。瑞萨在其汽车微控制器单元(MCU)中采用了分栅金属-氧化物-氮化硅-氧化物-单晶硅(SG-MONOS)技术,这使得其在行业中脱颖而出并带来了众多的优势。作为拥有30多年的电荷俘获型非易失性存储器(NVM)生产经验的瑞萨,已成为提供卓越功能和可靠性解决方案的领导者。瑞萨利用电荷俘获型非易失性存储器(NVM)技术实现更快的性能,并在其MCU中集成大容量闪存。这项技术能够实现高效的数据存储和检索,从而缩短访问时间并提高系统性能。瑞萨还将大容量闪存集成到其MCU中,减少了对外部存储设备的需求,增强了MCU的功能。

40纳米制程技术的一个突出优势是其世界级的高速随机读取性能,这使得瑞萨成为这方面的行业前沿。快速高效地访问数据的能力在许多应用中至关重要,而瑞萨的40纳米MCU在这方面提供了无与伦比的性能。此外,瑞萨的40纳米制程技术,还提供了最快的闪存访问速度,无需等待的状态,这意味着可以快速读取和写入数据,从而提高系统响应能力并减少延迟。这一优势在实时应用中尤为显著,因为快速数据访问对于无缝操作至关重要。

瑞萨的40纳米工艺技术还采用了基于电荷俘获机制的离散存储节点架构。这种设计确保了高可靠性和可扩展性,使MCU能够承受苛刻的工作条件,并适应不断发展的行业要求。此外,集成氮化薄膜存储(SiN)技术实现了薄型单元设计,使MCU与先进的逻辑工艺兼容。

通过分栅源端热电子注入(SSI)编程的实施,瑞萨的MCU实现了低功率编程操作。这有助于提高能效,降低功耗,并延长便携式设备的电池寿命。为了进一步提高性能和能效,瑞萨采用了低电压字线驱动,并消除了读取访问路径中的高电压。这些优化措施实现了超过400MHz的高速随机读取操作,同时保持较小的区域尺寸。高性能、低功耗和紧凑尺寸的结合使瑞萨的40纳米MCU成为各种应用的理想选择。

瑞萨的40纳米技术为各种工业、消费和汽车应用带来了显著的优势。其中,一些领先优势包括电荷捕获NVM产品、世界一流的高速随机读取性能、最快的闪存访问、高可靠性、可扩展性和优化的电路设计。瑞萨持续推动MCU技术的发展,这些进步使工程师能够为性能、功效和尺寸至关重要的各种行业的设计创新提供高效的解决方案。

瑞萨MCU为当前技术带来的附加值

瑞萨的40纳米工艺技术已经开发出一系列具有先进特性和功能的MCU和MPU。以下是一些采用瑞萨40纳米制程技术的MCU产品示例,以及它们的功能和应用支持介绍:

RX72N系列

这组MCU是为工业自动化和控制应用而设计的。它具有高性能32位RXv3 CPU内核、高达4MB的闪存和高达640KB的随机存储器(RAM)。RX72N系列还支持以太网、CAN和USB通信接口,适合机器人、电机控制和工厂自动化等应用。

有关RX72N产品的更多信息,您可点击下方链接查看:

RX72N

RA6M5系列

RA6M5组MCU专为高性能物联网应用而设计。它具有200MHz Arm® Cortex®-M33 CPU内核、高达2MB的闪存和高达512KB的RAM。RA6M5系列还支持以太网、USB和CAN FD通信接口,以及AES和SHA加密等安全特性。这使得它非常适合所有互联应用以及智能家居、楼宇自动化和远程监控。

有关RA6M5产品的更多信息,您可点击下方链接查看:

RA6M5

RX66T系列

RX66T是瑞萨的微控制器单元(MCU),专为工业自动化系统和机器人领域的高性能电机控制应用而设计。它拥有一个32位RXv3 CPU内核、专用外设、多种存储器选项,以及UART、SPI、I2C和CAN等通信接口。RX66T还包含高级安全功能,如内置自测功能和内存保护单元。它的工作电压范围广泛,通常为2.7V至5.5V,并提供全面的开发生态系统,包括软件开发工具、中间件和库。RX66T MCU非常适用于对精密电机控制要求较高的应用,如工业机器人、电机驱动设备和自动化系统。

有关RX66T产品的更多信息,您可点击下方链接查看:

RX66T

瑞萨先进的40纳米微控制器设备

瑞萨的40纳米制程技术,拥有高集成度、高能效、高性能和可扩展性,彻底改变了微控制器技术的格局。这些先进的MCU为工程师提供了高效的解决方案,包括延长电池寿命,增强处理能力和响应能力。而高速闪存、优化的电路设计和高级安全功能等特性帮您轻松设计出创新产品!毋庸置疑,瑞萨的40纳米MCU树立了行业新标准,让您的设计更有竞争力!不论是工业自动化和控制,还是物联网应用和电机控制,这些MCU将助您实现更高水平的生产力和创新!

瑞萨将持续推动MCU技术的发展,提供满足半导体行业不断发展需求的增值解决方案,欢迎使用我们的产品,期待与您一同开创未来!

来源:瑞萨电子

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理(联系邮箱:cathy@eetrend.com)。