布线(Layout)是pcb设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速pcb设计中是至关重要的。

下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。

蛇形线是Layout中经常使用的一类走线方式。其主要目的就是为了调节延时,满足系统时序设计要求。设计者首先要有这样的认识:蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使用。但实际设计中,为了保证信号有足够的保持时间,或者减小同组信号之间的时间偏移,往往不得不故意进行绕线。

那么,蛇形线对信号传输有什么影响呢?走线时要注意些什么呢?其中最关键的两个参数就是平行耦合长度(Lp)和耦合距离(S),如图1-8-21所示。很明显,信号在蛇形走线上传输时,相互平行的线段之间会发生耦合,呈差模形式,S越小,Lp越大,则耦合程度也越大。可能会导致传输延时减小,以及由于串扰而大大降低信号的质量,其机理可以参考第三章对共模和差模串扰的分析。

下面是给Layout工程师处理蛇形线时的几点建议:

1. 尽量增加平行线段的距离(S),至少大于3H,H指信号走线到参考平面的距离。通俗的说就是绕大弯走线,只要S足够大,就几乎能完全避免相互的耦合效应。

2. 减小耦合长度Lp,当两倍的Lp延时接近或超过信号上升时间时,产生的串扰将达到饱和。

3. 带状线(Strip-Line)或者埋式微带线(EmbeddedMicro-strip)的蛇形线引起的信号传输延时小于微带走线(Micro-strip)。理论上,带状线不会因为差模串扰影响传输速率。

4. 高速以及对时序要求较为严格的信号线,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。

5. 可以经常采用任意角度的蛇形走线,如图1-8-20中的C结构,能有效的减少相互间的耦合。

6. 高速pcb设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。

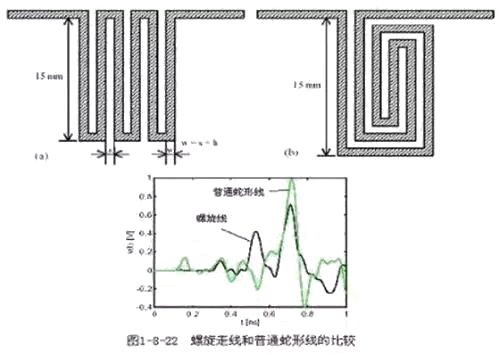

7. 有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

来源:电子技术应用